- •1.1 Пояснити призначення і використання віртуальної машини jvm. Пояснити відмінність іjvm і jvm.

- •1.2Пояснити призначення і роботу регістрів пам’яті віртуальної машини іjvm.

- •1.3 Пояснити призначення контролера мікрокоманд іjvm Міс-1. Намалювати його структурну схему і пояснити призначення кожного його функціонального модуля.

- •1.4 Що таке стек операндів? Яке його призначення де він розміщений і як організований?

- •1.5??????????????????? Вкажіть який максимально допустимі розміри областей пам’яті в іjvm Міс-1: фрейму локальних змінних? а області процедур? а області констант?

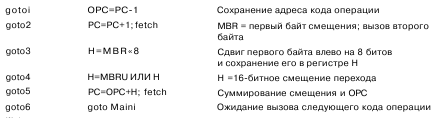

- •1.7 Опишіть інтерпретацію в Міс-1 команди goto

- •1.9 Поясніть як побудована асоціативна кеш-пам’ять?

- •1.10 Опишіть способи адресації віртуальної машини Java

1.7 Опишіть інтерпретацію в Міс-1 команди goto

Мікрокоманда goto2 починає виклик другого байта зсуву, що призводить до ситуації, що на рис. 4.17, г (мікрокоманда goto3). Після того, як перший байт зміщення зсувається вліво на 8 бітів і копіюється в регістр Н, ми переходимо

до мікрокоманд goto4 (див. рис. 4.17, д). Тепер у нас перший байт зсуву, зрушутий вліво, знаходиться в регістрі Н, другий байт зміщення - в регістрі MBR, а основа зміщення - в регістрі ДСБ. У мікрокоманд goto5 шляхом додавання повного

16-бітного зсуву до основі зсуву ми отримуємо нову адресу, який заться в регістр PC. Відзначимо, що в goto4 замість MBR ми використовуємо MBRU, оскільки нам не потрібно знакова розширення другого байта. 16-бітове зсув

будується шляхом логічного додавання (операція АБО) двох половинок. Нако-270 Глава 4. Мікроархітектурний рівень

нець, оскільки програма перед переходом до Mainl вимагає, щоб в MBR був по- щень слід код операції, ми повинні викликати цей код. Останній цикл, goto6, потрібен для того, щоб вчасно помісити дані з пам'яті в регістр MBR.

1.8 Поясніть, як організована кеш-пам’ять в Міс-1 і чому.

Одним з найбільш важливих питань при розробці комп'ютерів було і залишається побудова такої системи пам'яті, яка могла б передавати операнди про-цессора з тією ж швидкістю, з якою він їх обробляє. Швидке зростання швидкості

роботи процесора, на жаль, не супроводжується настільки ж високим зростанням швидкості роботи пам'яті. Щодо процесора пам'ять працює все повільнийнеї і повільніше з кожним десятиліттям. З урахуванням величезної важливості основний пам'яті ця ситуація значно обмежує розвиток систем з високою виробляй- тельностью і спрямовує дослідження таким шляхом, щоб обійти проблему дуже низькою порівняно з процесором швидкості роботи пам'яті. І, відверто гово-

ря, ця ситуація погіршується з кожним роком. Сучасні процесори висувають певні вимоги до системи пам'яті і щодо часу очікування (затримки у доставці операнда), і відносительно пропускної здатності (кількості даних, переданих в одини-

цу часу). На жаль, ці два аспекти системи пам'яті сильно розходяться. Зазвичай зі збільшенням пропускної здатності збільшується час очікування. Наприклад, технології конвеєризації, які використовуються в мікроархітек-турі Mic-З, можна застосувати до системи пам'яті, при цьому запити пам'яті будуть Збільшення продуктивності 295 оброблятися більш раціонально, з перекриттям. Але, на жаль, як і в мік- роархітектуре Mic-З, це призводить до збільшення часу очікування окремих операцій пам'яті. Зі збільшенням швидкості задає генератора стає все складніше забезпечити таку систему пам'яті, яка може передавати операнди за один або два цикли. Один із способів вирішення цієї проблеми - додавання кеш-пам'яті. Як ми говорили в розділі «Кеш-пам'ять» розділу 2, кеш-пам'ять містить найбільш часто використовувані слова, що підвищує швидкість доступу до них. Якщо достатньо біль- шой відсоток потрібних слів знаходиться в кеш-пам'яті, час очікування може силь-але скоротитися. Однією з найбільш ефективних технологій одночасного збільшення про- випускним здатності та зменшення часу очікування є застосування не-скількох блоків кеш-пам'яті. Основна технологія - введення окремої кеш-

пам'яті для команд і окремим для даних (розділеної кеш-пам'яті). Така кеш-пам'ять має кілька переваг. По-перше, операції можуть починати-ся незалежно в кожній кеш-пам'яті, що подвоює пропускну здатність сістеми пам'яті. Саме з цієї причини в мікроархітектурі Mic-1 нам знадобиться-лись два окремих порту пам'яті: особливий порт для кожної кеш-пам'яті. Відзначимо, що кожна кеш-пам'ять має незалежний доступ до основної пам'яті. В даний час багато систем пам'яті набагато складніше цих. Між розділеної кеш-пам'яттю і основною пам'яттю часто міститься кеш-пам'ять другого рівня. Взагалі кажучи, може бути три і більше рівнів кеш-пам'яті,оскільки потрібні більш просунуті системи. На рис. 4.25 зображена систе-

ма з трьома рівнями кеш-пам'яті. Прямо на мікросхемі центрального процесора знаходиться невелика кеш-пам'ять для команд і невелика кеш-пам'ять для даної них, зазвичай від 16 до 64 Кбайт. Є ще кеш-пам'ять другого рівня, яка роз-

покладено не на самій мікросхемі процесора, а поряд з ним в тому ж блоці. Кеш- пам'ять другого рівня з'єднується з процесором через високошвидкісний тракт даних. Ця кеш-пам'ять звичайно не є розділеною і містить суміш дан-

них і команд. Її розмір - від 512 Кбайт до 1 Мбайт. Кеш-пам'ять третього рівня знаходиться на тій же платі, що і процесор, і звичайно складається зі статичного ОЗУ в кілька мегабайтів, яке функціонує набагато швидше, ніж динамічний

дещо ОЗУ основної пам'яті. Зазвичай весь вміст кеш-пам'яті першого рівня знаходиться в кеш-пам'яті другого рівня, а весь вміст кеш-пам'яті другого рівня знаходиться в кеш-пам'яті третього рівня.