- •1.Архітектура сапр.

- •2.Характеристика мультипроцесорних комп’ютерних систем.

- •3.Топологія локальних мереж. Види і коротка характеристика

- •1.Реляційна модель даних. Загальна характеристика. Цілісність сутності і посилань.

- •2.Алгоритм шифрування даних гост 28147-89. Основні характеристики алгоритму. Основні режими роботи алгоритму(призначення, схема роботи, переваги та недоліки кожного режиму)

- •3.Схемотехніка зовнішніх інтерфейсів еом. Шини і2с, послідовний паралельний порт, шина usb.

- •4.Мережні обладнання: комутатор, концентратор, шлюз, міст, маршрутизатор. Функції та стисла характеристика).

- •5.Характеристика та структура матричних процесорів.

- •1.Дешифратори, типи, побудова, характеристики

- •3.Ієрархічні системи. Ієрархічні структури даних. Маніпулювання даними. Обмеження цілісності.

- •4.Модель мультипроцесорних комп’ютерних систем із загальною пам’яттю.

- •1.Двійкові однорозрядні суматори.

- •2.Схема Ель-Гемаля. Процедура шифрування. Процедура розшифрування.

- •3.Семантичне моделювання даних,er – діаграми. Семантичні моделі даних.

- •4.Розімкнена мережева модель систем оперативної обробки інформації.

- •5.Технологія бездротової передачі даних Wi-Fi.

- •2.Характеристика мультипроцесорних комп’ютерних систем з перехресною комутацією.

- •3.Високовиробничі технічні засоби сапр та їх комплексування.

- •4.Проектування реляційних баз даних. Проектування реляційних бд із використанням нормалізації.

- •1.Двійково – десяткові суматори.

- •4.Синтез систем оперативної обробки інформації із заданою вартістю.

- •5.Технологія 100vg-AnyLan (середовище передачі інформації в мережі, основні технічні характеристики, апаратура, топологія, метод доступу).

- •2.Характеристика конвеєрного процесора для векторної обробки інформації.

- •4.Загальні поняття реляційного підходу до організації бд. Основні концепції і терміни.

- •1.Однокристальні восьмирозрядні мікропроцесори.

- •3.Фундаментальні властивості відношень. Відсутність кортежів-дублікатів. …

- •2.Замкнута мережева модель систем оперативної обробки інформації з обмеженим числом заявок.

- •3.Основні функції субд. Управління буферами оперативної пам’яті. Управління трансакціями.

- •4.Абстрактні моделі захисту інформації: Сазерлендская модель. Модель Кларка-Вільсона.

- •4.Синтез соо інформації із заданою вартістю.

- •1.Кабельні системи: коаксіальний кабель, «кручена пара», оптоволоконний кабель.

- •2.Побудова мережених моделей систем оперативної обробки інформації.

- •3.Робочі станції – сервери для сапр.

- •4.Пристрої цифрового керування. Керуючі автомати зі схемною логікою.

- •1.Тупики, розпізнавання і руйнація. Метод тимчасових міток. Журналізація…

- •2.Технологія fddi (середовище передачі інформації, основні технічні характеристики, метод доступу).

- •5.Схеми порівняння і контролю.

- •1.Комбінаційні функціональні вузли комп’ютерної схемотехніки. Мультиплексори, демультиплексори.

- •2.Склад, організація та режими роботи технічних засобів сапр.

- •5.Технологія Gigabit Ethernet (середовище передачі інформації, основні технічні.Характеристики).

- •1.Технологія Token-Ring (апаратура, топологія, основні технічні характеристики, метод доступу).

- •2.Характеристика асоціативних комп’ютерних систем.

- •3.Криптосистема шифрування даних rsa. Процедура шифрування. Процедура розшифрування.

- •5.Паралельні багаторозрядні суматори.

- •3.Асиметричні криптосистеми, концепція криптосистеми з відкритим ключом: недоліки симетричних криптосистем, необхідні умови для ака, характерні особливості ака, узагальнена схема акс,…

- •5.Технологія Arcnet (апаратура, топологія, основні технічні характеристики, метод доступу.

- •3.Мережні обладнання: комутатор, концентратор, шлюз, міст, маршрутизатор.

- •4.Характ-ка процесорної матриці з локальною пам’яттю.

- •1.Алгоритми електронного цифрового підпису. Поняття аутентифікації. Призначення ецп…

- •2.Схеми для виконання логічних мікрооперацій.

- •3.Характеристика мультипроцесорних комп’ютерних систем з багатовходовими озп.

- •4.Локальне периферійне обладнання сапр.

- •1.Архітектура сапр

- •2.Технологія 100vg-AnyLan .

- •3.Характеристика функціонально розподілених комп’ютерних систем.

- •1.Семантичне моделювання даних,er – діаграми. Семантичні моделі даних.

- •2.Постійна пам’ять комп’ютерів. Мікросхеми пам’яті на ліз мон-транзисторах.

- •3.Характеристика однорідних комп’ютерних систем.

- •1.Абстрактні моделі захисту інформації: модель Біба, модель Гогена-Мезигера.

- •4.Модель мультипроцесорних комп’ютерних систем із загальною пам’яттю.

- •5.Схемотехніка зовнішніх інтерфейсів еом. Шини і2с, послідовний паралельний порт, шина usb.

- •1.Керування транзакціями, серіалізація. Транзакція і цілісність баз даних. Ізольованість користувачів.

- •2.Дешифратори, типи, побудова, характеристики.

- •2.Технологія Gigabit Ethernet (середовище передачі інформації, основні технічні.Характеристики.

- •1.Комбінаційні функціональні вузли комп’ютерної схемотехніки.Мультиплексори, демультиплексори.

- •3.Високовиробничі технічні засоби сапр та їх комплексування.

- •1.Однокристальні восьмирозрядні мікропроцесори.

- •2.Загальні поняття реляційного підходу до організації бд. Основні концепції і терміни.

- •4.Фундаментальні властивості відношень. Відсутність кортежів-дублікатів.

- •1.Характеристика мультипроцесорних комп’ютерних систем з перехресною комутацією.

- •2.Проектування бд. Створення бд.

- •3.Призначення пакетів і їх структура.

- •4.Єдинонаправленні функції. Визначення єдинонаправлених функцій.

- •5.Двійкові однорозрядні суматори.

- •2.Технологія fddi (середовище передачі інформації, основні технічні характеристики, метод доступу).

- •3.Проектування реляційних баз даних. Проектування реляційних бд із використанням нормалізації.

- •4.Характеристика та структура матричних процесорів.

- •5.Статичні запам’ятовуючі пристрої.

5.Паралельні багаторозрядні суматори.

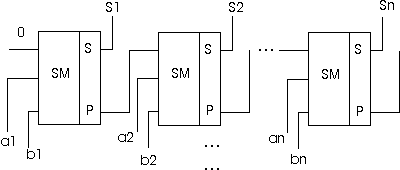

П араллельные

многоразрядные сумматоры предназначены

для одновременного суммирования двух

многоразрядных чисел и характеризуются

различными способами передачи сигналов

переноса от младших разрядов сумматора

к старшим. Различают параллельные

комбинационные сумматоры с последовательным,

одновременным и комбинированным

переносом. Выбор типа переноса между

разрядами суммирующего устройства

определяется требованиями к быстродействию.

Простейшими из параллельных сумматоров

(ПС) являются ПС с последовательной

передачей сигналов переноса (рис. 1). На

входы каждой одноразрядной схемы

сумматора поступают два слагаемых и

перенос из предыдущего разряда. Сигнал

переноса, образованный в младшем разряде,

распространяется последовательно по

цепям переноса к старшим разрядам. Время

распространения переноса определяется

суммарной задержкой этих цепей.

Быстродействие сумматора при сложении

двух n-разрядных чисел характеризуется

временем суммирования, которое в

наихудшем случае равно tS=(n-1)tP+tiS где tis,

tP - задержки формирования одноразрядным

сумматором суммы и переноса соответственно.

Следовательно, сумматоры с последовательным

переносом обладают низким быстродействием.

С целью повышения быстродействия

(сокращения времени сложения) применяются

сумматоры с одновременным переносом.

Серьезным недостатком сумматоров с

одновременным переносом является

значительный рост аппаратурных затрат

при построении схем межразрядных

переносов. Поэтому на практике применяют

метод построения сумматоров с

комбинированным переносом. В сумматорах

с комбинированным переносом полные

одноразрядные сумматоры объединяются

в группы. Внутри группы, как правило,

осуществляется одновременный перенос.

Между группами перенос может быть как

последовательный, так и одновременный.

араллельные

многоразрядные сумматоры предназначены

для одновременного суммирования двух

многоразрядных чисел и характеризуются

различными способами передачи сигналов

переноса от младших разрядов сумматора

к старшим. Различают параллельные

комбинационные сумматоры с последовательным,

одновременным и комбинированным

переносом. Выбор типа переноса между

разрядами суммирующего устройства

определяется требованиями к быстродействию.

Простейшими из параллельных сумматоров

(ПС) являются ПС с последовательной

передачей сигналов переноса (рис. 1). На

входы каждой одноразрядной схемы

сумматора поступают два слагаемых и

перенос из предыдущего разряда. Сигнал

переноса, образованный в младшем разряде,

распространяется последовательно по

цепям переноса к старшим разрядам. Время

распространения переноса определяется

суммарной задержкой этих цепей.

Быстродействие сумматора при сложении

двух n-разрядных чисел характеризуется

временем суммирования, которое в

наихудшем случае равно tS=(n-1)tP+tiS где tis,

tP - задержки формирования одноразрядным

сумматором суммы и переноса соответственно.

Следовательно, сумматоры с последовательным

переносом обладают низким быстродействием.

С целью повышения быстродействия

(сокращения времени сложения) применяются

сумматоры с одновременным переносом.

Серьезным недостатком сумматоров с

одновременным переносом является

значительный рост аппаратурных затрат

при построении схем межразрядных

переносов. Поэтому на практике применяют

метод построения сумматоров с

комбинированным переносом. В сумматорах

с комбинированным переносом полные

одноразрядные сумматоры объединяются

в группы. Внутри группы, как правило,

осуществляется одновременный перенос.

Между группами перенос может быть как

последовательный, так и одновременный.

Билет № 18 ТДАХТ

1.Технології CAD/CAM/CAE та їх зміст. Почти все крупные предприятия используют в своей работе возможности компьютерной техники, в частности CAD, CAE, CAM технологии, т.к. они предоставляют ряд преимуществ, таких как: -Совершенствование методов проектирования, в частности, использование методов многовариантного проектирования и оптимизации для поиска эффективных вариантов и принятия решений. -Повышение качества проектной документации. -Совершенствование управления процессом разработки проектов. -Частичная замена натурных экспериментов и макетирования моделированием на ЭВМ. -Уменьшение объёма испытаний и доводки опытных образцов в результате повышения уровня достоверности проектных решений и, следовательно, снижение временных затрат. CAD, CAE, CAM системы предназначены для комплексной автоматизации проектирования, конструирования и изготовления продукции. В них фактически объединены три системы разного назначения, разработанные на единой базе, аббревиатуры которых расшифровываются следующим образом: CAD - Computer Aided Design - компьютерная поддержка конструирования; САЕ - Computer Aided Engineering - компьютерная поддержка инженерного анализа; САМ - Computer Aided Manufacturing - компьютерная поддержка изготовления; Этап конструирования (CAD, САЕ) предполагает объемное и плоское геометрическое моделирование, инженерный анализ на расчётных моделях высокого уровня, оценку проектных решений, получение чертежей. Этап технологической подготовки производства (АСТПП) - на Западе называют САРР (Computer Automated Process Planing) - предполагает разработку технологических процессов, технологической оснастки, управляющих программ (УП) для оборудования с ЧПУ. Сюда входит задача САПР ТП - разработка технологической документации (маршрутной, операционной), доводимой до рабочих мест и регламентирующей процесс изготовления детали. Конкретное описание обработки на оборудовании с ЧПУ в виде управляющих программ вводится в систему автоматизированного управления производственным оборудованием (АСУПР), также называемую САМ. САЕ системы, используемые для анализа и оценки функциональных свойств проектируемых узлов и деталей, охватывают широкий круг задач моделирования упругонапряженного, деформированного, теплового состояния, колебаний конструкции, стационарного и нестационарного газодинамического и теплового моделирования с учетом вязкости, турбулентных явлений, пограничного слоя и т.п. Наиболее распространены САЕ-системы, использующие решение систем дифференциальных уравнений в частных производных методом конечных элементов (МКЭ).

2

.Двійкові

багаторозрядні суматори послідовної

дії. Сумматор — логический операционный

узел, выполняющий арифметическое

сложение двоичных, троичных или n-ичных

кодов двух (бинарный), трёх (тринарный)

или n чисел (n-нарный). При арифметическом

сложении выполняются и другие

дополнительные операции: учёт знаков

чисел, выравнивание порядков слагаемых

и тому подобное. Сумматоры являются

комбинационными схемами, выполняющими

бинарную (двухоперандные), тринарную

(трёхоперандные) или n-арную (n-операндную)

логическую функцию сложения. Входят в

состав узлов арифметическо-логических

устройств (АЛУ). Для того чтобы получить

многоразрядный сумматор, достаточно

соединить входы и выходы переносов

соответствующих двоичных разрядов.

.Двійкові

багаторозрядні суматори послідовної

дії. Сумматор — логический операционный

узел, выполняющий арифметическое

сложение двоичных, троичных или n-ичных

кодов двух (бинарный), трёх (тринарный)

или n чисел (n-нарный). При арифметическом

сложении выполняются и другие

дополнительные операции: учёт знаков

чисел, выравнивание порядков слагаемых

и тому подобное. Сумматоры являются

комбинационными схемами, выполняющими

бинарную (двухоперандные), тринарную

(трёхоперандные) или n-арную (n-операндную)

логическую функцию сложения. Входят в

состав узлов арифметическо-логических

устройств (АЛУ). Для того чтобы получить

многоразрядный сумматор, достаточно

соединить входы и выходы переносов

соответствующих двоичных разрядов.

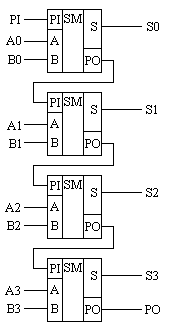

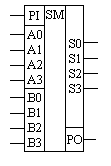

Схема соединения одноразрядных сумматоров для реализации четырехразрядного сумматора приведена на рис. 1. Одноразрядные

сумматоры практически никогда не использовались, так как почти

сразу же были выпущены микросхемы многоразрядных сумматоров. Полный двоичный четырехразрядный сумматор изображается на схемах как показано на рис. 2.