- •Введение

- •Расшифровка и анализ задания

- •2.2 Генератор тактовых импульсов

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.8 Программируемый таймер кр580ви53

- •3.3 Подключение устройств памяти и ввода-вывода к магистралям микроЭвм

- •4.3 Разработка контроллера прямого доступа к памяти

- •4.4 Упрощенная структурная схема микропроцессорной системы

- •5 Разработка алгоритма работы микропроцессорной

- •6 Разработка электрической принципиальной схемы

- •70 Изм. Лист № Докум. Подпись Дата Уитс.161ххх.122 пз Лист.

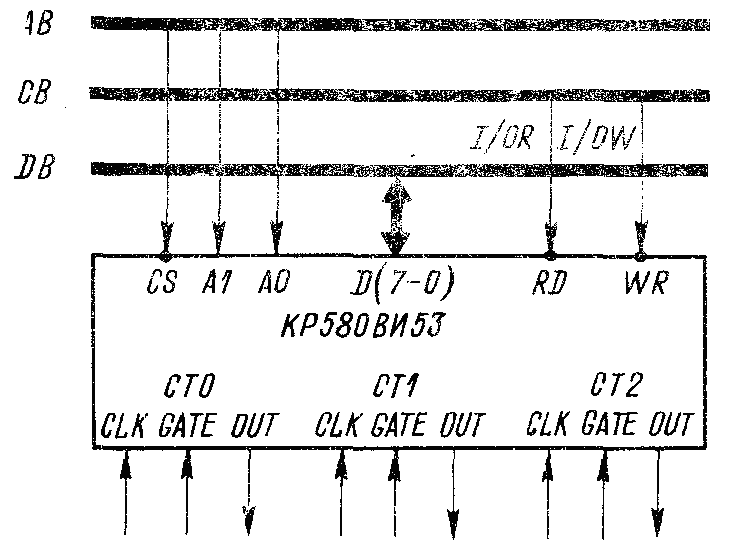

2.8 Программируемый таймер кр580ви53

БИС программируемого таймера КР58ОВИ53 предназначена для организации работы микропроцессорных систем в режиме реального времени и позволяет формировать сигналы с различными временными и частотными характеристи-ками.

Программируемый таймер (ПТ) имеет три независимых канала, каждый из которых содержит 16-разрядный вычитающий счетчик. Счетчики могут работать в двоичном или двоично-десятичном коде, с однобайтными или двухбайтными числами. Скорость счета программно изменяется от 0 до 2 МГц.

Упрощенная структурная схема ПТ приведена на рисунке 20. В состав БИС входят: буфер данных (ВD), предназначенный для обмена данными и управляющими словами между МП и ПТ; схема управления чтением-записью (RWCU), обеспечивающая выполнение операций ввода-вывода информации в ПТ; регистр управляющего слова (RGR), предназначенный для записи управляющих слов, задающих режимы работы счетчиков; счетчик каналов (СТ0 — СТ2).

Рисунок 14 — Структурная схема программируемого таймера КР580ВИ53

Назначение входных, управляющих сигналов ПТ указано при описании выводов микросхемы в таблице 13.

Таблица 8 — Описание выводов программируемого таймера.

-

Обозначение вывода

Номер контакта

Назначение вывода

D(7-0)

1; 2: 3:

4.5;6;7;8

Канал данных

RD

22

Сигнал «чтение»

WR

23

Сигнал «запись»

А0, A1

19; 20

Адресные входы, выбирающие один из каналов ПТ или управляющий регистр

CS

21

Выбор микросхемы

CLK0 - CLK2

9; 15; 18

Входы синхронизации счетчиков

САТЕ0-СЛТЕ2

11; 14; 16

Входы управлениясчетчиков

OUT0-OUT2

10; 13: 17

Выходные сигналы

UСС

24

Напряжение питания ( + 5В)

GND

12

Напряжения питания (0 В)

Подключение ПТ к шинам микропроцессора показано на рисунке 21. Установка режима работы каждого канала ПТ производится программно путем записи управляющего слова и начального значения содержимого счетчика (N) с помощью команд вывода (OUT).

Рисунок 15 — Схема подключение ПТ к шинам микропроцессора

Основные электрические параметры микросхемы КР58ОВИ53 при температуре окружающей среды (+25 … +10)°С приведены ниже:

Выходное напряжение логического нуля UOL, В < 0,4

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления IСС, мА < 115

Ток утечки на входах IIL, мкА —1,...,1

Ток утечки на выходах IOL, мкА —1,5,...,1,5

2.9 Разработка упрощенной структурной схемы

Микропроцессорный комплект серии К1810 включает в себя 8- и 16-разрядные МП, позволяющие производить высокоскоростные вычисления и обмен данными; устройства формирования магистралей и арбитража многопроцессорных взаимодействий и универсальные интерфейсные БИС, предназначенные для выполнения широкого набора функций ускоренной передачи информации, счета временных интервалов и обработки прерываний от УВВ

В составе микроЭВМ, построенной на основе МПК серии К1810, можно использовать все интерфейсные БИС 8-разряд-ного МПК серии КР580.

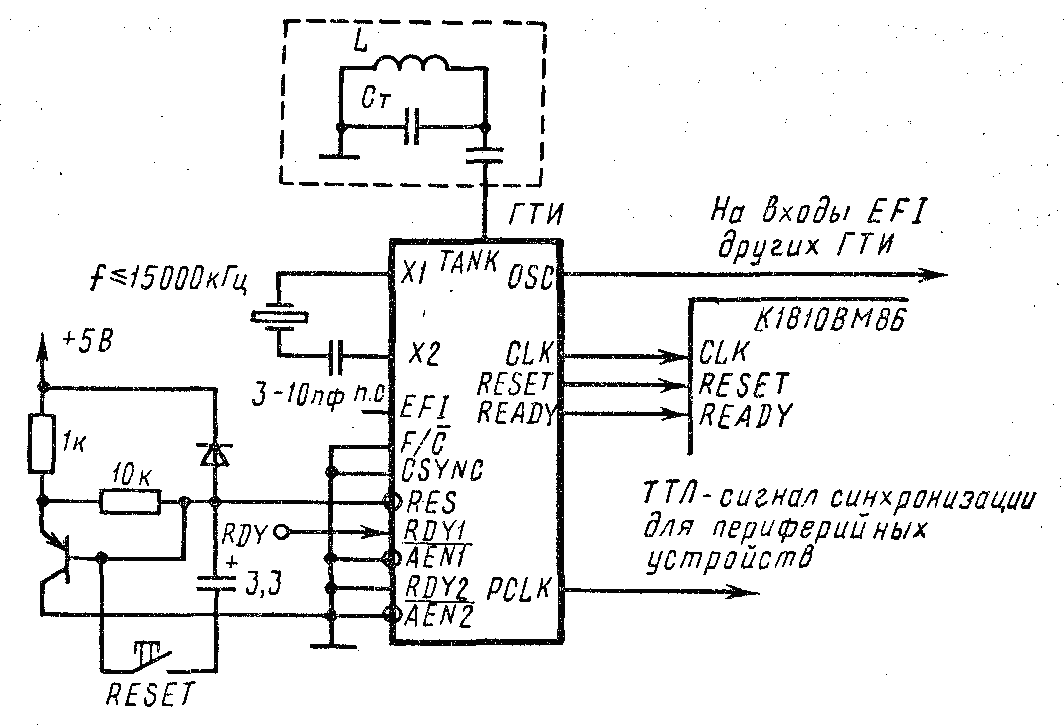

2.9.1 Синхронизация работы МП БИС К1810ВМ86. Для синхронизации работы МП БИС используется микросхема тактового генератора 1810ГФ84. Схема подключения тактового генератора к МП БИС показаны на рисунке 11.

Основной сигнал синхронизации МП частотой до 5 МГц формируется делением на 3 опорной частоты ОSС кварцевого генератора (вход F/С = 0) или внешнего задающего сигнала, подключенного ко входу ЕР1 (вход F/С = 1), что позволяет использовать один кварцевый резонатор для задания частоты нескольким тактовым генераторам. Их полную синхронизацию можно обеспечить одновременной подачей внешнего сигнала синхронизации СSYNC на вход микросхем КР1810ГФ84.

Рисунок 16 — Схема подключения тактового генератора к МП БИС

Кварцевый резонатор можно возбудить и на более высокой гармонике, для чего ко входу ТANК через разделительный конденсатор подключается LС-контур, настроенный на частоту верхней гармоники генератора.

Сигнал синхронизации периферийного оборудования РСLК для работы с более медленными УВВ вырабатывается путем деления частоты тактового сигнала СLК на 2.

Микросхема К1810ГФ84 вырабатывает также сигнал RESET начальной установки и стробирует внешние сигналы готовности периферийного оборудования READY.

Наличие двух сигналов

готовности RDY1,

RDY2

и разрешения

![]() ;

;

![]() необходимо для построения систем с

несколькими магистралями, к которым

подключены медленные устройства памяти

и ввода-вывода, а также для синхронизации

многопроцессорных взаимодействий.

необходимо для построения систем с

несколькими магистралями, к которым

подключены медленные устройства памяти

и ввода-вывода, а также для синхронизации

многопроцессорных взаимодействий.

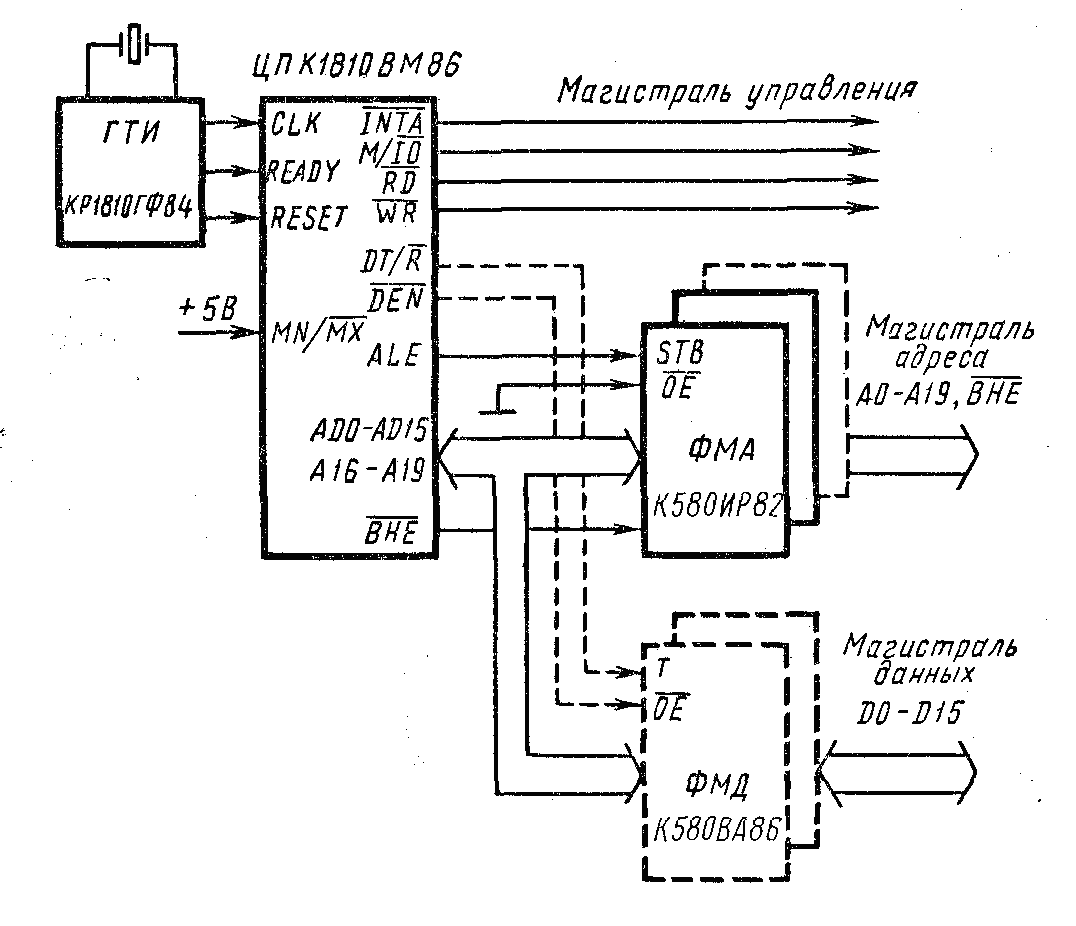

2.9.2 Формирование магистралей адреса, данных и управления микроЭВМ. Схемы формирования магистралей адреса, данных и управления различны при включении МП К1810ВМ86 в минимальном или максимальном режиме.

Рисунок 17 — Формирование магистралей адреса и данных при работе БИС ЦП К1810ВМ86 в минимальном режиме

В минимальном режиме

магистраль управления образуется

сигналами:

![]() — обращение к памяти или к УВВ,

— обращение к памяти или к УВВ,

![]() - строб чтения данных,

- строб чтения данных,

![]() — строб записи данных,

— строб записи данных,

![]() — строб чтения вектора прерываний, а

для управления регистрами магистрали

адреса и формирователями магистрали

данных используются сигналы приема-передачи

—

— строб чтения вектора прерываний, а

для управления регистрами магистрали

адреса и формирователями магистрали

данных используются сигналы приема-передачи

—

![]() и разрешения обмена данными —

и разрешения обмена данными —

![]()

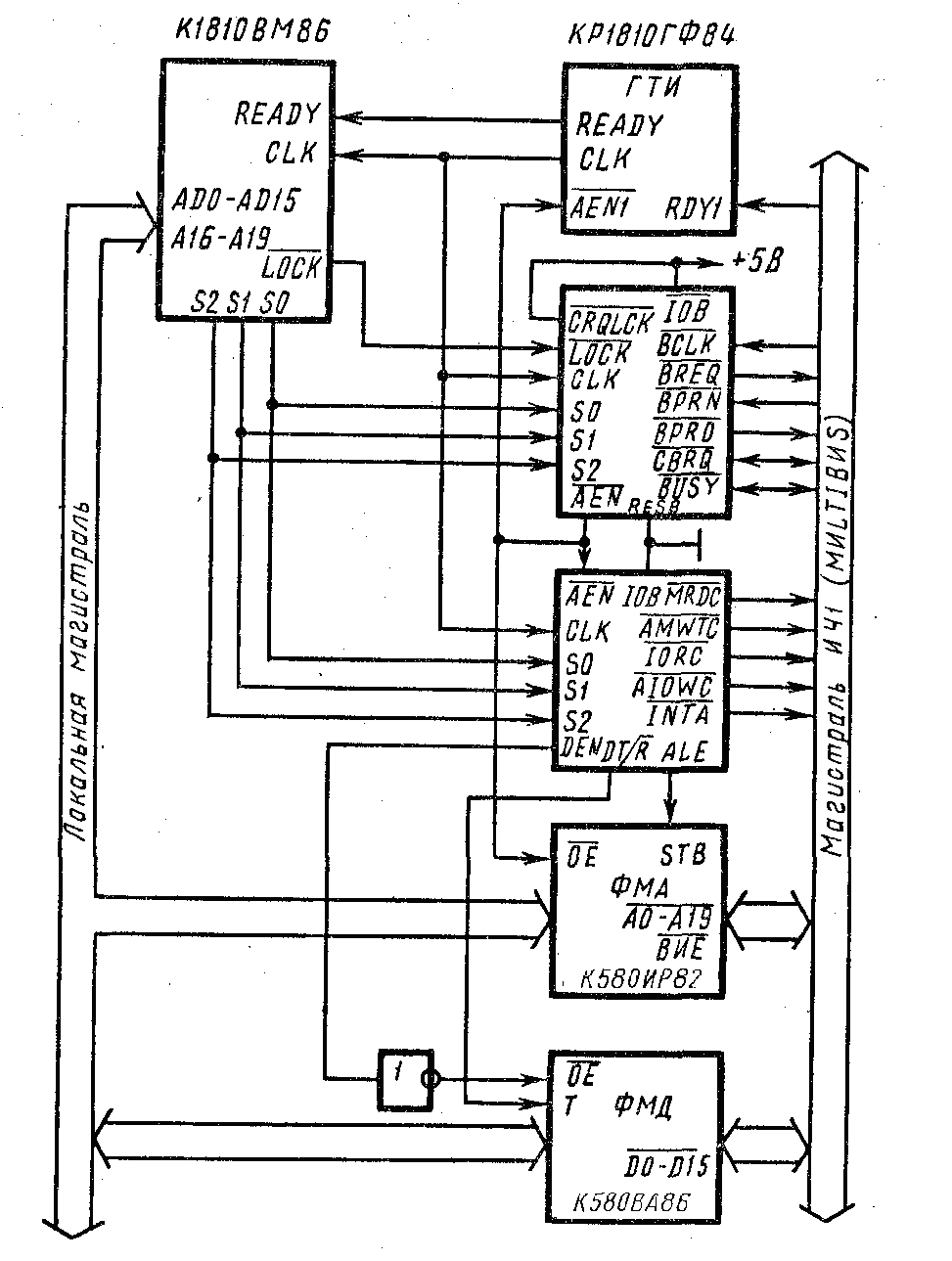

В максимальном режиме для формирования управляющих сигналов применяют системный контроллер КР1810ВГ88, обрабатывающий сигналы SO, SI, S2 состояния МП.

МП К1810ВМ86 можно подключать к общей многопроцессорной магистрали ИЧ1 (MULTIBUS); при этом для арбитража доступа МП БИС к магистрали необходимо использовать арбитр магистрали БИС К1810ВБ89 (рисунок 13).

Рисунок 18 — Подключение МП БИС К1810ВМ86 в максимальном режиме к мультиплексорной магистрали ИЧ1 (MULTIBUS)

При необходимости захвата

магистрали процессором арбитр вырабатывает

сигналы запроса захвата магистрали

![]() и всеобщего запроса

и всеобщего запроса

![]() .

Если магистраль свободна (

.

Если магистраль свободна (![]() равно 1) и есть разрешение

равно 1) и есть разрешение

![]() с внешнего арбитра распределения

приоритетов (при параллельной обработке

приоритетов), то формируется сигнал

захвата магистрали

с внешнего арбитра распределения

приоритетов (при параллельной обработке

приоритетов), то формируется сигнал

захвата магистрали

![]() и по сигналу

и по сигналу

![]() информация с внутренней магистрали

адреса выдается на магистраль ИЧ1.

Этот же сигнал разрешает системному

контроллеру К1810ВГ88 выдать на магистраль

сигналы управления

информация с внутренней магистрали

адреса выдается на магистраль ИЧ1.

Этот же сигнал разрешает системному

контроллеру К1810ВГ88 выдать на магистраль

сигналы управления

![]() ,

MWTC,

,

MWTC,

![]() ,

IOWC.

,

IOWC.

Сигнал

![]() используется в схемах с последовательным

заданием приоритетов для трансляции

сигнала разрешения доступа

используется в схемах с последовательным

заданием приоритетов для трансляции

сигнала разрешения доступа

![]() (в том случае, когда процессор не требует

доступа к магистрали) арбитру с более

низким приоритетом (приоритет задается

последовательностью соединения арбитров)

на его вход

(в том случае, когда процессор не требует

доступа к магистрали) арбитру с более

низким приоритетом (приоритет задается

последовательностью соединения арбитров)

на его вход

![]() для дальнейшей обработки.

для дальнейшей обработки.

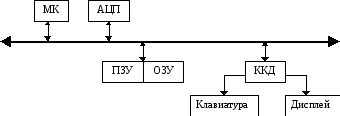

Упрощенная схема микропроцессорной системы показана на рисунке 19.

Рисунок 19 — Упрощенная схема микропроцессорной системы

3 Разработка систем памяти

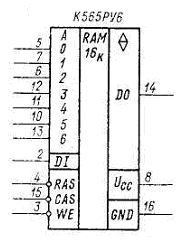

3.1 БИС ОЗУ К565РУ6

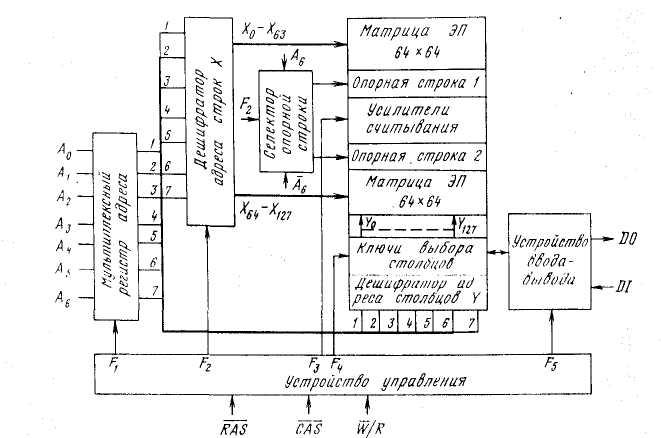

ОЗУ динамического типа серии К565. Микросхемы серии К565 представляют собой оперативные запоминающие устройства с произвольной выборкой динамического типа, изготавливаются по n-канальной МОП-технологии с кремниевыми затворами и двумя типами транзисторов (с индуцированным и встроенным каналом) и предназначены для построения накопителей ОЗУ большой емкости.

В состав серии входят: К565РУ5 (Б, В, Г, Д) емкостью 65 536 бит с организацией 65536x1 бит; К565РУ5 (Д1, Д2) емкостью 32 763 бит с организацией 32 768 х I бит; К565РУ5 (ДЗ, Д4) емкостью 16 384 бит с организацией 16 384 х 1 бит; КР565РУ6 (Б, В, Г, Д) емкостью 16 384 бит с организацией 16384 х 1 бит. Внешние сигналы: RAS — сигнал выбора адреса строк, С AS — сигнал выбора адреса столбцов, WE — сигнал записи/считывания, а также сигналы, вырабатываемые схемой управления, обеспечивают работу ОЗУ в режимах считывания, записи, постраничного считывания или постраничной записи, считывания-модификации-записи, регенерации по сигналу RAS.

Временные диаграммы работы микросхем в режимах считывания, записи. считывание — модификация — запись, регенерации приведены на рисунке 5 г - ж. Это позволяет при работе в страничном режиме получить значительный выигрыш в быстродействии. Внутри страничного режима возможна любая комбинация режимов записи, считывания и считывание — модификация — запись.

Регенерация информации в динамических ячейках памяти осуществляется за 128 циклов путем обращения к каждой из 128 строк не ранее, чем через каждые 2 мс перебором адресов /1(0 — 6). Регенерация может быть осуществлена в любом из режимов ОЗУ, однако наиболее просто ее выполнить в режиме регенерации по сигналу RAS. когда сигнал CAS находится в неактивном высоком логическом состоянии (регенерация сигналом RAS). При регенерации в этом режиме имеет место минимальная потребляемая мощность. При эксплуатации микросхем необходимо помнить, что после подачи напряжения питания БИС ОЗУ переходит в нормальный режим функционирования через 2,0 мс и требует проведения затем 16 рабочих циклов регенерации.

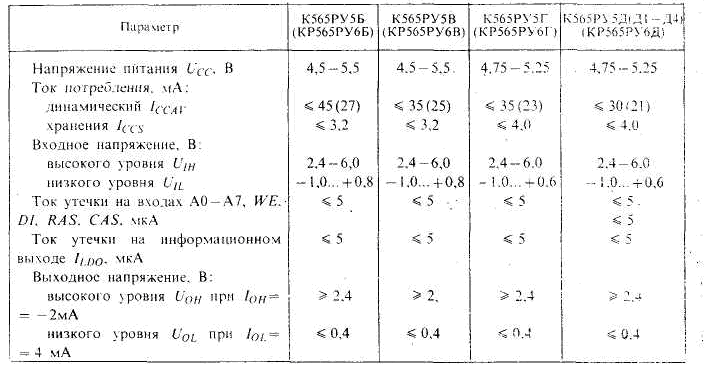

Основные электрические и временные параметры БИС ОЗУ К565РУ5, КР565РУ6 при температуре 25±100С приведены в таблице 4.

Таблице 9 – Основные электрические и временные параметры БИС ОЗУ

К565РУ5, КР565РУ6

Рисунок 19 – Микросхема ОЗУ КР565РУ6

Рисунок 20 – Структура микросхемы динамического ОЗУ

-

БИС ПЗУ К573РФ2

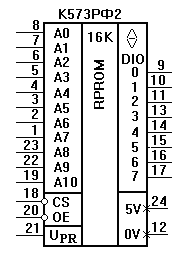

Микросхема К573РФ2 с ультрафиолетовым стиранием информации, условное обозначение которой приведено на рисунке 12, имеет емкость 2 килобайта и допускает 100 циклов программирования.

Рисунок 12- Условно графическое изображение ПЗУ К573РФ2

Для стирания записанной информации микросхему извлекают из контактного устройства замыкают все ее выводы полоской фольги и помещают под источник ультрафиолетового света, обеспечив ее обдув. Стирание можно произвести, не извлекая микросхему из контактного устройства, но тогда надо отключить напряжение питания и сигналы. Излучение проникает к полупроводниковому кристаллу РПЗУ через прозрачное окно в крышке корпуса. Время стирания информации составляет 30-60минут.

Режиму работы микросхемы К573РФ2: хранение, считывание, запись (программирование), стирание, контроль обеспечивают сигналами управления CS, OE, UPR

Микросхема К573РФ2 управляется сигналом CS - выбора микросхемы: при подаче этого сигнала с активным уровнем открывается доступ к накопителю для записи или считывания информации, сигналом OE - разрешение выхода (считывания).

Запись информации в накопитель можно провести в автономном программаторе. При записи информации предварительно должны быть поданы адреса сигнала для выбора ячейки накопителя и сигналы данных. Напряжение программирования на микросхему подают постоянным уровнем. Контроль правильности записи информации осуществляется либо по циклу считывания, либо по циклу контроля, отличающегося тем, что напряжение программирования остается тем же, что и при записи.

После каждого контроля считывания при положительном результате по этому же адресу рекомендуется подать программирующий импульс трехкратной длительности для закрепления записи.

Режим запрета программирования применяется для защиты микросхемы в составе модуля ПЗУ, объединенных одноименными выводами. Если одна из таких микросхем установлена в режиме записи, то у остальных должен быть обеспечен режим запрета программирования. Это достигается сигналом подачей OE=1 и сигнала выбора, инверсного по отношению к его состоянию в режиме записи CS=0.Считывание информации производится в асинхронном режиме доступа к накопителю, при котором сигналы на входы CS и OE подаются уровнями. Быстродействие микросхемы определяется временем выборки.

Характерные особенности микросхем серии К573 приведены ниже.

-

Наличие информационных выводов мультиплексирования для входной и выходной информации.

-

Информация считается в том же коде, в каком записывается.

-

Выводы микросхем могут находиться в трех состояниях: с низким уровнем напряжения, с высоким уровнем напряжения, в состоянии не выбора микросхемы с высоким выходным сопротивлением.

4.Стирание информации проводят путем воздействия потока ультрафиолетового излучения с длиной волны λ=300 нм через крышку с кварцевым стеклом в течении 30 минут.

В таблице 10 приведены режимы программирования (записи), считывания и хранения записанной информации для микросхемы К573РФ2.

Таблица 10- Режимы программирования (записи), считывания и хранения записанной информации для микросхемы К573РФ2

-

Сигнал

Запись

Считывание

Хранение

CS

1*

0

1

OE

1

0

X

UPR, В

25

5

5

DIO

DI

DO

Z

* - сигнал действует в течение 50 мс.