- •1 Расшифровка и анализ задания

- •2.1 Разработка процессорного модуля и интерфейса

- •2.2 Разработка упрощенной структурной схемы

- •3 Разработка подсистемы памяти

- •3.4 Подключение озу и пзу к системной шине

- •4 Разработка системы ввода/вывода

- •4.1 Аналогово-цифровой преобразователь

- •4.2 Параллельный интерфейс

- •4.3 Блок индикации

- •4.4 Логический элемент «не»

- •4.5 Подключение индикаторов к микроконтроллеру

- •4.6 Подключение матричной клавиатуры к порту ввода/вывода

- •4.8 Логические элементы «или-не»

- •5 Разработка алгоритма работы мпс

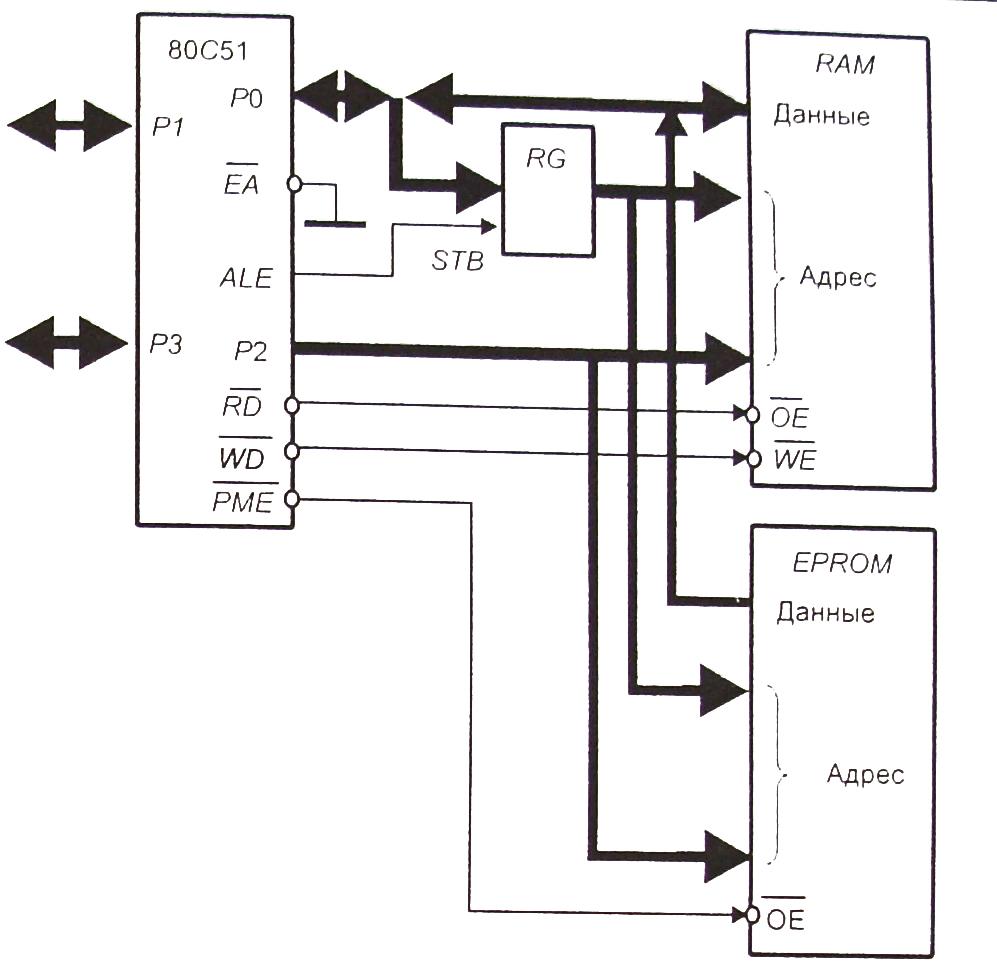

3.4 Подключение озу и пзу к системной шине

Внешняя оперативная память доступна МК по командам пересылки МОVХ А, @R и МOVX @R,А , которые по косвенному адресу (регистры R0 и R1) выполняют операции передачи байта между ВПД и аккумулятором. Сигналом ALE косвенный адрес, выводимый по шине BUS, фиксируется в многорежимном буферном регистре МБР. Сигналы WR и RD определяют режим работы БИС ОЗУ. Так как косвенный адрес имеет формат байта, то схема на рисунке 8 обеспечивает адресацию 256 ячеек ОЗУ в дополнение к 64 ячейкам резидентной памяти данных МК48.

Внешняя постоянная память подключаются к шине BUS своими информационными выходами. Младший байт адреса по сигналу ALE фиксируется на внешнем буферном регистре.

Схема подключения внешней памяти данных и команд представлена на рисунке 15.

Рисунок 15 – Подключение внешней памяти данных и программ к ОМЭВМ К1816ВЕ51

Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде.

4 Разработка системы ввода/вывода

4.1 Аналогово-цифровой преобразователь

В качестве устройство ввода информации выбран аналогово-цифровой преобразователь К1113ПВ1.

Данная микросхема была выбрана по параметрам питания: +5В, а также по параметру энергопотребления данная микросхема является одной из самых экономичных среди своих аналогов.

Полупроводниковая БИС функционально завершенного АЦП типа К111ЗПВ1 предназначена для применения в электронной аппаратуре в составе блоков аналогового ввода. Микросхема выполняет функцию аналого-цифрового преобразования однополярного или биполярного входного сигнала с представлением результатов преобразования в параллельном двоичном коде. Она содержит все функциональные узлы АЦП. Выходные каскады позволяют считывать результат преобразования непосредственно на шину данных МП.

Микросхемы представляют собой функционально законченный 10-разрядный АЦП, сопрягаемый с микропроцессором. Обеспечивает преобразование как однополярного напряжения (вывод 15 соединяется с выводом 16) в диапазоне 0...9,95 В, так и биполярного напряжения в диапазоне -4,975...+4,975 В в параллельный двоичный код. В состав ИС входят ЦАП, компаратор напряжения регистр последовательного приближения (РПП), источник опорного напряжения (ИОН), генератор тактовых импульсов (ГТИ), выходной буферный регистр с тремя состояниями, схемы управления. Выходные каскады с тремя состояниями позволяют считывать результат преобразования непосредственно на шину данных микропроцессора. По уровням входных и выходных логических сигналов сопрягаются с ТТЛ схемами. В ИС выходной ток ЦАП сравнивается с током входного резистора от источника сигнала и формируется логический сигнал РПП. Тактирование РПП обеспечивается импульсами встроенного ГТИ с частотой следования 300...400 кГц. Установка РПП в исходное состояние и запуск его в режим преобразования производится по внешнему сигналу "гашение и преобразование". По окончанию преобразования АЦП вырабатывает сигнал "готовность данных" и информация из РПП поступает на цифровые входы через каскады с тремя состояниями.

Условное графическое изображение представлено на рисунке 16.

Рисунок 16 – Микросхема К1113ПВ1

Таблица 6 - Назначение выводов:

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

Состояние |

|

#1-10;(#) |

1-9; 18 |

Выводы разряда |

0,1 |

|

W*;(-) |

13 |

Вход аналоговый |

0,1 |

|

СO; (-) |

11 |

гашение и преобразование |

0,1 |

|

СО*; (-) |

15 |

управление сдвигом нуля |

0,1 |

|

U1; (Uп1) |

10 |

напряжение питания Uп1 |

1 |

|

-U2; (Uп) |

12 |

напряжение питания Uп2 |

1 |

|

OV*(аОбщ) |

14 |

аналоговая "земля" |

0 |

|

OV#; (Общ.) |

16 |

цифровая "земля" |

0 |

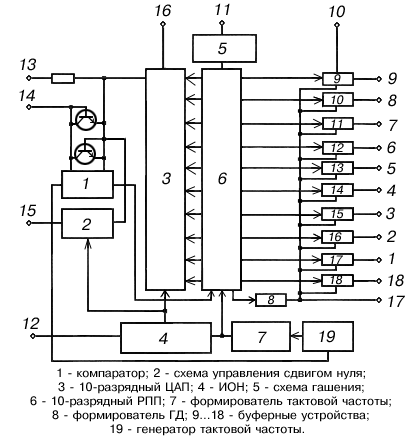

Функциональная схема АЦП приведена на рисунке 17. Электрические параметры указаны в таблице 6.

Таблица 6 – Электрические параметры БИС К1113ПВ1

|

Название параметра |

Значение параметра |

|

1 |

2 |

|

Номинальное напряжение питания Uп1 |

5

В

|

|

Номинальное напряжение питания Uп2

|

-15

В

|

Продолжение таблицы 6

|

1 |

2 |

|

Выходное напряжение низкого уровня |

не более 0,4 В |

|

Выходное напряжение высокого уровня |

не менее 2,4 В |

|

Напряжение смещения нуля в однополярном и биполярном режимах от полной шкалы |

|

|

Ток потребления от источника питания Uп1 от источника питания Uп2 |

не более 10 мА не более 18 мА |

|

Входной ток высокого (низкого) уровня |

|

|

Ток утечки на выходе |

|

|

Время преобразования |

не более 30 мкс |

|

Нелинейность от полной шкалы |

|

|

Абсолютная погрешность преобразования в конечной точке шкалы от полной шкалы |

|

1 – компаратор; 2 – схема управления сдвигом нуля; 3 – 10-разрядный ЦАП; 4 – ИОН; 5 – схема гашения; 6 – 10-разрядный РПП; 7 – формирователь тактовой частоты; 8 – формирователь; 9 – 18 – буферные устройства; 19 – генератор тактовой частоты.

Рисунок 17 – Структурная схема микросхемы К1113ПВ1