- •1 Расшифровка и анализ задания

- •2.1 Разработка процессорного модуля и интерфейса

- •2.2 Разработка упрощенной структурной схемы

- •3 Разработка подсистемы памяти

- •3.4 Подключение озу и пзу к системной шине

- •4 Разработка системы ввода/вывода

- •4.1 Аналогово-цифровой преобразователь

- •4.2 Параллельный интерфейс

- •4.3 Блок индикации

- •4.4 Логический элемент «не»

- •4.5 Подключение индикаторов к микроконтроллеру

- •4.6 Подключение матричной клавиатуры к порту ввода/вывода

- •4.8 Логические элементы «или-не»

- •5 Разработка алгоритма работы мпс

2.2 Разработка упрощенной структурной схемы

Для создания управляющей микроЭВМ на базе однокристальной микроЭВМ необходимы следующие устройства:

-

память, состоящая из ПЗУ и ОЗУ;

-

параллельный интерфейс;

-

аналогово-цифровой преобразователь (АЦП) и цифро-аналоговый преобразователь (ЦАП) для преобразования аналоговых и цифровых сигналов с датчиков и на органы управления;

-

блок клавиатуры и индикации.

Упрощенная структурная схема микроЭВМ представлена на рисунке 8.

В качестве параллельного интерфейса выбрана микросхема К580ВВ55, поскольку у микроконтроллера и микросхем серии 580 совпадают напряжения уровней сигналов (0 В - для логического нуля, 5 В – для логической единицы).

В качестве АЦП выбрана К1113ПВ1, в качестве ЦАП – К1113ПА2.

В качестве ОЗУ и ПЗУ выбраны соответственно К537РУ8 и К56РТ5.

В качестве индикаторов выбраны АЛС321А, подключаемые через дешифратор К514ИД1, клавиатура и индикаторы подключаются через параллельный интерфейс.

Рисунок 8 – Упрощенная структурная схема микроЭВМ

3 Разработка подсистемы памяти

3.1 Модуль ОЗУ К537РУ8

Микросхема ОЗУ - К537РУ8. Данная серия микросхем наиболее развита. Она включает в себя более 20 типономиналов микросхем, отличающихся друг от друга информационной емкостью (от 1024 до 65536 бит), организацией (одноразрядная и словарная), быстродействием (более чем в пять раз), потребляемой мощностью. Общими свойствами микросхем являются: единое напряжение питания 5 В, уровни ТТЛ входных и выходных сигналов, схема выхода с тремя состояниями и др. Таким образом, при необходимости увеличения ОЗУ достаточно взять микросхему большей емкости той же серии. Микросхема КР537РУ8 имеет емкость 2К х 8 байт и работает в режиме записи, считывания и хранения информации, в зависимости от сигналов управления, приходящих с микроконтроллера.

Рисунок 9 – Цоколевка БИС ОЗУ К537РУ8

Основные характеристики К537РУ8, приведены в таблице 4

Таблица 3 – Назначение выводов БИС ОЗУ К537РУ8

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

Состояние |

|

D(0-7); (-) |

9-11; 13-17 |

Выход данных |

0,1 |

|

А (0-10); (а) |

1-8; 19;22;23 |

Выходы адреса |

0,1 |

|

CS; (ВМ) |

18 |

Выбор микросхемы |

0,1 |

|

OE; (-) |

20 |

Разрешение по выходу (считывания) |

0,1 |

|

W/R; (ЗП/СЧ) |

21 |

Запись – считывание |

0,1 |

|

UCC; (UНП) |

26 |

Напряжение питания (+5 В) |

1 |

|

GND (Общ) |

7 |

Общий вывод микросхемы |

0 |

Для микросхемы памяти К537РУ8 характерно сравнительно невысокое быстродействие, высокая помехоустойчивость, малая потребляемая мощность, способность сохранять записанную информацию при напряжении питания 1,5 ... 3 В.

Таблица 4 – Статические характеристики К537РУ8

|

|

|

|

|

|

|

|

||||

|

|

|

L |

H |

L |

H |

L |

H |

|||

|

5±5% |

- |

36 |

1 |

- |

0,4 |

4,1 |

0,4 |

2,4 |

1,6 |

0,1 |

Таблица истинности К537РУ8, приведена в таблице 5.

Таблица 5 - Таблица истинности К537РУ8

|

|

|

|

|

|

Режим работы |

|

1 |

Х |

Х |

Х |

Z |

Хранение |

|

0 |

Х |

0 |

А |

0 |

Запись 0 |

|

0 |

Х |

0 |

А |

1 |

Запись 1 |

|

0 |

1 |

1 |

А |

Z |

Чтение без выдачи |

|

0 |

0 |

1 |

А |

|

Считывание |

Микросхема КР537РУ8 имеет словарную организацию Эти микросхемы допускают запись и считывание информации 8-разрядными словами. Информационные входы и выходы в этих микросхемах совмещены, поэтому записываемая информация вводится в микросхему, а считываемая выводится из нее по одним линиям, что обусловливает мультиплексный режим их работы.

Другой особенностью названных микросхем является наличие у них дополнительного сигнала управления ОЕ состоянием выхода. Он может подаваться одновременно с сигналом выбора CS или с некоторой задержкой. Отсутствие разрешающего состояния этого сигнала, как можно видеть из таблиц истинности, не позволяет вывести считанную информацию из микросхемы. В этом режиме выходы находятся в Z-состоянии. При наличии всех необходимых для считывания сигналов выходы переходят в функциональное состояние только по сигналу ОЕ = 0. Считываемые данные появятся на выходах спустя время выборки сигнала разрешения выхода.

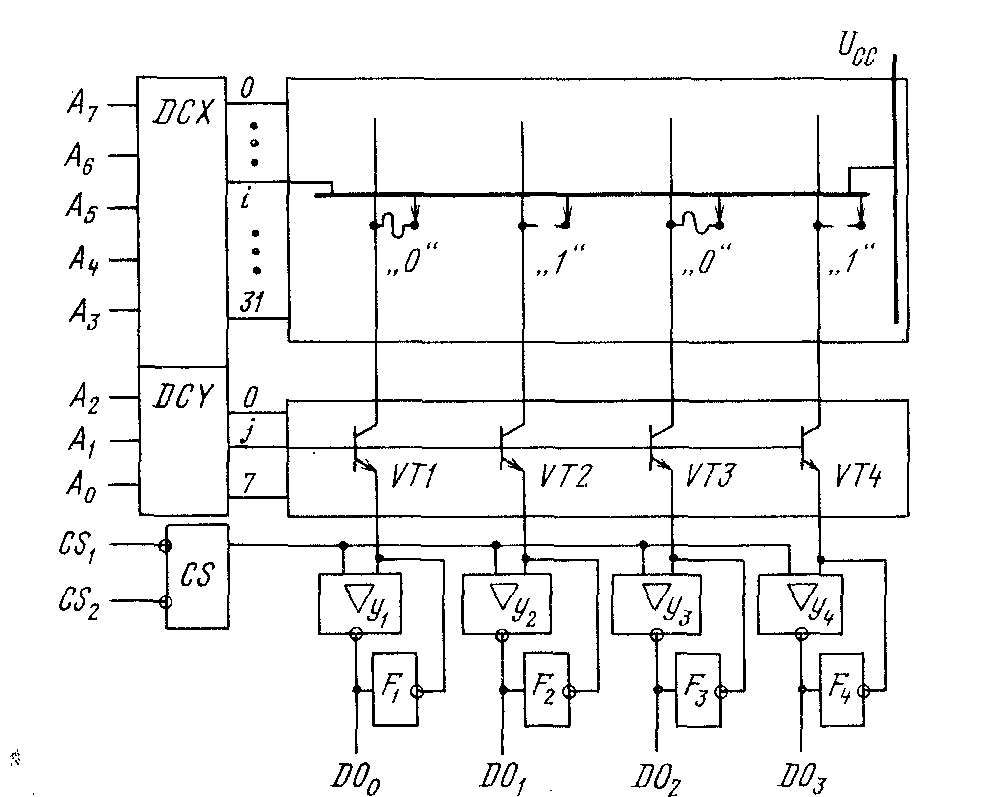

Структурная схема БИС приведена на рисунке 15.

Рисунок 10 - Структурная схема БИС ОЗУ К537РУ8

Она содержит матрицу запоминающих элементов 128х128 М, представляющую собой накопитель емкостью 16384 бит, дешифраторы адреса строк DCF и столбцов DCS, блок управления СИ, адресные и выходные формирователи BF и разрядные усилители записи/считывания DD.

Чтение и запись информации ведутся словами, размерностью в 1 байт. Дешифратор адреса строки, реализует функцию одной линии из 128, а столбца - функцию выбора 8-ми линий из 128. Выходной формирователь содержит восемь усилителей считывания и следующих за ними оконченных каскадов, осуществляющих усиление и передачу данных на выход. Адресный код А0 - А11 запоминается в регистре адреса и не зависит от состояния внешних адресных шин.

На функциональной схеме БИС ОЗУ изображена в виде микросхемы ОЗУ (приложение А).

3.2 Модуль ПЗУ К541РТ2

Микросхемы программируемых ПЗУ по принципу построения и функционирования аналогичны масочным ПЗУ, но имеют существенное отличие в том, что допускают программирование на месте своего применения пользователем. Операция программирования заключается в разрушении (пережигании) части плавких перемычек на поверхности кристалла импульсами тока амплитудой 30 ... 50 мА. Технические средства для выполнения этой операции достаточно просты и могут быть построены самим пользователем. Это обстоятельство в сочетании с низкой стоимостью и доступностью микросхем ПЗУ обусловило их широкое распространение в радиолюбительской практике.

В данном курсовом проекте рассматривается применение микросхемы ПЗУ К541РТ2, представленной на рисунке 9. Микросхемы ПЗУ серии К541 выполнены по технологии ИИЛ.

Матрица до программирования, т. е. в исходном состоянии, содержит однородный массив проводящих перемычек, соединяющих строки и столбцы во всех точках их пересечений. Перемычки устанавливают из поликристаллического кремния. Перемычка в матрице выполняет роль ЭП. Наличие перемычки кодируют логической 1, если усилитель считывания является повторителем, и логическим 0, если усилитель считывания - инвертор. Следовательно, микросхема ПЗУ в исходном состоянии перед программированием в зависимости от характеристики выходного усилителя может иметь заполнение матрицы либо логическим 0, либо логической 1.

Рисунок 11 — Микросхема ПЗУ К541РТ2

Таблица 5 — Описание выводов БИС ПЗУ К541РТ2

|

Обозначение вывода |

Номер контакта |

Назначение вывода, |

Состояние |

|

D(0-7); (-) |

17; 16; 15; 14; 13; 11; 10; 9; |

Выход данных |

0,1 |

|

А (0-10); (а) |

8; 7; 6; 5; 4; 3; 2; 1; 23; 22; 19 |

Входы данных с локальной шины МП |

0,1 |

|

CS(1-3); (ВМ) |

18 |

Выбор микросхемы; L-уровень сигнала подключает ПЗУ к системной шине |

0,1 |

|

UCC; (UНП) |

26 |

Напряжение питания (+5 В) |

1 |

|

GND (Общ) |

7 |

Общий вывод микросхемы |

0 |

Программирование микросхемы, матрица которой в исходном состоянии заполнена 0, заключается в пережигании перемычек в тех ЭП, где должны храниться 1. Если матрица в исходном состоянии заполнена 1, то пережигают перемычки в ЭП, где должны храниться 0.

Типичный вариант реализации микросхемы ППЗУ представлен на рисунке 12.

Рисунок 12 – Структурная схема микросхемы К451РТ2

Микросхемы ППЗУ потребляют большую мощность от источника питания. Поэтому представляется целесообразным использовать их свойство работать в режиме импульсного питания, когда питание на микросхему подают только при обращении к ней для считывания информации. Особенности применения микросхем ППЗУ в этом режиме состоят; в следующем: во-первых, на управляющие входы должны быть поданы уровни, разрешающие доступ к микросхеме: если необходим 0, то данный вывод соединяют с общим выводом, если 1, то с шиной через резистор с сопротивлением 1 кОм; в этом случае функции сигнала выбора микросхемы выполняет импульс напряжения питания Ucc; во-вторых, для обеспечения 1 режима импульсного питания применяют транзисторные ключи, на переходах которых падает часть напряжений, поэтому напряжение, подаваемое к внешним ключам, должно быть выбрано с учетом требования иметь на выводе питания микросхемы номинальное напряжение 5 В; в-третьих, из-за инерционности процессов коммутации цепи питания время выборки адреса микросхемы увеличивается в 2-3 раза.

При использовании импульсного режима питания среднее значение потребляемого тока и, следовательно, уровень потребляемой мощности существенно уменьшаются.

3.3 Многорежимный буферный регистр К589ИР12

Для подключения дополнительных микросхем ПЗУ и ОЗУ выберем многорежимный буферный регистр (МБР) К589ИР12.

Корпус микросхемы пластмассовый прямоугольный типа 239.24-2.

Основные параметры микросхемы приведены в таблице 5.

Таблица 4 – Основные параметры микросхемы К589ИР12

|

Название параметра |

Значение |

|

Напряжение источника питания |

5 В ± 5% |

|

Диапазон рабочих температур |

-10 ... +70 °С |

|

Предельное напряжение источника питания (кратковременно в течение 5 мс), не более |

7 В |

|

Предельное напряжение источника питания, не более |

6 В |

|

Предельное напряжение на выходе (закрытой ИС), не более |

5,25 В |

|

Предельное входное напряжение, не более |

5,5 В |

|

Предельный ток на входе, не менее |

-5 мА |

Условное обозначение микросхемы К589ИР12 представлена на рисунке 13.

Структурная схема многорежимного буферного регистра приведена на рисунке 14.

Рисунок 13 – Условное обозначение БИС К589ИР12

Рисунок 14 – Структурная схема БИС К589ИР12

Описание выводов МБР приведено в таблице 5.

Запись данных в RG из шины D1(7 — 0) происходит положительным потенциалом на входе С, описываемым выражением:

![]() .

.

Чтение

информации в шину DO

(7 — 0) производится

высоким потенциалом сигнала

![]() .

Сигнал

запроса прерывания вырабатывается

низким потенциалом при комбинации

сигналов

.

Сигнал

запроса прерывания вырабатывается

низким потенциалом при комбинации

сигналов

![]() ,

где

Q

-данные

на прямом плече триггера Г.

,

где

Q

-данные

на прямом плече триггера Г.

Таблица 5 – Назначение выводов

|

Обозначение вывода |

Номер контакта |

Назначение вывода, |

Состояние |

|

D1-D8; (-) |

22; 20; 18; 16; 9; 7; 5; 3 |

8-разрядная параллельная входная шина данных |

0,1 |

|

Q1-Q8; (-) |

21; 19; 17; 15; 10; 8; 6; 4 |

8-разрядная параллельная выходная шина данных |

0,1 |

|

EW; (ВС) |

11 |

Вход строба; (0;1) |

0,1 |

|

MD; (ВР) |

2 |

Вход выбора режима |

0,1 |

|

CS1, CS2; (ВК) |

1; 13 |

Входы выбора кристалла |

0,1 |

|

CLR; (CLR) |

14 |

Вход установки нуля |

0,1 |

|

INP; (INP) |

23 |

Выход запроса прерывания |

0,1 |

Установка

триггера производится по низкому

потенциалу асинхронно при комбинации

сигналов

![]() .

Сброс триггера производится отрицательным

фронтом сигнала на входе STB.

.

Сброс триггера производится отрицательным

фронтом сигнала на входе STB.