3.4 Подключение озу и пзу к системной шине

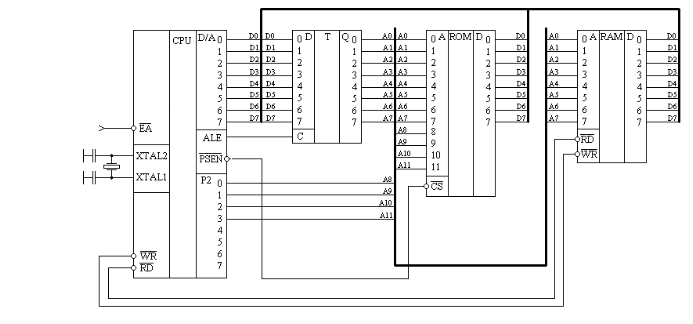

Внешняя оперативная память доступна МК по командам пересылки МОVХ А, @R и МOVX @R,А , которые по косвенному адресу (регистры R0 и R1) выполняют операции передачи байта между ВПД и аккумулятором. Сигналом ALE косвенный адрес, выводимый по шине BUS, фиксируется в многорежимном буферном регистре МБР. Сигналы WR и RD определяют режим работы БИС ОЗУ. Так как косвенный адрес имеет формат байта, то схема на рисунке 8 обеспечивает адресацию 256 ячеек ОЗУ в дополнение к 64 ячейкам резидентной памяти данных МК48.

Внешняя постоянная память подключаются к шине BUS своими информационными выходами. Младший байт адреса по сигналу ALE фиксируется на внешнем буферном регистре.

Схема подключения внешней памяти данных и команд представлена на рисунке 13. Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде.

Рисунок 13 – Подключение внешней памяти данных и программ к ОМЭВМ К1816ВЕ48

4 РАЗРАБОТКА СИСТЕМЫ ВВОДА/ВЫВОДА

4.1 Аналогово-цифровой преобразователь

В качестве устройство ввода информации выбран аналогово-цифровой преобразователь К1113ПВ1.

Полупроводниковая БИС функционально завершенного АЦП типа К111ЗПВ1 предназначена для применения в электронной аппаратуре в составе блоков аналогового ввода. Микросхема выполняет функцию аналого-цифрового преобразования однополярного или биполярного входного сигнала с представлением результатов преобразования в параллельном двоичном коде. Она содержит все функциональные узлы АЦП. Выходные каскады позволяют считывать результат преобразования непосредственно на шину данных МП. Несколько АЦП могут обслуживать один МП и наоборот. По уровням входных и выходных сигналов АЦП сопрягается с цифровыми ТТЛ ИС.

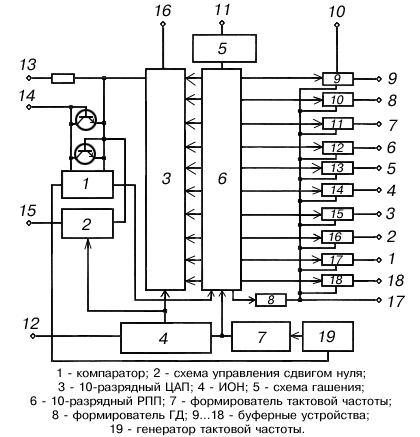

Микросхемы представляют собой функционально законченный 10-разрядный АЦП, сопрягаемый с микропроцессором. Обеспечивает преобразование как однополярного напряжения (вывод 15 соединяется с выводом 16) в диапазоне 0...9,95 В, так и биполярного напряжения в диапазоне -4,975...+4,975 В в параллельный двоичный код. В состав ИС входят ЦАП, компаратор напряжения регистр последовательного приближения (РПП), источник опорного напряжения (ИОН), генератор тактовых импульсов (ГТИ), выходной буферный регистр с тремя состояниями, схемы управления. Выходные каскады с тремя состояниями позволяют считывать результат преобразования непосредственно на шину данных микропроцессора. По уровням входных и выходных логических сигналов сопрягаются с ТТЛ схемами. В ИС выходной ток ЦАП сравнивается с током входного резистора от источника сигнала и формируется логический сигнал РПП. Стабилизация разрядных токов ЦАП осуществляется встроенным ИОН. Тактирование РПП обеспечивается импульсами встроенного ГТИ с частотой следования 300...400 кГц. Установка РПП в исходное состояние и запуск его в режим преобразования производится по внешнему сигналу "гашение и преобразование". По окончанию преобразования АЦП вырабатывает сигнал "готовность данных" и информация из РПП поступает на цифровые входы через каскады с тремя состояниями. Корпус К1113ПВ1(A-B) типа 2104.18-1, масса не более 2,5 г, 1113ПВ1(A-B) типа 238.18-1, масса не более 2,5 г.

Условное графическое изображение представлено на рисунке 14.

Рисунок 14 – Микросхема К1113ПВ1

Назначение выводов:

1 - девятый разряд; 2 - восьмой разряд; 3 - седьмой разряд; 4 - шестой разряд; 5 - пятый разряд; 6 - четвертый разряд; 7 - третий разряд; 8 - второй разряд; 9 - первый разряд; 10 - напряжение питания Uп1; 11 - гашение и преобразование; 12 - напряжение питания -Uп2; 13 - вход аналоговый; 14 - аналоговая "земля"; 15 - управление сдвигом нуля; 16 - цифровая "земля"; 17 - готовность данных;18 - десятый разряд (младший).

Функциональная схема АЦП приведена на рисунке 15. Электрические параметры указаны в таблице 7.

Таблица 7 – Электрические параметры БИС К1113ПВ1

|

Название параметра |

Значение параметра |

|

1 |

2 |

|

Номинальное напряжение питания Uп1 |

5

В

|

|

Номинальное напряжение питания Uп2

|

-15

В

|

|

Выходное напряжение низкого уровня |

не более 0,4 В |

|

Выходное напряжение высокого уровня |

не менее 2,4 В |

|

Напряжение смещения нуля в однополярном и биполярном режимах от полной шкалы |

|

Продолжение таблицы 7

|

1 |

2 |

|

Ток потребления от источника питания Uп1 от источника питания Uп2 |

не более 10 мА не более 18 мА |

|

Входной ток высокого (низкого) уровня |

|

|

Ток утечки на выходе |

|

|

Время преобразования |

не более 30 мкс |

|

Нелинейность от полной шкалы |

|

|

Абсолютная погрешность преобразования в конечной точке шкалы от полной шкалы |

|

1 – компаратор; 2 – схема управления сдвигом нуля; 3 – 10-разрядный ЦАП; 4 – ИОН; 5 – схема гашения; 6 – 10-разрядный РПП; 7 – формирователь тактовой частоты; 8 – формирователь; 9 – 18 – буферные устройства; 19 – генератор тактовой частоты.

Рисунок 15 – Структурная схема микросхемы К1113ПВ1

4.2 Параллельный интерфейс

Для расширения портов ввода/вывода воспользуемся БИС КР580ВВ55.

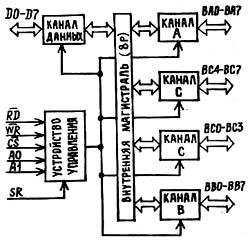

БИС КР580ВВ55 применяется в микропроцессорной технике в качестве элемента ввода/вывода общего назначения для подключения интерфейсных устройств (клавиатуры, принтера, накопителя на магнитной ленте и так далее) к магистралям данных. Условное графическое изображение микросхемы показано на рисунке 16, а ее структурная схема - на рисунке 27. Данные о назначении выводов приведены в таблице 8.

Рисунок 16 – Условное обозначение БИС КР580ВВ55

Рисунок 27 – Структурная схема БИС КР580ВВ55

Таблица 8 – Назначение выводов

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

D(7 – 0) |

27; 28; 29; 30; 31; 32; 33; 34 |

Вход/выход данных |

|

RD |

5 |

Чтение; L-уровень сигнала разрешает считывание информации с регистра, адресуемого по входам А0, А1 на шину D(7 – 0) |

|

WR |

36 |

Запись; L-уровень сигнала разрешает запись информации с шины D(7 – 0) в регистр ППИ, адресуемый по входам А0, А1 |

|

A0, A1 |

9; 8 |

Входы для адресации внутренних регистров ППИ |

|

RESET |

35 |

Сброс; Н-уровень сигнала обнуляет регистр управляющего сигнала и устанавливает все порты в режим ввода |

|

CS |

6 |

Выбор микросхемы; L-уровень сигнала подключает ППИ к системной шине |

|

PA(7 – 0) |

37; 38; 39; 40; 1; 2; 3; 4 |

Вход/выход канала А |

|

PB(7 – 0) |

15; 24; 23; 22; 21; 20; 19; 18 |

Вход/выход канала В |

|

PC(7 – 0) |

10; 11; 12; 13; 17; 16; 15; 14 |

Вход/выход канала С |

|

UCC |

26 |

Напряжение питания (+5 В) |

|

GND |

7 |

Напряжение питания (0 В) |

Обмен информацией между магистралью данных системы и микросхемой KР580BB55A осуществляется через 8-разрядный двунаправленный канал данных (D). Для связи с периферийными устройствами используются 24 линии ввода/вывода, сгруппированные в три 8-разрядных канала БА, ВВ и ВС, режимы работы которых и направление передачи информации определяются программным способом.

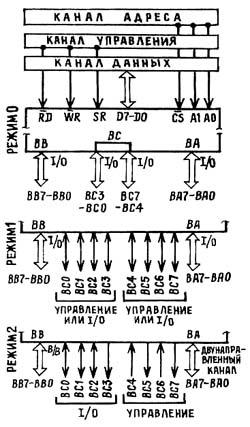

Микросхема имеет три режима работы. В режиме 0 обеспечивается синхронная, программно-управляемая передача данных через два независимых 8-разрядных канала ВА и ВВ и два 4-разрядных канала ВС.

В режиме 1 обеспечивается ввод или вывод информации "в" или "из" периферийного устройства через каналы ВА и ВВ по специальным сигналам. При этом линии канала С используются для приема и выдачи сигналов управления обменом информацией. В режиме 2 обеспечивается возможность обмена информацией с периферийными устройствами через двунаправленный 8-разрядный канал ВА по специальным сигналам. Для передачи и приема сигналов управления обменом используются пять линий канала ВС. Выбор соответствующего канала и направление передачи информации через канал определяется сигналами А0, А1 (обычно соединяется с младшими разрядами канала адреса системы), RD, WR, CS в соответствии с таблицей 9.

Режим работы каждого из каналов ВА, ВВ и ВС определяется содержимым регистра управляющего слова (РУС). Записав в него управляющее слово, микросхему можно перевести в один из трех режимов работы: режим 0 - простой ввод/вывод, режим 1 - стробируемый ввод/вывод, режим 2- двунаправленный канал.

При подаче сигнала SR регистр управляемого слова устанавливается в состояние, при котором все каналы настраиваются в режиме 0 для ввода информации. Режим работы каналов можно изменять не только в начале, но в самом процессе выполнения программы. Благодаря этому одна микросхема может в определенном порядке последовательно обслуживать несколько различных периферийных устройств. При изменении режима работы любого канала все входные и выходные регистры каналов и триггеры состояния сбрасываются. Режимы работы каналов представлены на рисунке 18.

Таблица 9

|

Сигналы на входах |

Направление передачи информации |

||||

|

А1 |

А0 |

Р0 |

Р |

С |

|

|

Операция ввода (чтение) |

|||||

|

0 |

0 |

0 |

1 |

0 |

ВА – канал данных |

|

0 |

1 |

0 |

1 |

0 |

ВВ – канал данных |

|

1 |

0 |

0 |

1 |

0 |

ВС – канал данных |

|

Операция вывода (запись) |

|||||

|

0 |

0 |

1 |

0 |

0 |

Канал данных – ВА |

|

0 |

1 |

1 |

0 |

0 |

Канал данных – ВВ |

|

1 |

0 |

1 |

0 |

0 |

Канал данных – ВС |

|

1 |

1 |

1 |

0 |

0 |

Канал данных – РУС |

|

Операция блокировки |

|||||

|

Х |

Х |

Х |

Х |

1 |

Канал данных – третье состояние |

|

1 |

1 |

0 |

0 |

0 |

Запрещенная комбинация |

Рисунок 18 – Режимы работы каналов

4.3 Блок индикации

Для индикации выбраны светодиодные индикаторы АЛС321А.

Светодиодные индикаторы серий АЛС321 имеют хорошие светотехнические характеристики, но в номинальном режиме потребляют довольно большой ток - для каждого элемента около 20 мА. При динамической индикации амплитудное значение тока в несколько раз больше.

4.4 Дешифратор К514ИД1

Микросхемы К514ИД1 представляют собой многорежимный буферный регистр. Корпус микросхем пластмассовый прямоугольный типа 239.24-2.

Параметры микросхемы К514ИД1 приведены в таблице 10, условное графическое изображение – на рисунке 19.

Таблица 10 – Параметры дешифратора К514ИД1

|

Название параметра |

Значение параметра |

|

Напряжение источника питания |

5 В ± 5% |

|

Диапазон рабочих температур |

-10 ... +70 °С |

|

Предельное напряжение источника питания (кратковременно в течение 5 мс), не более |

7 В |

|

Предельное напряжение источника питания, не более |

6 В |

|

Предельное напряжение на выходе (закрытой ИС), не более |

5,25 В |

|

Предельное входное напряжение, не более |

5,5 В |

|

Предельный ток на входе, не менее |

-5 мА |

Рисунок 19 – Условное графическое изображение К514ИД1

Назначение выводов:

Х0-Х3 – входы разрядов, A-G – вход управления сегментами, Ucc – питание, GND – общий, BI – вход модуляции.

4.5 Подключение индикаторов к микроконтроллеру

Для подсоединения индикаторов к микропроцессору между ними необходимо вставить дешифратор К514ИД1 (рисунок 20).

Рисунок 20 – Подсоединение индикатора АЛС321А к дешифратору К514ИД1

В качестве преобразователей двоично-десятичного кода в семиэлементный промышленность выпускает дешифраторы К514ИД1.

4.6 Контроллер прерываний, контроллер прямого доступа к памяти, программируемый таймер

Контроллер прерываний, контроллер прямого доступа памяти и таймер входят в состав однокристальной микроЭВМ К1816ВЕ48 (их принцип действия рассмотрен в пункте 2). Следовательно, включение дополнительных устройств в структурную схему управляющей микроЭВМ не требуется.

По результатам сделанного подбора микросхем начертим функциональную схему управляющей микроЭВМ (приложение А).

5 РАЗРАБОТКА АЛГОРИТМА РАБОТЫ МИКРОПРОЦЕССОРНОЙ

СИСТЕМЫ