- •1 Расшифровка и анализ задания

- •1.1. Общая структура разрабатываемой микроЭвм

- •1.2 Реакция системы на внешние события

- •2.1 Архитектура однокристальной микроЭвм к1816ве51

- •3 Разработка подсистемы памяти

- •3.1 Описание микросхемы кр537ру8

- •3.2 Описание микросхемы бис пзу к541ре1

- •3.3 Подключение озу и пзу к системной шине

- •4 Разработка подсистем ввода/вывода, прерываний и пдп

- •4.1 Аналогово-цифровой преобразователь

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5 Контроллер клавиатуры/дисплея кр580вд79

- •4.6 Уточненная схема управляющей микроЭвм

- •5 Разработка программного обеспечения

- •5.1 Алгоритм управления объектом

- •5.2 Разработка блок-схемы управляющей системы

- •6.1 Основные технические данные и характеристики

- •6.1.1 Параметры назначения:

- •6.1.2 Конструктивные параметры, параметры надежности и безопасности.

- •6.2 Устройство

3 Разработка подсистемы памяти

Подсистема памяти разрабатываемой системы включает в себя модуль ОЗУ и модуль ПЗУ, доступ к которым осуществляется по системной магистрали.

3.1 Описание микросхемы кр537ру8

Оперативные ЗУ предназначены для хранения переменной информации и имеют практически одинаковое быстродействие при считывании и записи. МС статической ОЗУ КР537РУ8 характеризуется: по технологии изготовления – КМДП, по режиму доступа – Т, емкость составляет 2Кх8 бит.

Основные электрические параметры.

Напряжение питания UCC, B 4,75 - 5,25.

Ток потребления динамический ICCAV, мА менее 20.

Ток потребления хранения ICCS, мкА менее 1000.

Ток потребления в режиме хранения от

резервного источника питания ICCB, мкА менее 200.

Выходное напряжение высокого уровня UOH, В более 2,4.

Высокое напряжение низкого уровня UOL, В менее 0,4.

Ток утечки на входе ILI, мкА менее 5.

Ток утечки на выходе ILO, мкА менее 5.

Выходной ток низкого уровня IOL, мА менее 2.

Входная емкость С1, пФ менее 8.

Выходная емкость С0, пФ менее 10.

Предельная емкость нагрузки, пФ менее 1000.

Время цикла считывания (записи) tCR(CW), нс более 300. Время выборки разрешения tAС, нс 270.

Длительность сигнала CS tCS, нс 220.

Длительность сигнала WE tW, нс 80 – 120.

Время сдвига CS относительно адреса tCSA, нс более 50.

Время сдвига WE относительно DI tWS, нс более 20.

Время сдвига CS относительно WE tCSW, нс более 20.

Время сохранения адреса после CS tCHA , нс более 60.

Время сохранения WE после CS tCHW, нс более 30.

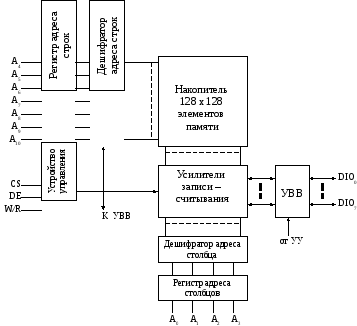

Структуру МС КР537РУ8 рассмотрим на рисунке 9.

Рисунок 9 - Структура микросхемы КР537РУ8

Организация одноразрядная и словарная с числом разрядов в слове четыре, восемь и шестнадцать. Для КМДП - микросхем характерен самый низкий уровень потребляемой мощности. Многие из них способны сохранять записанную информацию при пониженном до 2-3 В напряжении питания, что позволяет реализовать энергонезависимые ОЗУ с встроенным низковольтным источником питания.

Данная МС содержит матрицу запоминающих элементов 2048*8, представляющую собой накопитель ёмкостью 16384 бит (16 Кбит), дешифраторы адреса строк (DCK) и столбцов (DCS), блок управления СИ, адресные и выходные формирователи и разрядные усилители записи-считывания. Режим работы устанавливается с помощью сигналов CS1, CS2, W/R.

О бозначение

выводов

МС КР537РУ8

представлено на рисунке 10, назначение

выводов микросхемы –

в таблице 2.

бозначение

выводов

МС КР537РУ8

представлено на рисунке 10, назначение

выводов микросхемы –

в таблице 2.

Рисунок 10 - Цоколевка микросхемы КР537РУ8

Таблица 2 - Назначение выводов микросхемы КР537РУ8

|

Номера контактов |

Обозначение

|

Назначение |

Тип сигнала |

Состояние |

|

1-8 |

А0 - А7 |

Порты адреса |

вх |

1, 0, z |

|

9 - 11, 13 - 17 |

D0 - D7 |

Входы-выходы порта D |

вх/вых |

1, 0, z |

|

12 |

OV |

"Земля" (Общий вывод И.П.) |

|

|

|

18 |

CS1 |

Сигнал выбора микросхемы 1 |

вх |

0 |

|

19 |

A10 |

Порты адреса |

вх/вых |

1, 0, z |

|

20 |

CS2 |

Сигнал выбора микросхемы 2 |

вх |

0 |

|

21 |

W/R |

Сигнал записи |

вых |

0 |

|

22-23 |

A8, A9 |

Порты адреса |

вх |

1, 0, z |

|

24 |

5 V |

Питание + 5В |

|

|

МС КР537РУ8 имеет встроенные входные регистры - «защелки», срабатывающие от перепада сигнала CS. Наличие входных регистров придает МС ряд особенностей, прежде всего в режимах управления.

Истинность представленной МС рассмотрена в таблице 3.

Таблица 3 – Истинность микросхемы КР537РУ8

|

CS1vCS2 |

WR/RD |

А0…А10 |

DIO0…DIO7 |

Режим работы |

|

1 |

Х |

X |

Z |

Хранение |

|

0 |

0 |

А |

D0…D7 |

Запись |

|

0 |

1 |

А |

D0…D7 |

Считывание |

Статический режим КР537РУ8 характеризуется напряжением питания 5 В, близкими значениями уровней выходных сигналов, сравнительно небольшими выходными токами, наличием выходов с тремя состояниями, значительной предельной емкостью нагрузки.

Большой недостаток оперативной памяти состоит в том, что информация, записанная в нее, исчезает при выключении источника питания. Поэтому часто используется дополнительный источник питания, который питает при выключении источника питания только микросхемы памяти. МС КР537РУ8, является энергонезависимой оперативной памятью, содержимое которой может легко перезаписываться, но не пропадает при выключении питания, как в ПЗУ.

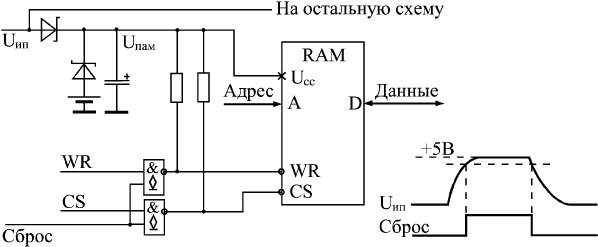

Схема энергонезависимой памяти (рисунок 11) довольно проста, хотя и имеет ряд неочевидных особенностей.

Рисунок 11 - Энергонезависимая оперативная память

Управляющие сигналы памяти – WR и – CS имеют активный низкий уровень, а при выключении питания все входные сигналы памяти, естественно, станут нулевыми. Это приведет к искажению записанной в память информации. Поэтому необходимо обеспечить, чтобы при выключении питания сигналы на входах –WR и –CS были пассивными, то есть имели уровень логической единицы. Для этого обычно используются логические элементы с выходами ОК, нагрузочные резисторы которых присоединяются не к пропадающему напряжению питания памяти Uип, а к сохраняющемуся напряжению питания памяти Uпам. Для получения напряжения Uпам используется простая схема на двух диодах, которая передает на выход Uпам напряжение источника питания Uип (если питание включено) или напряжение от гальванической батареи 3 – 4,5 В (если питание выключено).

Для большей гарантии от пропадания информации во время переходных процессов (при постепенном нарастании Uип и при постепенном его уменьшении) необходимо управлять прохождением сигналов WR и CS на память с помощью управляющего сигнала "Сброс". Этот сигнал равен нулю при напряжения Uип менее 4,7– 4,8 В и равен единице при нормальном напряжении Uип = 5 В (временная диаграмма приведена на рисунке). В результате такого решения память отключается от остальной схемы при недостаточном напряжении питания (сигналы -WR и –CS равны единице) и подключается к остальной схеме при нормальном напряжении питания.