5.2 Шинный формирователь к580ва86

Микросхема ШФ состоит из блока управления (элементы ИЛИ-НЕ А и В) и восьми функциональных блоков, каждый из которых содержит по два (1 и 2 ) разнонаправленных управляемых усилителя - формирователя с тремя устойчивыми состояниями. Блок управления обеспечивает выбор направления передачи и разрешение передачи за счет изменения логических уровней сигналов Т и ВК. Если на входе ВК высокий уровень лог. «1», то независимо от значения сигнала на выводе Т на выходах элементов А и В устанавливается низкий уровень лог. «0», и все усилители во всех разрядах оказываются в выключенном состоянии и передача через них блокируется в любом направлении. При комбинации ВК = 0 и Т = 1 на выводе элемента А образуется высокий уровень лог. «1» и усилители 1 (рисунок 19) во всех разрядах ШФ оказываются во включенном состоянии, а усилители 2 - в выключенном состоянии, так как на выходе элемента Б - низкий уровень лог. «0». В этом состоянии ШФ передает 8-разрядную информацию в направлении А > В. При комбинации ВК = 0 и Т = 0 на выходе элемента А установится низкий уровень лог. «0», а на выходе элемента Б - высокий уровень лог. «1», что приведет к выключенному состоянию усилителя 1 и к включенному состоянию усилителя 2. В этом состоянии возможна передача 8-разрядных данных в направлении В > А. Таким образом, схема ШФ обеспечивает двунаправленную передачу 8-разрядных данных в соответствии с таблицей 10.________________ Таблица 10 – Уровни сигналов К580ВА86

-

Уровни сигналов

Направление передачи байта данных

ВК

Т

0

1

канал А -> канал В

0

0

канал В -> канал А

1

безразлично

передача отсутствует

Рисунок 23 – Структурная схема К580ВА86 _______________________ ______Корпус ШФ имеет информационные выводы А0-А7 и В0-В7; вывод Т, логическое содержание которого определяет направление передачи информации, и вывод ВК (выборки кристалла). _______________________________________ _______Конструктивно ИС ШФ выполнена так, что нагрузочная способность канала В выше канала А. К выводам канала В допускается подключение токовой нагрузки I вых.0 = 32 мА, I вых.1 = -5 мА. Это обстоятельство следует учитывать при включении ШФ в качестве буфера шин: канал А целесообразно подключить к выводам микропроцессора.

5.3 Подключение микросхем, входящих в микропроцессорную систему, к шинам адреса и шинам данных

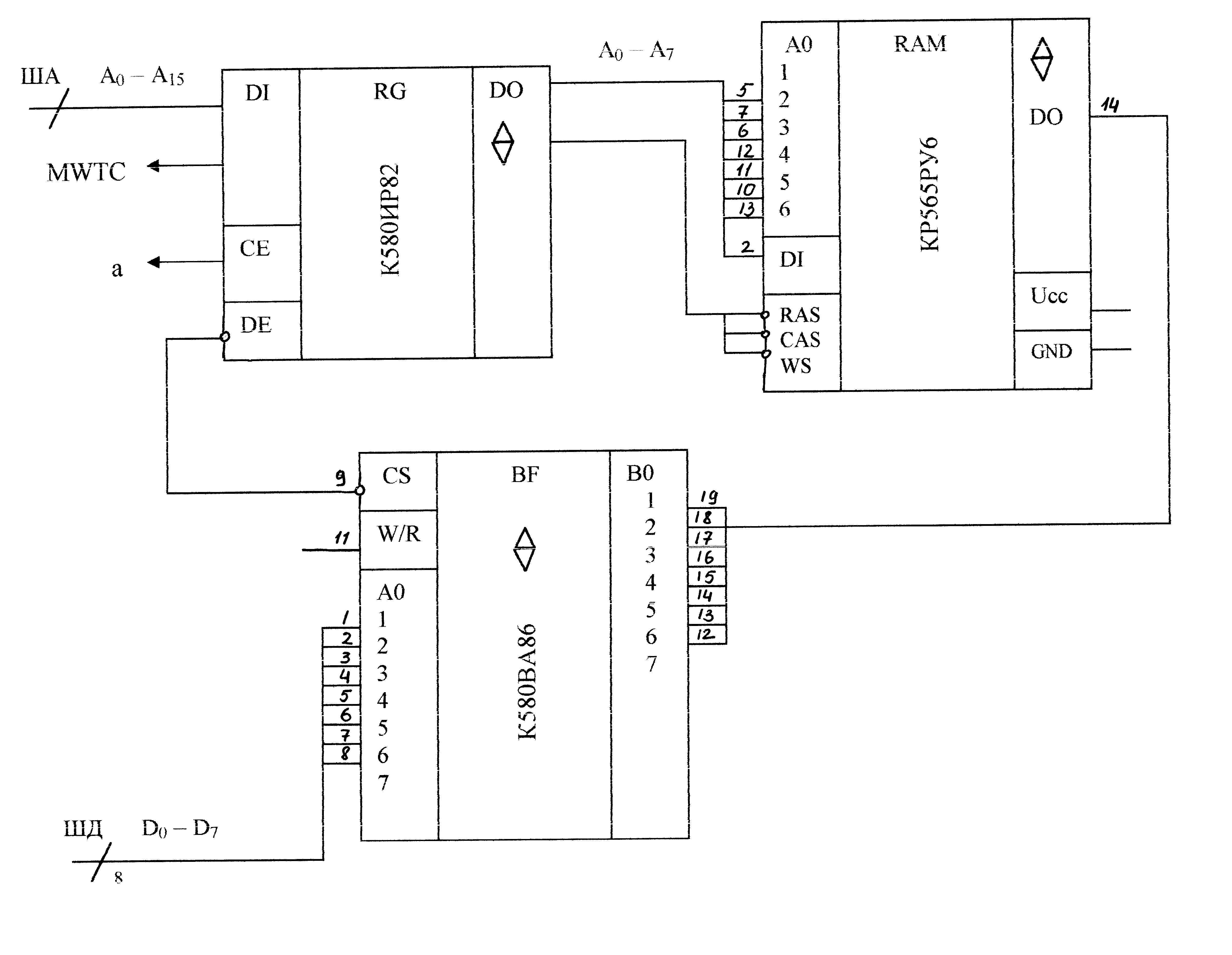

Подключение микросхем, входящих в микропроцессорную систему, к шинам адреса и данных осуществляется по средствам буферного регистра КР580ИР82 и шинного формирователя К580ВА86. _______________________ _______Подключение модулей ОЗУ и ПЗУ представлено на рисунке 24 и 25.

Рисунок

24 – Подключение ОЗУ к шинам адреса и

данных __

___

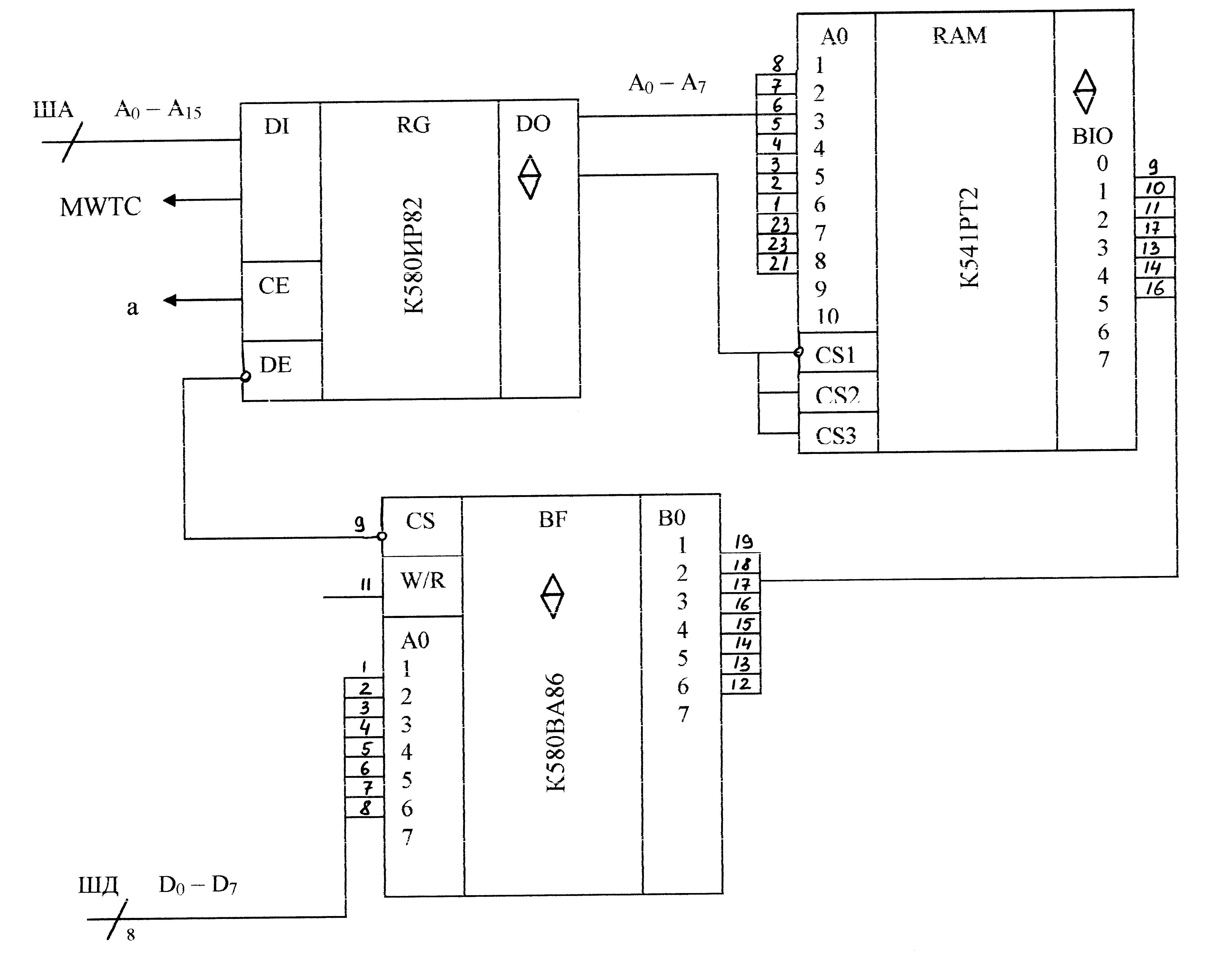

Рисунок 25 – Подключение ПЗУ к шинам адреса и данных

Подключение программируемого интервального таймера и программируемого контроллера прерываний представлены на рисунке 26 и 27.

Рисунок 26 - Подключение ПИТ к шинам адреса и данных _______

Рисунок 27 – Подключение ПКП к шинам адреса и данных

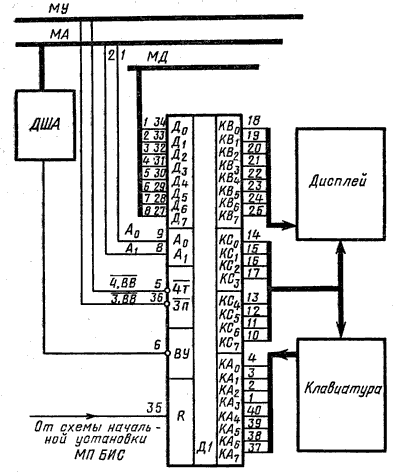

Подключение программируемого периферийного адаптера представлено на рисунке 28.

Рисунок 28 - Подключение программируемого периферийного адаптера к шинам адреса и данных

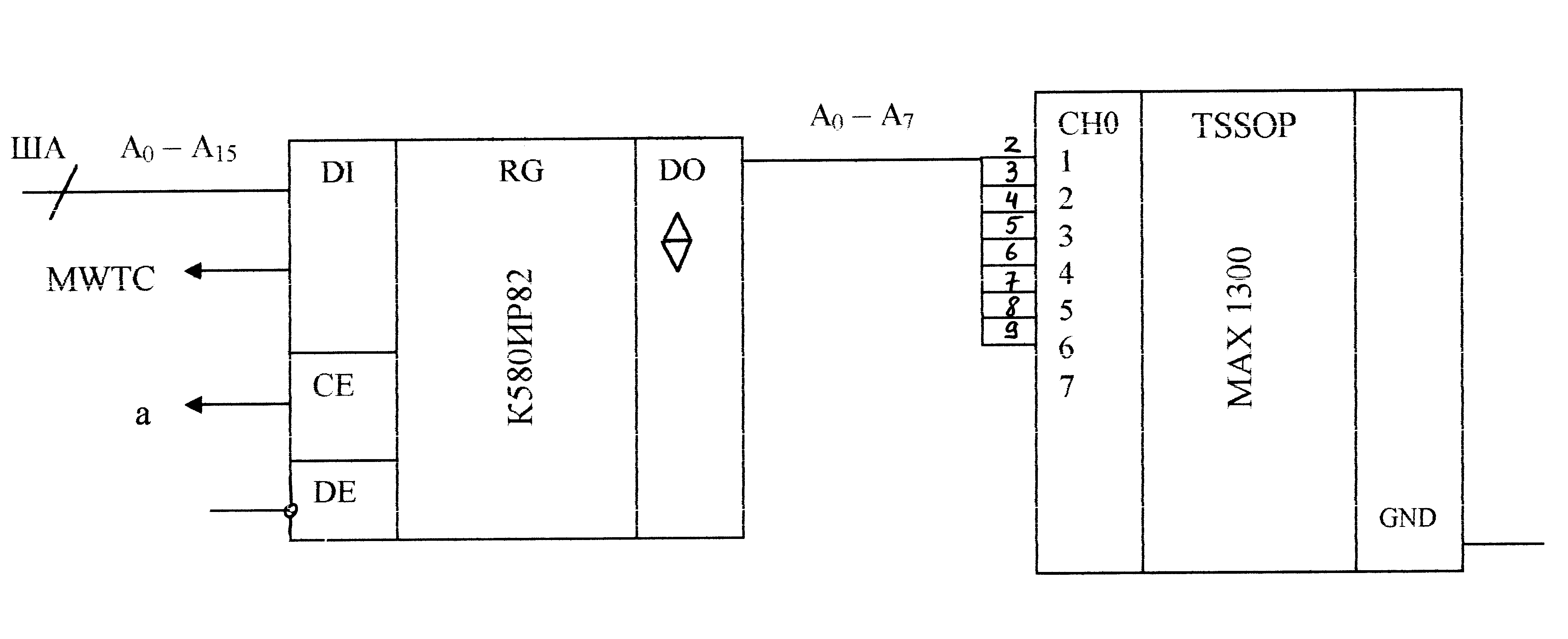

Подключение АЦП представлено на рисунке 29.

Рисунок 29 – Подключение АЦП