- •2.2 Генератор тактовых импульсов

- •2.2.2 Rc генератор. Когда не предъявляются требования к быстродействию и к точности по времени, отр кристалл, например pic16c84-rc, позволяет сэкономить деньги и реализовать простой rc.

- •3.1 Обзор регистров и озу

- •3.1.1Прямая адресация. Когда производится прямая 9-битная адресация, младшие 7 бит берутся как прямой адрес из кода операции, а два бита указателя страниц (rp1,rp0) из регистра статуса (03h).

- •3.2 Организация встроенного пзу

- •3.3 Данные в eeprom

- •4 Разрботка подсистемы ввода/вывода, прерываний, пдп

- •4.1Rtcc таймер/счетчик

- •4.2 Схема линии порта a

- •4.3 Схема линии порта b

4.3 Схема линии порта b

Порт В - это двунаправленный порт, шириной в восемь бит (адрес регистра 06h). Относящийся к порту В управляющий регистр TRISB расположен на первой странице регистров по адресу 86h. Если бит управляющего TRISB регистра имеет значение единица, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра защелки. У каждого вывода порта В имеется небольшая активная нагрузка (около 100мкА) на линию питания. Она автоматически отключается, если эта линия запрограммирована как вывод. Более того, управляющий бит RBPU OPTION<7> может отключить (RBPU=1) все нагрузки. Сброс при включении питания также отключает все нагрузки. Четыре линии порта В (RB<7:4>) имеют способность вызвать прерывание при изменении значения сигнала на любой из них. Если эти линии настроены на ввод, то они опрашиваются и защелкиваются в цикле чтения Q1. Новая величина входного сигнала сравнивается со старой в каждом командном цикле. При несовпадении значения сигнала на выводе и в защелке, генерируется высокий уровень. Выходы детекторов “несовпадений” RB4,RB5,RB6,RB7 объединяются по ИЛИ и генерируют прерывание RBIF (запоминаемое в INTCON<0>). Любая линия, настроенная как вывод, не участвует в этом сравнении. Прерывание может вывести кристалл из режима SLEEP. В подпрограмме обработки прерывания следует сбросить запрос прерывания одним из следующих способов:

1) Запретить прерывания при помощи обнуления бита RBIE INTCON<3>.

2) Прочитать порт В. Это завершит состояние сравнения.

3) Обнулить бит RBIF INTCON<0>.

Прерывание по несовпадению и программно устанавливаемые внутренние активные нагрузки на этих четырех линиях могут обеспечить простой интерфейс, например с клавиатурой, с выходом из режима SLEEP по нажатию клавиш.

Таблица 9 - Описание вывода порта

|

Название |

# |

Функция |

Другие функции |

|

PB0 |

0 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

Вход внешнего прерывания |

|

PB1 |

1 |

Порт ввода/вывода.Входные уровни ТТЛ. и внутренняя программируемая активная нагрузка. |

|

|

PB2 |

2 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

|

|

PB3 |

3 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

|

|

PB4 |

4 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

Прерывание при изменении |

|

PB5 |

5 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

Прерывание при изменении |

|

PB6 |

6 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

Прерывание при изменении |

|

PB7 |

7 |

Порт ввода/вывода.Входные уровни ТТЛ и внутренняя программируемая активная нагрузка. |

Прерывание при изменении |

4.4 Программируемый контроллер клавиатуры и индикации К580ВВ79

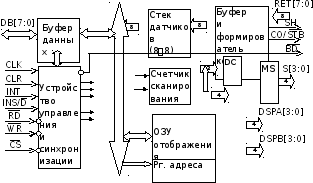

Контроллер К580ВВ79 предназначен для обслуживания сегментной индикации (максимально – два блока по 16 индикаторов) и матричной клавиатуры (до четырех матриц размером 8х8 клавиш) или линейки двоичных датчиков (2х8).

Контроллер включает в себя следующие блоки:

ОЗУ отображения объемом 16 8-разрядных слов, предназначенное для хранения кодов индицируемых символов;

ОЗУ датчиков (клавиатуры) объемом 8 8-разрядных слов с буферной схемой, предназначенное для размещения кодов нажатых клавиш или состояний линейки датчиков;

четырехразрядный счетчик сканирования с дешифратором состояния двух младших разрядов;

буфер данных для связи с МПС;

Рисунок 15 - Контроллер клавиатуры и индикации К580ВВ79

Таблица 12 - Внешние выводы

|

Название |

Функция |

|

DB[7:0] |

системная шина данных; |

|

CLK |

сигнал синхронизации (тактовая частота); |

|

CLR |

сброс (установка микросхемы в исходное состояние); |

|

INT |

выход запроса на прерывание; |

|

INS/D |

H-уровень определяет запись команды или чтение слова состояния; L-уровень определяет запись или чтение данных; |

|

RD |

вход строба чтения; |

|

WR |

вход строба записи; |

|

CS |

вход выбора микросхемы; |

|

RET[7:0] |

входы линий возврата для приема сигналов от датчиков |

|

SH |

вход сигнала идентификации для режима сканирования клавиатуры; |

|

CO/STB |

то же / строб записи состояния датчиков в стек датчиков; |

|

BD |

выход сигнала гашения индикаторов; |

|

S[3:0] |

выходы разрядов счетчика или выходы дешифратора младших разрядов; |

|

DSPA[3:0] |

выходы старших разрядов ОЗУ отображения; |

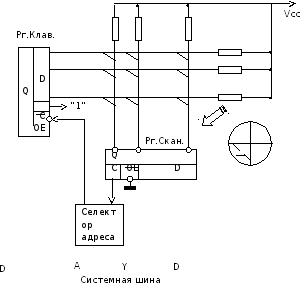

Рисунок 16 - Подключение контроллера К580ВВ79 в составе МПС

Контроллер позволяет обеспечить одновременное управление сегментными индикаторами и блоком матричной клавиатуры или линейкой датчиков. Схема подключения контроллера К580ВВ79 к МПС и блокам клавиатуры и индикации приведена на рисунке 16.

Работа контроллера осуществляется следующим образом. МПС загружает в ОЗУ отображения коды выводимых на индикацию символов и больше не обращается к контроллеру до тех пор, пока не потребуется изменить выводимую на индикацию информацию.

Контроллер инкрементирует счетчик (с частотой CLK/f, где f – один из 16 программируемых коэффициента деления) и синхронно выводит на линии DSP содержимое ячейки ОЗУ отображения, адрес которой соответствует значению счетчика. При работе с внешним дешифратором возможно управление 16 сегментными индикаторами при условии, что в ячейках ОЗУ отображения хранятся семисегментные коды символов.

Если хранить в ОЗУ отображения двоичные позиционные коды символов, то в каждой ячейке можно разместить коды двух символов и, при наличии внешних знакогенераторов, можно управлять 32 индикаторами.

4.5 Матричная клавиатура и сегментная индикация

Если клавиатура разрабатываемой МПС включает в себя большое число клавиш, целесообразно организовать ее в виде прямоугольной матрицы и идентифицировать клавишу номером строки и столбца матрицы.

На рисунке 17 показан один из возможных способов подключения матричной клавиатуры к МПС. Регистр сканирования Рг.Скан. является устройством вывода и содержит унитарный код номера столбца. При опросе клавиатуры в этот регистр последовательно записываются коды, содержащие единицу только в одном разряде. Если нажата клавиша (замкнут контакт) в столбце, соответствующем единичному разряду Рг.Скан., то (с учетом инверсии выхода этого регистра) на линии строки, соответствующей нажатой клавише, установится потенциал «логический 0», на остальных линиях строк матрицы сохранятся «логические 1». Состояние строк матрицы через регистр ввода Рг.Клав. вводится в процессор. Позиции «1» в Рг.Скан. и «0» в Рг.Клав. однозначно определяют положение нажатой клавиши в матрице клавиатуры. Длительность нажатия клавиши обычно не бывает менее 0,1 сек. Для надежной фиксации нажатия необходимо за это время просканировать все столбцы матрицы. Очевидно, это не предъявляет слишком высоких требований к быстродействию МПС.

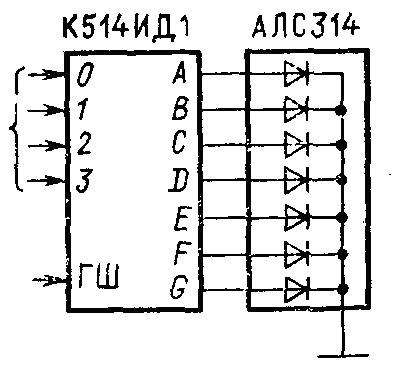

Для индикации символов (прежде всего – десятичных цифр) в простейших МПС часто используется сегментная индикация рисунок 18. В этом случае каждому разряду (знакоместу) ставится в соответствие группа сегментов, реализованных каждый как светодиод, электролюминесцентный, газоразрядный или жидкокристаллический индикатор, причем у индикаторов одной группы имеется, как правило, общий электрод (анод или катод). Каждый сегмент разряда можно включить независимо от другого при условии, что на общий электрод будет подан соответствующий потенциал. Количество сегментов разряда зависит от номенклатуры индицируемых символов, требуемого «качества» отображения и допустимых аппаратных затрат.

Рисунок 17 - Подключение матричной клавиатуры

Рисунок 18 - Светоизлучающие сегменты

В том случае, если в МПС надо отображать выводимую информацию только в шестнадцатеричных кодах, можно воспользоваться стандартными СИС преобразователей кодов (К514ИД1, К514ИД2, К155ИД8, К155ИД9). В том случае, если в МПС требуется отображение специальных знаков, вместо стандартных СИС необходимо использовать специально разработанные логические схемы на основе ИС (или ППЗУ). Широкому применению в простых управляющих МПС ССИ типов АЛС314А и АЛС324Б способствуют не только их дешевизна и простота монтажа, но и их электрическая совместимость с элементами серии ТТЛ.

Рисунок 19 – Устройство светодиодного индикатора

5 ОПИСАНИЕ СТРУКТРУЫ ПРОЦЕССА ОТЛАДКИ

МИКРОКОТРОЛЛЕРА

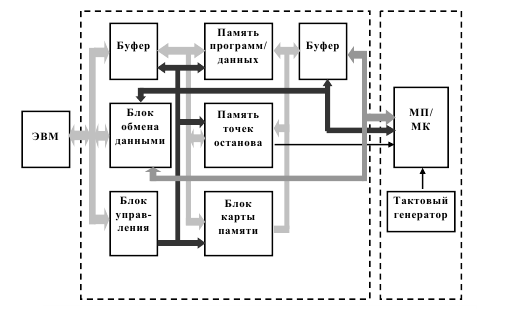

Внутрисхемный эмулятор — программно аппаратное средство, способное замещать собой эмулируемый процессор в реальной схеме. Внутрисхемный эмулятор — это наиболее мощное и универсальное отладочное средство. По сути дела, "хороший" внутрисхемный эмулятор делает процесс функционирования отлаживаемого контроллера прозрачным, т.е. легко контролируемым, произвольно управляемым и модифицируемым по воле разработчика.

Разрабатываемый внутрисхемный эмулятор предназначен для работы под управлением IBM PC — совместимого персонального компьютера. Эмулятор подключается к параллельному порту компьютера (порт должен поддерживать режим двунаправленной передачи данных ЕРР).

Структурная схема приведена на рисунке 20. Прибор состоит из двух модулей — базового и сменного. В состав базового модуля входит блок управления, память программ/данных, память точек останова, блок карты памяти, блок обмена данными, а также буферные элементы. Таким образом, в базовом модуле сосредоточены все необходимые для эффективной эмуляции блоки. Это позволяет значительно упростить схемотехнику и конструкцию сменных модулей. В состав сменного модуля входят лишь целевой микроконтроллер и генератор тактовых импульсов. В некоторых случаях могут понадобиться дополнительные буферные и логические элементы. Такое конструктивное решение позволяет производить отладку систем на базе широкого спектра микроконтроллеров, а также использовать прибор в качестве эмулятора ПЗУ (до 64 Кбайт).

В начале сеанса отладки происходит инициализация эмулятора. При этом разрешается доступ с ЭВМ к памяти программ/данных и точек останова, а также к блоку карты памяти. Пользователь вводит и редактирует программу, предназначенную для отладки, пользуясь средствами инструментальной ЭВМ. После редактирования, при помощи блока управления и буферного элемента, программа пользователя заносится в память программ/данных эмулятора. Туда же записывается системная программа -монитор, предназначенная для управления процессом обмена данными между инструментальной ЭВМ и отлаживаемой системой. В память точек останова заносится информация об установленных пользователем контрольных точках, в которых микроконтроллеру необходимо прервать выполнение программы и передать данные о состоянии ресурсов отлаживаемой системы на инструментальную ЭВМ. Блок карты памяти предназначен для хранения информации о распределении адресов памяти программ/данных между отлаживаемой системой и эмулятором.

После записи всей необходимой для эмуляции информации управление передается целевому микроконтроллеру. При этом буфер, связывающий устройство с инструментальной ЭВМ переводится в третье состояние, а другой буфер переводится из третьего состояния в активное. Таким образом, микроконтроллер получает доступ к памяти программ/данных и начинает выполнение программы пользователя.

Рисунок 20 – Структурная схема отладочного устройства

Программа пользователя может выполняться в одном из трех режимов - реального времени, пошаговом и с точками останова. При выполнении в режиме реального времени программа выполняется полностью адекватно целевой системе без эмулятора. Остановов в контрольных точках при этом не происходит (однако возможен останов выполнения по желанию пользователя). В режиме с точками останова пользовательская программа запускается аналогично режиму реального времени, однако разрешается отслеживание контрольных точек. По ходу выполнения микроконтроллер выставляет на внешнюю шину текущий адрес и, как только он совпадает с адресом точки останова, на микроконтроллер подается сигнал прерывания. Вектор прерывания настроен на переход к монитору. Под управлением монитора происходит обмен данными (в управляющую ЭВМ поступает информация о состоянии внутренних регистров и ячеек памяти отлаживаемой системы, при необходимости, ЭВМ их изменяет и записывает новые значения в отлаживаемую систему). В пошаговом режиме программа пользователя выполняется последовательно по одной команде. Между выполнением команд программы пользователя происходят вызовы монитора.

6 РАЗРАБОТКА АЛГОРИТМА РАБОТЫ МИКРОПРОЦЕССОРНОЙ

СИСТЕМЫ

Обработка

информации от цифровых датчиков и выдача

управляющего воздействия y1

производится путем ввода значений x1,

x2,

x3,

x4

и вычисления булевой функции f1(x1,

x2,

x3,

x4)=

.

.

При единичном значении f1 вырабатывается управляющий сигнал y1=1 длительностью t1=40 мкс.

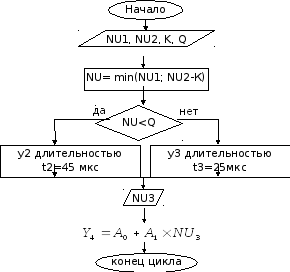

При обработке информации с аналоговых датчиков ПМ принимает коды NU1, NU2 с выходов АЦП и код константы К с регистра пульта управления. Далее вычисляется значение функции NU=f2(NU1,NU2, К)=min(NU1,NU2-К) и сравнивается с константой Q, хранящейся в ПЗУ. В зависимости от результатов сравнения вырабатывается (аналогично y1) один из двух двоичных управляющих сигналов y2 или y3 заданной длительности по следующему правилу: если NU<Q, то выдать y2 длительностью t2=25 мкс, иначе выдать y3 длительностью t3=40 мкс.

Далее формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3 и производится вычисление по формуле:

Значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

Все двоичные переменные и константы, участвующие в вычислениях: NU1, NU2, NU3, К, Q, A0, A1, Y4 рассматриваются как целые без знака.

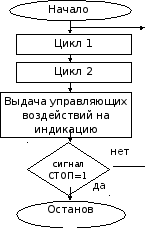

После выдачи всех управляющих воздействий проверяется состояние тумблера «СТОП» на пульте управления. Если СТОП=0, цикл управления начинается с начала, иначе выполняется процедура останова системы, включающая следующие действия: формируется сигнал установки системы в исходное состояние путем подачи на линию начальной установки интерфейса двух прямоугольных импульсов длительностью 30 мкс интервалом 30 мкс, выполняется команда процессора СТОП.

Блок-схема заданного цикла управления разбита на две части (рисунок 21 и 22), общая блок-схема представлена на рисунке 23.

Начало

x1, x2, x3, х4

y1=1

нет

да

y1 длительностью t1=40 мкс

конец цикла

Рисунок 21– Цикл 1 управляющей программы

В общем виде управляющая программа состоит из двух циклов, по результатам выполнения которых осуществляется выдача управляющих воздействий на индикацию. Управляющая программа выполняется до тех пор пока на пульте управления не будет включен тумблер «СТОП».

Цикл 1 управляющей

программы заключается в вводе в

центральный процессор значений сигналов

из цифровых датчиков, вычислении булевой

функции

.

Если по результатам вычисления получилось,

что управляющий сигнал стал равен 1, то

выдается управляющий сигнал длительностьюt1=40

мкс. Если же управляющий сигнал принял

значение 0, то булева функция

.

Если по результатам вычисления получилось,

что управляющий сигнал стал равен 1, то

выдается управляющий сигнал длительностьюt1=40

мкс. Если же управляющий сигнал принял

значение 0, то булева функция

вновь повторяется.

вновь повторяется.

Цикл 2 управляющей

программы заключается в воде в центральный

процессор двоичных кодов с выходов АЦП

и констант К и Q,

вычислении значения функции f2(NU1,

NU2,

К), по выражению NU=

min(NU1;

NU2-К).

Если по результатам вычисления получилось,

что NU<Q,

то вырабатывается управляющий сигнал

длительность t2=25

мкс, если же получилось что NU>Q,

то вырабатывается управляющий сигнал,

длительностью t3=40мкс.

Далее осуществляется ввод в центральный

процессор двоичного кода с выхода АЦП

NU3

и производиться вычисление функции

.

.

Цикл 2 изображен на рисунке 22.

Рисунок 22 – Цикл 2 управляющей программы

Рисунок 23 – Общая блок-схема программы

ЗАКЛЮЧЕНИЕ

В ходе курсового проектирования была создана управляющая МПС на базе однокристального микроконтроллера PIC16C84 , удовлетворяющая всем параметрам, заданным в техническом задании. Рассмотрена структура микроконтроллера, основные узлы, режимы работы и принципы программирования.

Разработана подсистема ПДП на базе контроллера КР580ВТ57, подсистема ввода-вывода и светодиодной индикации для вывода информации. Была разработана блок-схема алгоритма управляющей программы, по которой можно написать программу на языке Ассемблер для данного типа однокристальной микро-ЭВМ.

Была решена основная задача курсового проекта – развитие и закрепление навыков самостоятельной работы при решении конкретной задачи разработки микропроцессорной системы.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

1. Горбунов В.Л., Панфилов Д.И., Преснухин Д.Л. Микропроцессоры. Основы построения микроЭВМ. – М.: Высшая школа, 1986.

2. Новиков Ю.В. Основы микропроцессорной техники/ Ю.В. Новиков, П.К. Скоробогатов – М.: ИНТУИТ.РУ, 2003.

3. Алексенко А.Г. Проектирование радиоэлектронной аппаратуры намикропроцессорах/ А.Г. Алексенко, А.А. Галицын и др – М.: Энергоатомиздат, 1985. – 254 с.

4. Сташин В.В. Проектирование цифровых устройств на однокристальных микроконтроллерах/ В.В. Сташин, А.В. Урусов – М.: Энергоатомиздат, 1990. – 224 с.

5. www.microchip.com

ПРИЛОЖЕНИЕ А

(обязательное)

Графическая часть

1 Структурная схема микропроцессора PIC16C84 41

2 Контроллер прямого доступа к памяти КР580ВТ57 42

3 Разработка подсистемы, ввода/вывода, ПДП 43

4 Общая блок-схема программы 44

УИТС.161 ХХХ.105 ПЗ