- •2.2 Генератор тактовых импульсов

- •2.2.2 Rc генератор. Когда не предъявляются требования к быстродействию и к точности по времени, отр кристалл, например pic16c84-rc, позволяет сэкономить деньги и реализовать простой rc.

- •3.1 Обзор регистров и озу

- •3.1.1Прямая адресация. Когда производится прямая 9-битная адресация, младшие 7 бит берутся как прямой адрес из кода операции, а два бита указателя страниц (rp1,rp0) из регистра статуса (03h).

- •3.2 Организация встроенного пзу

- •3.3 Данные в eeprom

- •4 Разрботка подсистемы ввода/вывода, прерываний, пдп

- •4.1Rtcc таймер/счетчик

- •4.2 Схема линии порта a

- •4.3 Схема линии порта b

3.3 Данные в eeprom

EEPROM PIC16C84 рассчитан на ограниченное число циклов стирания/записи. Чтобы записать в программную память, кристалл должен быть переведен в специальный режим при котором на выводе /MCLR подается напряжение программирования Vрrg, а питание Vdd должно находиться в пределах 4.5 В ...5.5В. PIC16C84 непригоден для применений, в которых часто модифицируется программа. Запись в программную память осуществляется побитно, последовательно с использованием только двух выводов. Паспортное значение количества записей в программную память PIC16C84 равно 100(min) и 1000 (tiр), практически же микросхемы выдерживают несколько тысяч перезаписей. Число перезаписей памяти данных (64 байта) достанет 1000000.

При записи в память EEPROM, необходимо сначала записать требуемый адрес в EEADR регистр и данные в EEDATA регистр. Затем выполнить специальную последовательность команд, производящую непосредственную запись:

movlv 55h

movwf EECON2

movlv AAh

movwf EECON2

bsf EECON1,WR ;установить WR бит, начать запись.

Таблица 6 - Управляющие регистры для EEPROM

|

Название |

Функция |

Адрес |

Значение после включения |

|

EEDATA |

EEPROM регистр данных |

08h |

XXXX XXXX |

|

EEADR |

EEPROM регистр адреса |

09h |

XXXX XXXX |

|

EECON1 |

EEPROM 1 управляющий регистр |

88h |

0000 X000 |

|

EECON2 |

EEPROM 2 управляющий регистр |

89h |

- |

3.4 Контроллер прямого доступа к памяти КР580ВТ57

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 предназначен для организации высокоскоростного обмена данными между памятью и внешними устройствами, выполняемого по инициативе внешнего устройства.

Рисунок 10 – Структурная схема контроллера прямого доступа к памяти КР580ВТ57

Упрощенная структурная схема КПДП приведена на рисунке 10. В состав БИС входят: двунаправленный двустабильный буфер данных (ВD), предназначенный для обмена информацией между МП и КПДП; схема управления чтением/записью (RWCU), адресующая внутренние регистры КПДП и управляющая обменом по шине D(7-0); блок управления (СU) и обеспечивающий последовательность операций; блок управления приоритетами (РСU), обеспечивающий определенный порядок обслуживания запросов внешних устройств; четыре канала прямого доступа (СН0 – СН3), каждый из которых содержит регистр адреса ячейки памяти, с которой производится обмен, и счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена.

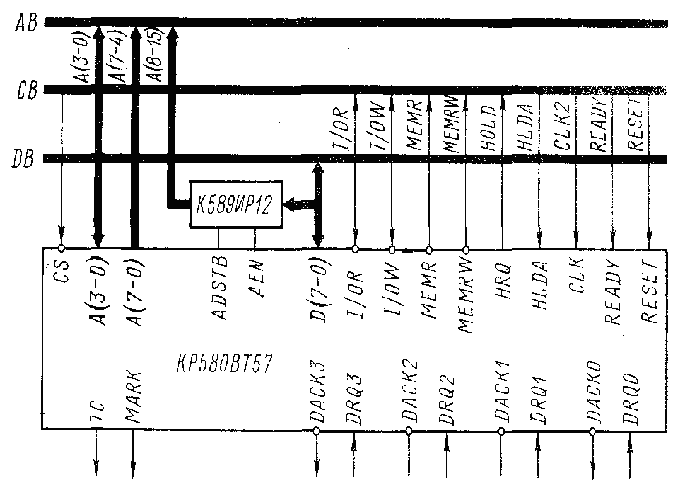

Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12 показана на рисунке 11.

Рисунок 11 – Схема подключения КПДП к системной шине с использованием буферного регистра К589ИР12

Основные электрические параметры микросхемы КР580ВТ57 при температуре окружающей среды + 25 + 10°С приведены ниже:

Выходное напряжение логического нуля UOL, В < 0,45

Выходное напряжение логической единицы UOH, В > 2,4

Ток потребления IСС, мА < 100

Ток утечки на входах IIL, мкА < 1,5

Ток утечки на управляемых выводах IОL, мкА –1,5...1

Таблица 7– Описание выводов контроллера прямого доступа к памяти

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

D(7–0) |

Д(7–0) |

Входы/выходы данных для обмена с МП |

Вход /выход |

H-1,L-0 |

|

|

Чтение ввода /вывода |

Чтение ввода/вывода – двунаправленный тристабильный вход /выход; вх. сигнал L – чтение |

Вход /выход |

L-1, H-0, z |

|

|

Запись ввода /вывода |

Запись ввода/вывода — двунаправленный тристабильный вход/выход; входной сигнал L- разрешает программирование КПДП |

Вход /выход |

L-1, H-0, z |

|

CLK |

синхро |

Вход тактовых импульсов |

Вход |

H-1,L-0 |

|

RESET |

сброс |

Вход установки 0 |

Вход |

H-1,L-0 |

|

A(3-0) |

A(3-0) |

Двунаправленные тристабильные ад. выводы |

|

H-1,L-0 |

|

|

КС |

Выбор микросхемы |

|

L-1,H-0 |

|

A(7-4) |

A(7-4) |

Тристабильные адресные выходы |

Выход |

H-1,L-0 |

|

READY |

Готов |

Готовность – входной сигнал Н- готовность к обмену |

Вход |

H-1 H-1 |

|

HRQ |

ЗЗ |

Запрос захвата – выходной сигнал Н- запрос о доступе КПДП |

Выход |

H-1,L-0 |

|

HLDA |

ПЗ |

Подтверждение захвата – входной сигнал Н- доступа к СШ |

Вход |

H-1,L-0 |

|

|

Чтение из памяти |

Чтение из памяти – тристабильный выход; чтение из ячейки памяти |

Выход |

L-1, H-0, z |

|

|

Запись в память |

Запись в память – тристабильный выход; L- запись в ячейку |

Выход |

L-1, H-0, z |

|

1 |

2 |

3 |

4 |

5 |

Продолжение таблицы 7

|

1 |

2 |

3 |

4 |

5 |

|

Обозначение |

Обозначение (рус) |

Функциональное назначение выводов |

Тип вывода |

Состояние |

|

ADSTB |

Ад строба |

Строб адреса – сигнал Н- нахождение D(7 – 0) старшего байта адреса |

Выход |

H-1,L-0 |

|

TC |

КС |

Конец счета – сигнал Н- выполнение последнего цикла |

Выход |

H-1,L-0 |

|

MARK |

Маркер |

Маркер — сигнал Н-ур. выполнить число циклов обмена, кратное 128 |

Вход |

H-1,L-0 |

|

DRQ3-DRQ0 |

СН3-СН0 |

Запросы ПДП каналов СН3-0; сигнал Н – УКазывает на запрос от ВУ |

Вход |

H-1,L-0 |

|

DACK3-DACK0 |

СН3-СН0 |

Подтверждение запросов ПДП каналов СН3-СН0 |

Ввыход |

L-1,H-0 |

|

UСС |

Uп |

Напряжение питания ( + 5 В) |

Вход |

|

|

GND |

ОБЩ |

Напряжение питания (0 В) |

Вход |

|