- •Опорные напряжения ацп (vrl и vrh).На эти два вывода подаются напряжения, относительно которых происходят измерения в системе ацп.

- •2.3 Программируемый таймер

- •2.4 Счетчик

- •2.5 Прерывания реального времени

- •2.6 Счетчик импульсов

- •2.7 Прерывания

- •2.8 Пзу

- •2.9 Озу

- •2.10 Регистры цп

- •Программный счетчик pc. Программный счетчик является 16-разрядным регистром, содержащим адрес следующей выполняемой команды.

- •Основные характеристики системы sci

- •Характеристики приемника

- •Характеристики передатчика

- •3.2 Последовательный периферийный интерфейс

- •Описание сигналов spi.

- •Функциональное описание.

- •3.3 Аналого-цифровой преобразователь

- •3.4 Сигналы портов

Описание сигналов spi.

В последующих параграфах обсуждаются четыре основных сигнала SPI (MISO, MOSI, SCK и SS). Каждый сигнал описан как при работе в режиме ведущего, так и при работе в режиме ведомого устройства.

Все выходные линии, используемые SPI должны иметь установленными соответствующие биты регистра направления. Если какой-либо бит сброшен, то соответствующая линия связи отсоединяется от логики SPI и становится линией ввода общего назначения. Все входные линии SPI функционируют как входы, независимо от состояния соответствующих битов регистра направления.

Функциональное описание.

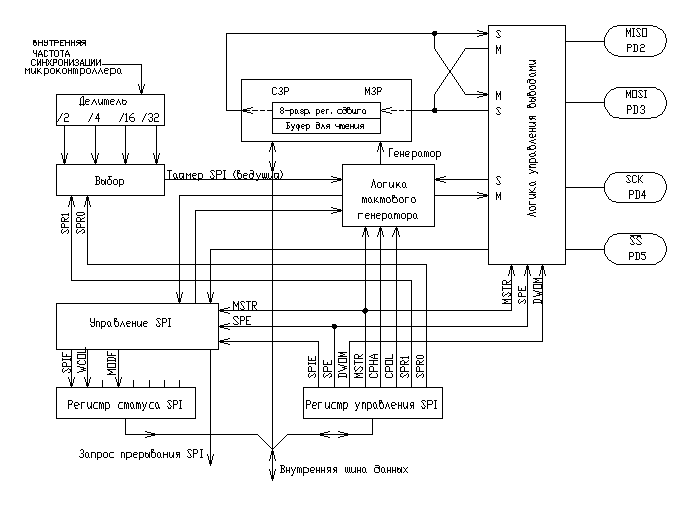

На рисунке 5 представлена блок-схема системы последовательного периферийного интерфейса. Когда ведущее устройство передает данные ведомому по линии MOSI, ведомое устройство отвечает посылкой данных ведомому по линии MISO. Весь этот процесс и составляет дуплексный обмен данными между двумя устройствами с синхронизацией одним и тем же сигналом. Таким образом, передаваемый байт замещается принимаемым байтом и поэтому не требуются отдельные флаги, сигнализирующие об очистке передатчика и заполнении приемника. Для индикации завершения обмена данными используется один бит SPIF.

Рисунок 5 - Блок-схема SPI

Последовательный периферийный интерфейс является дважды буферированным на чтение, но не запись. Если выполняется запись данных во время передачи данных, то текущая передача не прерывается, а сама запись игнорируется. Такое событие вызывает установку флага ошибки записи WCOL регистра SPSR. После сдвига данных устанавливается флаг SPIF того же регистра SPSR.

В режиме ведущего устройства вывод SCK является выходом. В свободном состоянии он имеет низкий или высокий уровень, в зависимости от состояния бита CPOL регистра SPCR. После записи в сдвиговый регистр формируются восемь тактовых импульсов синхронизации для сдвига восьми бит данных, после чего линия SCK снова принимает в свободное состояние.

В режиме ведомого устройства логические схемы формируют низкий уровень на выводе SS/ и формируют тактовые импульсы на выводе SCK. Таким образом, ведомое устройство синхронизируется по ведущему. Данные последовательно посылаются ведущим устройством по линии MOSI и считываются в регистр сдвига. После полной загрузки сдвигового регистра данные параллельно перемещаются в буфер чтения. В течение цикла записи данные записываются в сдвиговый регистр, после чего ведомое устройство ждет сигнала синхронизации от ведущего для сдвига данных по линии MISO.

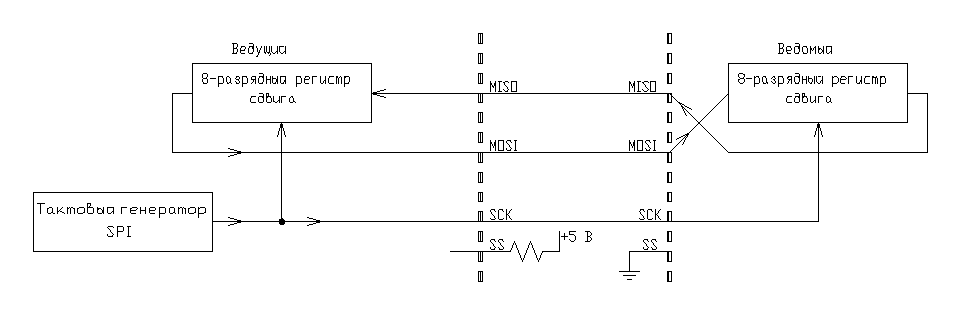

На рисунке 6 показано взаимное соединение выводов MOSI, MISO, SCK и SS ведущего и ведомого устройств.

Рисунок 6 - Соединение ведущий-ведомый при использовании SPI

Поскольку линии порта D (и соответственно линии SPI) могут работать в режиме с открытым стоком и таким образом позволять соединение “монтажное ИЛИ”, система SPI может быть построена различными способами. Система, в которой происходит единственный двунаправленный обмен данными может просто использовать соединение выводов MISO и MOSI. Но так как микроконтроллер MC68HC11E9 может выборочно запрещать свой выход MISO, то возможны другие виды протокола обмена.