- •Грицюк с. Н.____________ «_____»____________2006 г.

- •Введение

- •1 АналиЗтехнического задания

- •2 Разработка процессорного модуля

- •2.2 Вспомогательные интерфейсные микросхемы

- •Разработка последовательного интерфейса

- •3 Разработка подсистемы памяти

- •3.1 Оперативное запоминающее устройство к134ру6

- •3.2 Постоянное запоминающее устройство к556рт5

- •4 Разработка подсистем

- •4.1 Разработка подсистемы ввода/вывода

- •4.2 Разработка контролера прерываний

- •4.3 Разработка контроллера прямого доступа к памяти

- •4.4 Разработка программируемого таймера

- •4.5 Разработка ацп

- •5. Разработка принципиальной схемы микро-эвм

3 Разработка подсистемы памяти

3.1 Оперативное запоминающее устройство к134ру6

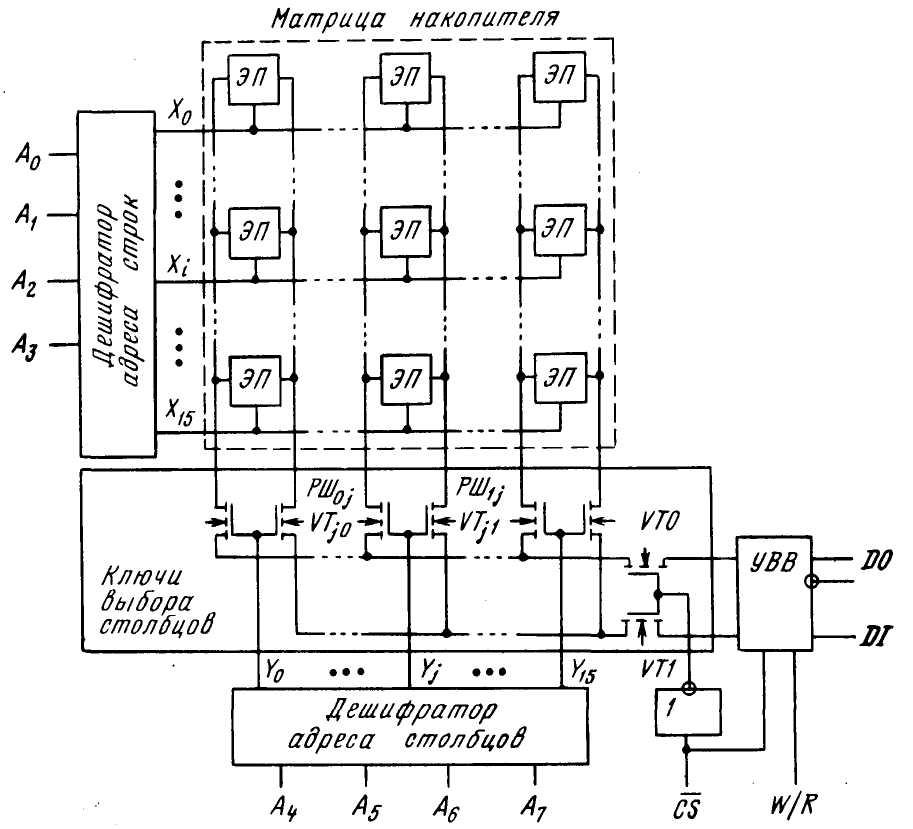

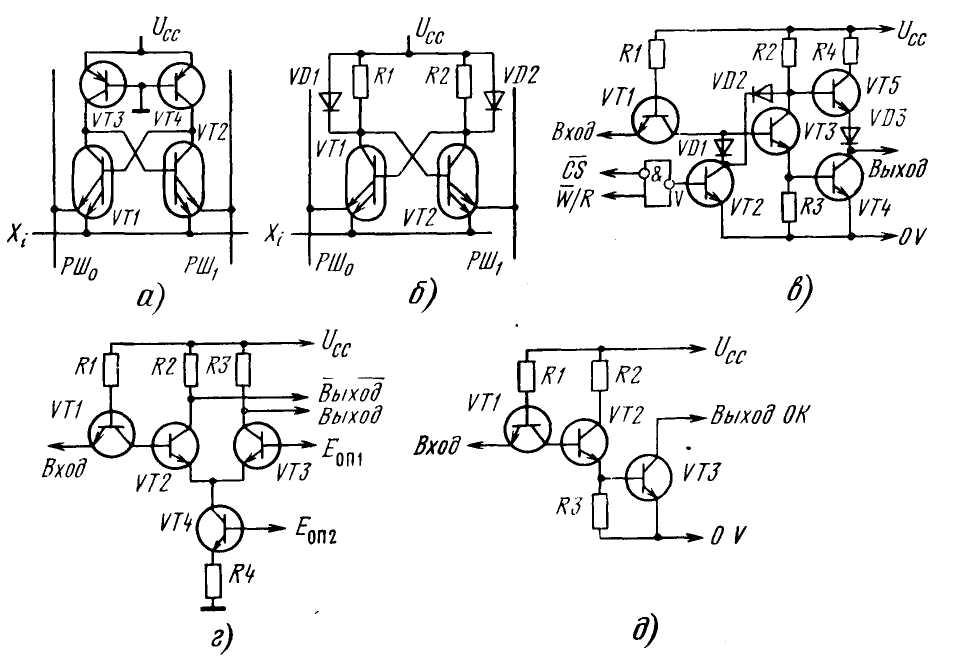

Техника БИС развивается, в первую очередь, по пути повышения степени интеграции цифровых схем с регулярной структурой. Наибольшего успеха в этом направлении достигнуто для БИС с МОП структурами. Различают статические ОЗУ на n-МОП - структурах и к-МОП - структурах. Структура микросхемы статического ОЗУ с одноразрядной организацией представлена на рисунке 7.

Рисунок 7 – Структура микросхемы статического ОЗУ с одноразрядной организацией

Микросхема К134РУ6 емкостью 1К×1 бит получена по ИИЛ-ТТЛ-технологии. Ее особенность заключается в том, что выход построен по схеме с открытым коллектором ОК (рис.8).

Рисунок 8 – Инвертор с открытым коллекторным выходом

Наличие такого в ыхода

не позволяет объединять информационные

входы и выходы. При соединении нескольких

микросхем по выходам можно использовать

схему «монтажного ИЛИ» с подключением

к точке соединения источника питания

через внешний токоограничивающий

резистор. Для расчета его сопротивления

необходимо учитывать прежде всего

значение выходного тока в состоянии

логического 0, равное 16 мА. При хранении

данных потребляемая мощность

снижается вдвое.

ыхода

не позволяет объединять информационные

входы и выходы. При соединении нескольких

микросхем по выходам можно использовать

схему «монтажного ИЛИ» с подключением

к точке соединения источника питания

через внешний токоограничивающий

резистор. Для расчета его сопротивления

необходимо учитывать прежде всего

значение выходного тока в состоянии

логического 0, равное 16 мА. При хранении

данных потребляемая мощность

снижается вдвое.

Таблица 1 - Характеристики ОЗУ серии К134

|

Серия |

Емкость, бит |

tц , нс |

Uпит, В |

Рпот, Вт |

Выходные уровни |

Технологии |

|

134 |

1К×1 |

1000 |

5 |

0,6 |

ТТЛ-ОК |

ИИЛ-ТТЛ |

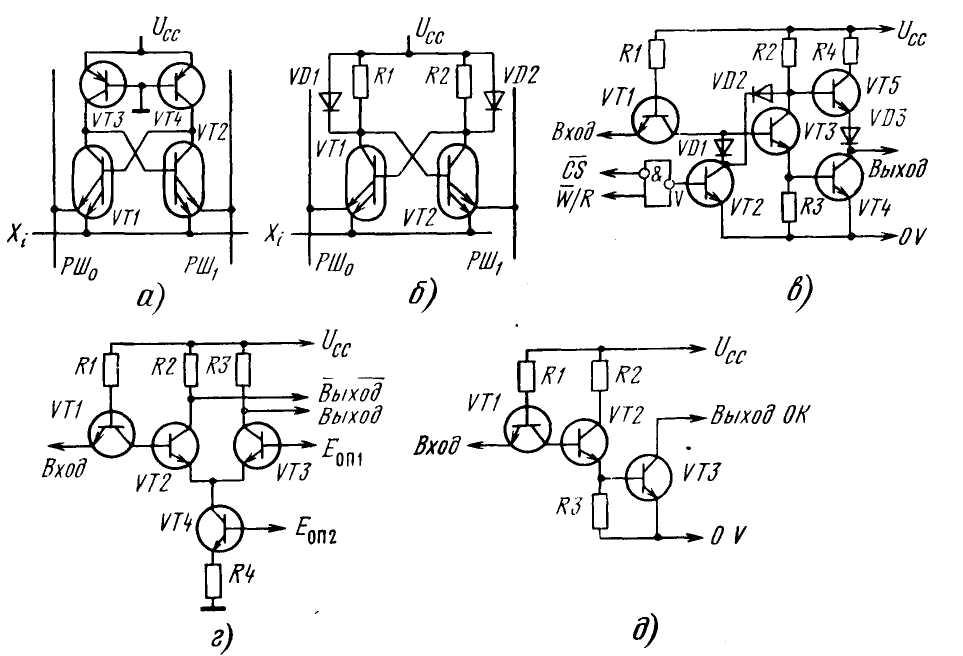

В качестве элемента памяти использован статический триггер на четырех транзисторах, два из которых, VT3 иVT4, являются инжекторами транзисторовVT2 иVT1 соответственно. Двухэмиттерными транзисторами управляют сигналы адресной шиныXiи разрядных шин РШ0, РШ1. ПриXi=0 триггер находится в режиме хранения, так как при этом фиксируется состояние плеч триггера. ПриXi=1 оба эмиттерных перехода закрываются и состояние триггера зависит от потенциалов разрядных шин: при низком потенциале шин в режиме считывания в одну из них потечет ток, а именно в ту, со стороны которой транзистор открыт.

При записи по шинам в форме парафазного

сигнала PШ1=D,PШ0=Dк плечам триггера подводится информация.

Асимметрия в потенциалах шин вызовет

переключение триггера в состояние,

определяемое потенциалами шин: например,

приPШ1= 0, РШ0=1

(запись 0) откроется VT2,

через него в шину потечет ток инжектораVT4, а транзисторVT1

закроется. При записи 1 состояния

транзисторов изменятся на обратные.

VT2,

через него в шину потечет ток инжектораVT4, а транзисторVT1

закроется. При записи 1 состояния

транзисторов изменятся на обратные.

Выходные и входные цепи выполнены на элементах ТТЛ, поскольку низкопороговые функциональные узлы ИИЛ имеют низкую помехоустойчивость и, кроме того, не согласованы по уровням напряжения с элементами других типов логики. Вариант выходного каскада с тремя состояниями (рис. 9) выполнен по схеме ТТЛ сложного инвертора с дополнительными элементами VD1,VD2,VT2, необходимыми для обеспечения третьего состояния выхода.

Рисунок 9 – Инвертор с выходом с тремя состояниями

Управляющий сигнал Vзависит от внешних сигналовCSиW/R, воздействуя на вход транзистораVT2, закрывает его приV= 0 или открывает приV=l. В третьем состоянии выход находится приV=l, когда открытый транзисторVT2 шунтирует входы и закрывает транзисторыVT5 иVT3, а значит, иVT4.