3 Обоснование выбора микропроцессора

Микроконтроллеры серии AT89 фирмы Atmel, совместные с MCS-51 с системой команд и архитектурой MCS-51 представлять нет необходимости. Они широко распространены, множество фирм выпускают их модификацию и программное обеспечение для них. Выпускает такие микроконтроллеры и фирма Atmel. Отличительной особенностью этих микроконтроллеров является применение FLASH- памяти программ. Эта особенность позволяет практически мгновенно изменять программный код микроконтроллера, что существенно сокращает цикл разработки. Микроконтроллеры в корпусе с 40/44 выводами полностью совместимы по выводам с контроллерами 80С51 и обеспечивают возможность использования наработанных программ и прямой замены. FLASH- память программ делает также возможным дистанционное изменение программного кода встроенных микроконтроллеров непосредственно у заказчика. Микроконтроллеры серии AT89 имеют следующие основные особенности:

-8-разрядный процессор, оптимизированный для приложения управления;

-обширные возможности побитовой обработки;

-встроенная FLASH- память программ;

-встроенная оперативная память;

-двунаправленные и индивидуально адресуемые линии ввода-вывода;

-один или несколько 16-разрядных таймеров/счетчиков;

-полнодуплексный UART;

-разветвленная структура прерываний;

-встроенный тактовый генератор;

-экономичные режимы: IDLE и POWER DOWN;

-встроенная память EEPROM (AT89S);

-последовательный интерфейс SPI (AT89S);

-сторожевой таймер (AT89S);

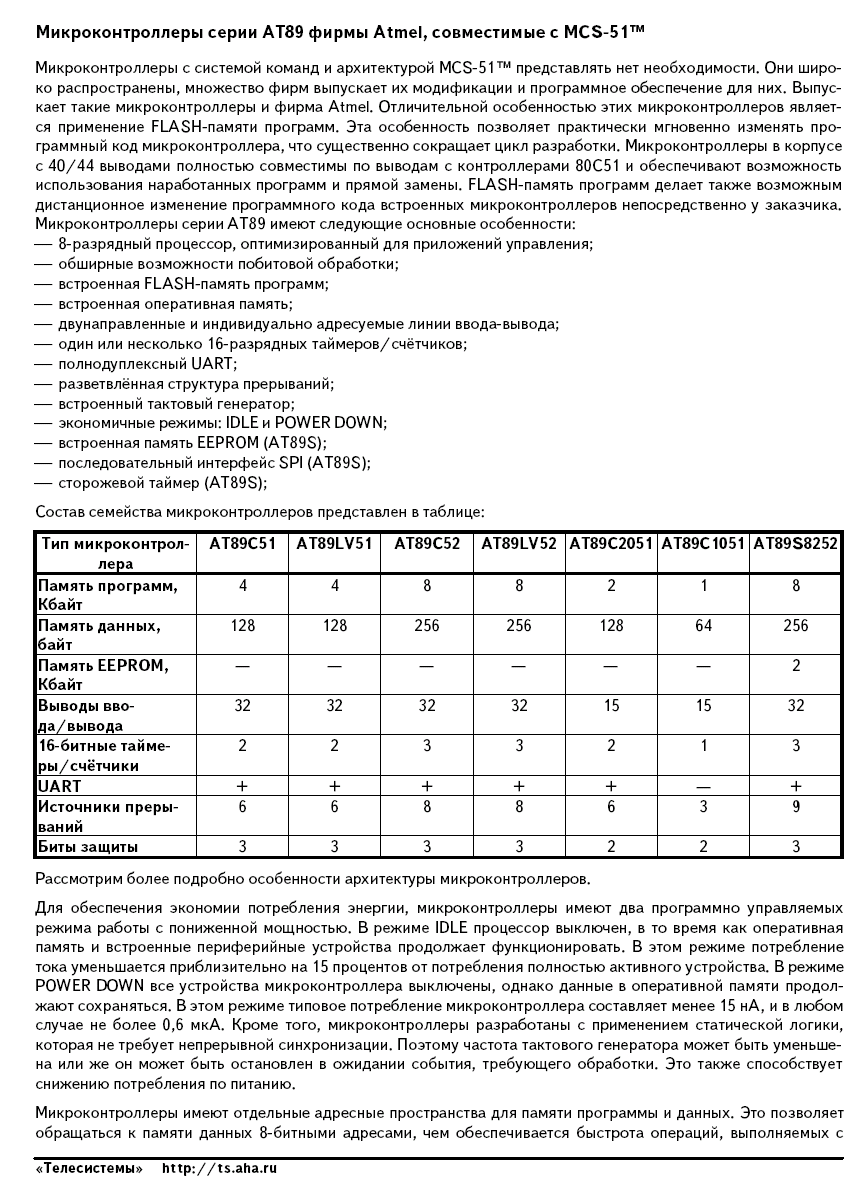

Состав

семейства микроконтроллеров представлен

в таблице 1.

Состав

семейства микроконтроллеров представлен

в таблице 1.

Таблица 1- Состав семейства микроконтроллеров.

Из таблицы 1 видно, что наш микроконтроллер AT89C2051 не самый лучший из всех перечисленных но, несмотря на это он в полной мере может обеспечить требуемое управление эхолотом по заданным критериям. Также микроконтроллер АТ89С2051 является отечественным аналогом КР1816ВЕ48, но применение микроконтроллера КР1816ВЕ48 с внешней памятью программ нецелесообразно, так как это существенно увеличит потребляемый ток и габариты прибора.

Таким образом, для реализации микропроцессорного устройства управления эхолотом был выбран микроконтроллер АТ89С2051.

4 Описание микропроцессора

Микроконтроллер АТ89С2051 ориентирован на использование в качестве встроенного управляющего контроллера. Потребление в активном режиме на частоте 12 МГц не превышает 15 мА и 5,5 мА при напряжении питания 6 В и 3 В, соответственно. При тех же условиях в пассивном режиме, при котором остановлено ЦПУ, но система прерываний, ОЗУ, таймер/счетчик событий и последовательный порт остаются активными, потребление не превышает 5 мА и 1мА. В стоповом режиме потребление не превышает 100 мкА и 20 мкА при напряжении питания 6 В и 3 В, соответственно.

Основные характеристики:

- Совместимость с MCS-51 - 2 Килобайта Перепрограммируемой Флеш-Памяти - Допускается: 1000 циклов записи/чтения - Диапазон напряжения питания от 2.7В до 6В - Полностатическая система: тактовая частота от 0 Гц от 24 MHz - Двухуровневая блокировка памяти программ - 128 x 8-разрядная внутреннее ОЗУ - 15 программируемых линий ввода/вывода - Два 16-разрядных Таймера/счетчика - Шесть источников прерывания - Программируемый последовательный UART Канал - Прямое подключение светодиодного дисплея - Встроенный аналоговый компаратор - Малая мощность пассивного режима и режим пониженной мощности

AT89C2051

- низковольтная, быстродействующая CMOS

8-разрядная микро ЭВМ с 2 Кб электрически

стираемой флеш ПЗУ (PEROM). Устройство

изготовлено, с использованием технологии

энергонезависимой памяти высокой

плотности фирмы Atmel и совместимо с

промышленным стандартом MCS-51 по системе

команд и назначению контактов. Соединение

универсального 8- разрядного

процессора с флэш-памятью на одном

кристалле, делает Atmel AT89C2051 мощной микро

ЭВМ, которая обеспечивает гибкое и

недорогое решение многих прикладных

задач управления. AT89C2051 обеспечивает

следующие стандартные возможности: 2

Кб флеш памяти, 128 байтов ОЗУ, 15 линий

ввода/вывода, два 16-разрядных

таймера/делителя, пяти векторная, двух

уровневая система прерываний,

полно/дуплексный последовательный

порт, прецизионный аналоговый компаратор,

встроенный осциллятор и тактовый

генератор. Кроме того, в микросхеме

AT89C2051 применяется технология со

статической логикой корректно работающая

при снижении частоты тактового генератора

вплоть до нулевого значения и поддерживает

два программно выбираемых режима

экономии мощности. Неактивный Режим

приостанавливает работу ЦП. При этом

выход из режима малого потребления

может происходить при запросах то ОЗУ,

таймера/делителя, последовательного

порта или системы прерывания. При

принудительном переходе в режим

пониженного потребления мощности

сохраняется содержимое ОЗУ, но внутренний

генератор микросхемы, останавливается,

отключая все другие функции чипа до

последующего аппаратного сброса.

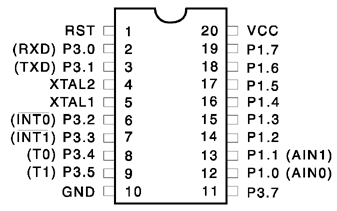

Циколевка корпуса представлена на

рисунке 5.

разрядного

процессора с флэш-памятью на одном

кристалле, делает Atmel AT89C2051 мощной микро

ЭВМ, которая обеспечивает гибкое и

недорогое решение многих прикладных

задач управления. AT89C2051 обеспечивает

следующие стандартные возможности: 2

Кб флеш памяти, 128 байтов ОЗУ, 15 линий

ввода/вывода, два 16-разрядных

таймера/делителя, пяти векторная, двух

уровневая система прерываний,

полно/дуплексный последовательный

порт, прецизионный аналоговый компаратор,

встроенный осциллятор и тактовый

генератор. Кроме того, в микросхеме

AT89C2051 применяется технология со

статической логикой корректно работающая

при снижении частоты тактового генератора

вплоть до нулевого значения и поддерживает

два программно выбираемых режима

экономии мощности. Неактивный Режим

приостанавливает работу ЦП. При этом

выход из режима малого потребления

может происходить при запросах то ОЗУ,

таймера/делителя, последовательного

порта или системы прерывания. При

принудительном переходе в режим

пониженного потребления мощности

сохраняется содержимое ОЗУ, но внутренний

генератор микросхемы, останавливается,

отключая все другие функции чипа до

последующего аппаратного сброса.

Циколевка корпуса представлена на

рисунке 5.

Рисунок 5- Циколевка корпуса.

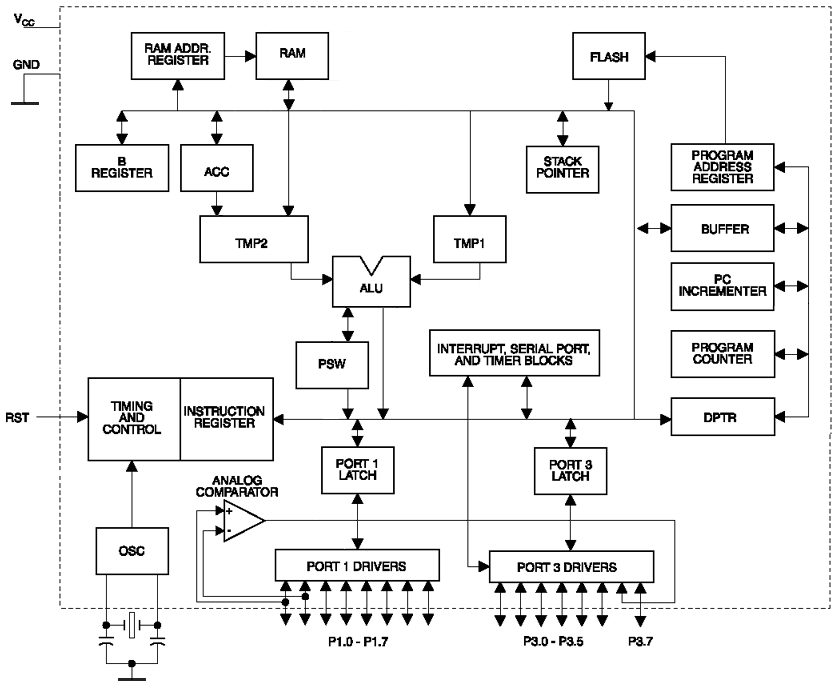

Блок

- схема внутреннего устройства контроллера

изображена на рисунке 6.

Блок

- схема внутреннего устройства контроллера

изображена на рисунке 6.

Рисунок 6- Блок - схема внутреннего устройства контроллера.

Назначение выводов: VCC-напряжение питания; GND-Общий провод; Порт P1-8-разрядный двунаправленный порт ввода/вывода. Порт содержит

линии

P1.2 к P1.7, имеющие внутренние нагрузочные

резисторы. P1.0 и P1.1 требуют внешней

нагрузки. P1.0 и P1.1 также являются

положительным (AIN0) и отрицательным

(AIN1) входами встроенного аналогового

компаратора.

Все выводы Порта P1

содержат буферы вывода, которые могут

выдерживать нагрузку до 20 мA и могут

непосредственно управлять светодиодными

дисплеями. Когда на какой-либо выход

Порта P1 подана логическая 1,они могут

использоваться как входы. Когда выводы

P1.2 к P1.7 используются, как входы и извне

на них подан сигнал низкого уровня, из

них будет вытекать ток от источника

(IIL) благодаря внутренним нагрузочным

резисторам.

Порт P1 также получает

данные кода в процессе программирования

и проверки ПЗУ программ;

линии

P1.2 к P1.7, имеющие внутренние нагрузочные

резисторы. P1.0 и P1.1 требуют внешней

нагрузки. P1.0 и P1.1 также являются

положительным (AIN0) и отрицательным

(AIN1) входами встроенного аналогового

компаратора.

Все выводы Порта P1

содержат буферы вывода, которые могут

выдерживать нагрузку до 20 мA и могут

непосредственно управлять светодиодными

дисплеями. Когда на какой-либо выход

Порта P1 подана логическая 1,они могут

использоваться как входы. Когда выводы

P1.2 к P1.7 используются, как входы и извне

на них подан сигнал низкого уровня, из

них будет вытекать ток от источника

(IIL) благодаря внутренним нагрузочным

резисторам.

Порт P1 также получает

данные кода в процессе программирования

и проверки ПЗУ программ;

Порт P3-Порт P3 имеет семь двунаправленных линий ввода/вывода со внутренней нагрузкой (P3.0 - P3.5, P3.7). Линия P3.6 постоянно подсоединена к выходу встроенного компаратора и не выходит на внешние выводы, как остальные линии ввода/вывода. Буферы Порта 3 могут нагружаться сигналом до 20 mA. Когда на любую из линий Порта 3 подан сигнал логической единицы, напряжение на этих выводах будет высоким (благодаря внутренним нагрузочным резисторам) при этом они могут использоваться как вводы. Если внешним сигналом вывод Порта 3 будут переведены в низкий уровень, из линии порта будет вытекать ток источника (IIL) благодаря внутреннему сопротивлению нагрузки. Порт P3 также обслуживает функции дополнительных устройств AT89C2051 как перечислено ниже:

Альтернативные функции выводов порта P3:

P3.0 - RXD (вход последовательного порта);

P3.1- TXD (выход последовательного порта);

P3.2 - INT0 (внешнее прерывание);

P3.3 - INT1 (внешнее прерывание);

P3.4

- T0 (таймер 0 внешний ввод);

P3.4

- T0 (таймер 0 внешний ввод);

P3.5 - T1 (таймер 1 внешний ввод);

Порт P3 также получает некоторые сигналы управления при программировании и проверке ПЗУ программ;

RST-Вход сброса. На всех вывода ввода/вывода устанавливается сигнал логической 1, как только RST перейдет в состояние логической 1. Высокий логический уровень на входе RST должен удерживаться в течении двух машинных циклов для надежного сброса устройства. Каждый машинный цикл берет 12 тактов генератора или циклов часов;

XTAL1-Вход инвертирующего усилителя тактового генератора и вход внешнего тактового сигнала;

XTAL2-Выход инвертирующего усилителя генератора.

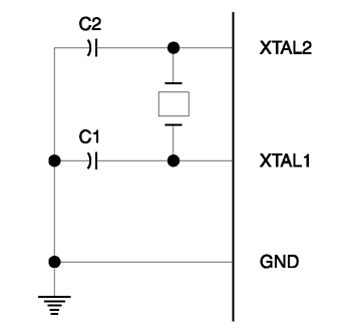

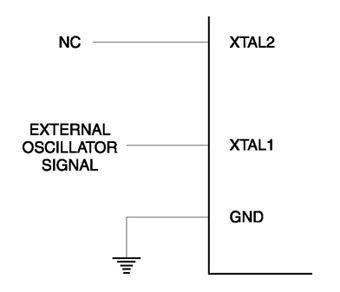

Характеристики Генератора: XTAL1 и XTAL2 - вход и выход, соответственно, инвертирующего усилителя, который может быть настроен для использования как внутренний генератор, как показано на Рисунке 7. Может использоваться кварцевый или керамический резонатор. Чтобы управлять устройством от внешнего источника колебаний, вывод XTAL2 должен быть оставлен свободным, а на XTAL1 подается управляющий сигнал, как показано на Рисунке 8. Нет никаких жестких ограничений к частоте внешнего тактового сигнала, так как к внутренней схеме синхронизации осуществляется через встроенный делитель на два, но требования к уровням напряжения высокого и низкого уровней должны соблюдаться.

Рисунок 7- Подключение кварцевого кристалла.

Примечания: C1, C2 = 30 pF +/- 10 pF для Кварцевых Резонаторов = 40 pF +/- 10 pF для Керамических Резонаторов.

Рисунок 8- Подключение внешнего тактового сигнала.

Ограничения на некоторые Команды:

AT89C2051

это экономичный и недорогой представитель

большого семейства микроконтроллеров

фирмы Атмел. Он содержит 2 Килобайта

памяти программ.  Микроконтроллер

полностью совместим с архитектурой

MCS- 51, и может быть запрограммирован,

используя систему команд MCS-51. Однако,

имеются несколько соображений, которые

нужно иметь в виду при использовании

некоторых команд в программе для этого

устройства.

Все команды, связанные с

переходом к подпрограмме или безусловным

переходом должны быть ограничены так,

чтобы они адресовали ячейку в пределах

физического пространства памяти программ

устройства, которое ограничено 2КБ для

AT89C2051. За это несет ответственность

разработчик программного обеспечения.

Например, команда LJMP 7E0H была бы допустима

для AT89C2051 (с 2КБ памяти), но LJMP 900H будет

не допустимо.

Микроконтроллер

полностью совместим с архитектурой

MCS- 51, и может быть запрограммирован,

используя систему команд MCS-51. Однако,

имеются несколько соображений, которые

нужно иметь в виду при использовании

некоторых команд в программе для этого

устройства.

Все команды, связанные с

переходом к подпрограмме или безусловным

переходом должны быть ограничены так,

чтобы они адресовали ячейку в пределах

физического пространства памяти программ

устройства, которое ограничено 2КБ для

AT89C2051. За это несет ответственность

разработчик программного обеспечения.

Например, команда LJMP 7E0H была бы допустима

для AT89C2051 (с 2КБ памяти), но LJMP 900H будет

не допустимо.

Команды Перехода: LCALL, LJMP, ACALL, AJMP, SJMP, JMP @A+DPTR Эти команды безусловного перехода выполняются правильно, пока программист имеет в виду, что адрес ячейки, к которой происходит переход, должен оставаться в пределах физических границ размера памяти программы (00H - 7FFH для процессора 89C2051). Нарушение физических пределов адресов может вызвать непредсказуемое поведение программы. CJNE [...], DJNZ [...], JB, JNB, JC, JNC, JBC, JZ, JNZ: С этими командами условного перехода то же самое правило, что и для команд безусловного перехода. Здесь также, нарушение границы памяти может привести к ошибочному выполнению программы. Для прикладных программ, включающих прерывания нормальное прерывание обслуживается стандартные адреса используемые в архитектуре семейства 80C51, сохранились.

Команды

MOVX-имеющие отношение к памяти данных:

AT89C2051

содержит 128 байтов внутренней памяти

данных. Таким образом, в AT89C2051 глубина

стека ограничена 128 байтами (количеством

доступной оперативной памяти). В этом

устройстве доступ к внешней памяти

данных не поддерживается, так же, как и

внешняя память программ. Поэтому в ваших

программах нельзя использовать команду

MOVX [...].

Стандартный ассемблер 80C51 будет

транслировать все команды, даже если

они  написаны

в нарушении ограничений, упомянутых

выше. Учитывать физические особенности

и ограничения данного контроллера и

корректировать используемые команды

должен разработчик программного

обеспечения.

Биты

защиты памяти программ:

На чипе имеются два бита защиты, каждый

из которых может быть оставлен

незапрограммированным (U) или быть

запрограммированным (P), для реализации

режимов защиты, перечисленных в таблице

ниже: Режимы

защиты памяти программ Состояние

LB1 LB2

Режим защиты:

написаны

в нарушении ограничений, упомянутых

выше. Учитывать физические особенности

и ограничения данного контроллера и

корректировать используемые команды

должен разработчик программного

обеспечения.

Биты

защиты памяти программ:

На чипе имеются два бита защиты, каждый

из которых может быть оставлен

незапрограммированным (U) или быть

запрограммированным (P), для реализации

режимов защиты, перечисленных в таблице

ниже: Режимы

защиты памяти программ Состояние

LB1 LB2

Режим защиты:

|

1

Таблица

2-режим защиты |

U |

U |

Программа не блокируется. |

|

2 |

P |

U |

Заблокирована возможность программирования. |

|

3 |

P |

P |

То же что и режим 2, но заблокирована и проверка. |

Внимание: Биты защиты могут быть стерты только во время операции "Очистка кристалла".

Режим ожидания: В режиме ожидания, ЦП переходит в неактивное состояние, в то время как все внутренние периферийные устройства остаются активными. Режим вызывается программным путем. Содержание ОЗУ микросхемы и всех специальных регистрах остается неизменным в течение всего этого режима. Неактивный режим может быть закончен любым разрешенным прерыванием или аппаратным сбросом. P1.0 и P1.1 должны быть установлены в '0', если не используется внешняя нагрузка, или в '1' если есть внешняя нагрузка. При этом, если ждущий режим закончен аппаратным сбросом, устройство обычно возобновляет выполнение программы, с того места, где оно было прекращено. Она выполняется еще в течение двух машинных циклов прежде, чем сработает внутренний алгоритм сброса. При этом запрещен доступ внутренних аппаратных средств к внутренней ОЗУ, но доступ к линиям ввода/вывода не запрещен. Для устранения возможности непредвиденной записи через вывод порта, когда режим ожидания закончен сбросом, следующая команда после той, которая вызывала ждущий режим, не должна быть командой записи в линию порта или во внешнюю память.

Режим

пониженного потребления:

В режиме пониженного потребления

внутренний генератор останавливается,

и команда, которая вызывает режим

пониженного потребления, должна быть

последней выполняемой командой.

Содержимое внутреннего ОЗУ и Специальных

Функциональных Регистров сохраняется

до тех пор, пока не закончится режим

пониженного потребления. Единственный

выход из этого режима - аппаратный сброс.

Сброс переопределяет SFRS, но не изменяет

содержимое встроенного ОЗУ. Сброс не

должен быть активизирован прежде, чем

напряжение питания (VCC) будет восстановлено

до его нормального значения и должен

быть активным достаточно долго, чтобы

позволить генератору стабилизироваться

и перезагрузить систему.

Линии P1.0 и

P1.1 должны быть установлены в '0', если

нет внешней нагрузки, или установлены

в '1' если внешняя нагрузка есть.

Режим

пониженного потребления:

В режиме пониженного потребления

внутренний генератор останавливается,

и команда, которая вызывает режим

пониженного потребления, должна быть

последней выполняемой командой.

Содержимое внутреннего ОЗУ и Специальных

Функциональных Регистров сохраняется

до тех пор, пока не закончится режим

пониженного потребления. Единственный

выход из этого режима - аппаратный сброс.

Сброс переопределяет SFRS, но не изменяет

содержимое встроенного ОЗУ. Сброс не

должен быть активизирован прежде, чем

напряжение питания (VCC) будет восстановлено

до его нормального значения и должен

быть активным достаточно долго, чтобы

позволить генератору стабилизироваться

и перезагрузить систему.

Линии P1.0 и

P1.1 должны быть установлены в '0', если

нет внешней нагрузки, или установлены

в '1' если внешняя нагрузка есть.

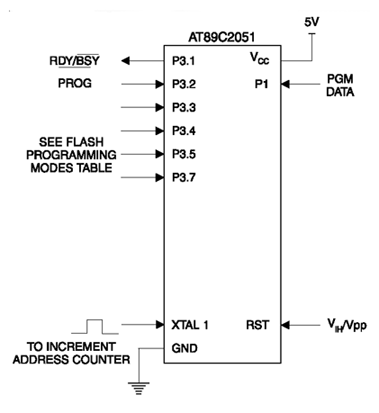

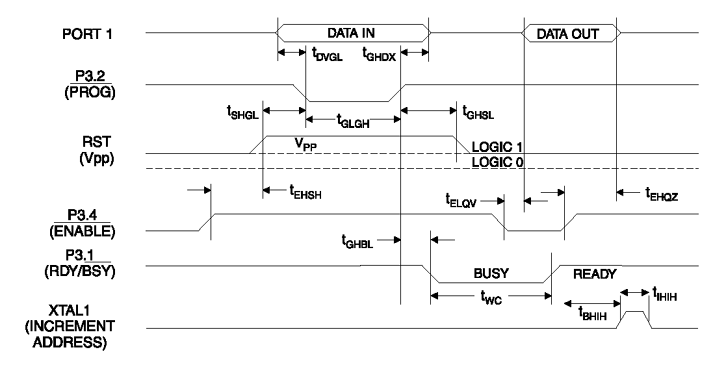

Прошивка памяти программ: Микросхема AT89C2051 поставляется с внутренней памятью программ (PEROM) 2 Кб в стертом состоянии (то есть, содержимое всех ячеек равно FFH) и готовом быть запрограммированным. При программировании памяти программ за один шаг программируется один байт. Как только массив запрограммирован, для того, чтобы повторно запрограммировать любой непустой байт, весь массив памяти должен быть стерт электрически.

Внутренний Счетчик Адреса: AT89C2051 содержит внутренний счетчик адреса PEROM, который всегда сбрасывается в 000 по фронту сигнала сброса на входе RST и увеличивает свое значение на единицу при каждом положительным импульсе на входе XTAL1.

Алгоритм программирования: Для программирования AT89C2051 рекомендуется следующая последовательность.

-

Последовательность Включения питания:

-

Подключите

источник питания между выводами VCC и

GND микросхемы

Подключите

источник питания между выводами VCC и

GND микросхемы

-

Входы RST и XTAL1 подключите к линии GND

-

Остальные выводы оставьте свободными, в таком состоянии после подключения напряжения питания микросхема должна находиться не менее 10 миллисекунд

Установите на входе RST уровень 'H' (высокий) Установите на входе P3.2 уровень 'H'

Установите соответствующую комбинацию 'H' или 'L' логических уровней на входах P3.3, P3.4, P3.5, P3.7 так, чтобы выбрать один из режимов программирования, показанных в таблице Режимов Программирования PEROM в соответствии с таблицей режимов программирования. Для программирования и проверки памяти программ:

Установите на входах P1.0 к P1.7 байт который должен быть зашит в 000-ю ячейку памяти программ.

Поднимите напряжение на входе RST до 12V, для начала процесса программирования ячейки.

Единичный импульс на входе P3.2 прошивает выбранный байт в памяти программ или биты блокировки. Длительность цикла записи байта величина самоустанавливающаяся и обычно составляет 1.2 мс.

Для проверки запрограммированных данных необходимо понизить уровень сигнала на входе RST с 12V до уровня логической 1 ('H'), и установить на выводах P3.3 в P3.7 appropiate уровни. Выходные данные считываются с выводов порта P1.

Для программирования следующего байта, при помощи импульса на XTAL1 увеличьте значение внутреннего счетчика адреса. Установите новые данные на выводах порта P1.

Повторить шаги 5 до 8, изменяя данные и продвигая счетчик адреса для всего массива 2 Кб или пока не достигнут конец объектного файла.

Последовательность отключения питания:

-

Установите

на входе XTAL1 уровень 'L'

Установите

на входе XTAL1 уровень 'L'

-

Установите на входе RST уровень 'L'

-

Освободите все остальные каналы ввода/вывода

-

Снимите питание с вывода Vcc

Опрос Данных: Микросхема AT89C2051 в процессе программирования памяти программ выдает информацию о конце цикла записи. В процессе записи байта, необходимо производить периодическое чтение последнего записанного байта. Информация о конце цикла записи содержится в бите, снимаемом с выхода P1.7. Как только цикл записи будет закончен, на всех выходных линиях установятся данные, соответствующие записываемому байту. Это сигнализирует о том, что можно начинать цикл записи следующего байта. Проверка конца цикла записи может начинать в любое время после начала цикла записи.

Ready/Busy(Готов/занят): Ход программирования байта может контролироваться также при помощи сигнала на выходе RDY/BSY. Если в процессе программирования на выходе P3.1 установится низкий уровень сразу после того, как уровень сигнала на входе P3.2 перейдет в высокое состояние. То есть на P3.1 сигнал Busy (ЗАНЯТ). На P3.1 опять установится высокий уровень, когда программирование окончено. То есть на P3.1 сигнал Ready (ГОТОВ).

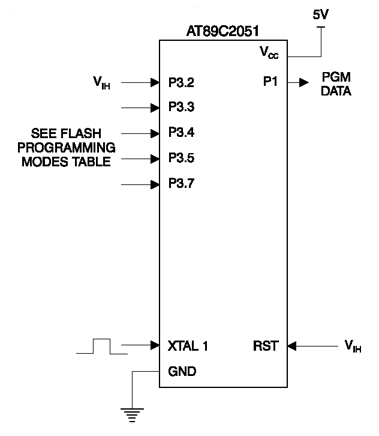

Проверка памяти программ: Если биты LB1 блокировки и LB2 не были запрограммированы, данные кода могут считываться через линии данных для проверки:

-

Сбросить внутренний адрес в 000, переведя уровень на входе RST с 'L' на 'H'.

-

Установить на входах управления комбинацию сигналов, соответствующих режиму чтения, и считать выходные данные через выводы порт P1.

-

При

помощи единичного импульса на входе

XTAL1 увеличить содержимое внутреннего

счетчика адреса.

При

помощи единичного импульса на входе

XTAL1 увеличить содержимое внутреннего

счетчика адреса.

-

Прочитать следующий байт данных кода через порт P1.

-

Повторить шаги 3 и 4, пока весь массив не будет считан.

Биты блокировки не могут быть проверены непосредственно. Проверка битов блокировки производится путем проверки того, что защита действует.

Стирание Чипа (Chip Erase): Полный массив PEROM (2 Килобайта) и оба Бита Блокировки стираются электрически. Для этого на входах управления устанавливается соответствующая комбинация сигналов управления и удерживается низкий уровень на входе P3.2 в течении 10 мс. После этого во всем массиве кода будет записан код 0FFH. Операция Chip Erase должна быть выполнена прежде, чем любой не пустой байт памяти может быть заново запрограммирован.

Чтение Байтов Сигнатуры: Байты сигнатуры читаются той же самой процедурой, что и обычное чтение данных при проверке по адресам 000H, 001H и 002, за исключением того, что на входы P3.5 и P3.7 должен быть подан низкий логический уровень. Возвращенные значения следующие. (000H) = 1EH если изготовитель - фирма Atmel (001H) = 21H, указывает на то, что это микросхема 89C2051

Интерфейс для программирования 89C2051: Любой байт кода может быть записан во флэш-память, и весь массив может быть стерт, используя соответствующую комбинацию сигналов управления. Микросхема имеет систему автонастройки параметров цикла записи, и после начала цикла, будет автоматически определять время его завершения. Все основные продавцы программного обеспечения во всем мире предлагают поддержку для всего ряда микроконтроллеров Atmel.

Режимы

Программирования:

Режимы

Программирования:

|

Mode |

RST |

P3.2/ Prog |

P3.3 |

P3.4 |

P3.5 |

P3.7 |

|

Запись Данных Кода (1,3) |

12V |

|

L |

H |

H |

H |

|

Чтение Данных Кода (1) |

H |

H |

L |

L |

H |

H |

|

Запись Бит защиты - 1 |

12V |

|

H |

H |

H |

H |

|

Запись Бит защиты - 2 |

12V |

|

H |

H |

L |

L |

|

Стирание всех данных |

12V |

|

H |

L |

L |

L |

|

Чтение Байта Сигнатуры |

H |

H |

L |

L |

L |

L |

Примечание: 1. Внутренний счетчик адреса PEROM сбрасывается в 000 по фронту RST и увеличивается на единицу по импульсу на выводе XTAL1. 2. Стирание всех данных требует длительности импульса PROG не менее 10 мс. 3. P3.1 устанавливается в ноль во время программирования для индикации состояния RDY/BSY\.

Программирование

флэш-памяти Проверка флэш-памяти:

Программирование

флэш-памяти Проверка флэш-памяти:

Характеристики режимов программирования и проверки флеш памяти:

Примечание:

Параметры действительны только для

режима программирования 12В.

Примечание:

Параметры действительны только для

режима программирования 12В.

Временные характеристики режимов программирования и проверки флэш-памяти:

Предельно допустимые параметры:

Рабочая температура ....................... -55 C +125 C Температура хранения ...................... -65 C +150 C Напряжение на Любом выводе относительно земли ........................ -1.0В +7.0В Максимальное напряжение питания .................. 6.6В Выходной ток (лог 1) .............................25.0 мА

5

ОПИСАНИЕ УПРОВЛЯЮЩЕЙ ПРОГРАММЫ

5

ОПИСАНИЕ УПРОВЛЯЮЩЕЙ ПРОГРАММЫ

ЗАКЛЮЧЕНИЕ

ЗАКЛЮЧЕНИЕ

СПИСОК

ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ

СПИСОК

ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ

1

ПРИЛОЖЕНИЕ

1

2

3

4

5

6