- •Введение

- •1 Анализ технического задания

- •2.2 Арифметическо-логическое устройство

- •2.3 Память микроконтроллера

- •2.4 Управление работой микроконтроллера

- •2.5 Организация ввода-вывода информации в микроконтроллере

- •Xtal1, xtal2 – входы для подключения кварцевого резонатора.

- •3.2 Постоянное запоминающее устройство

- •4.3 Программируемый интервальный таймер (пит)

- •5.2 Шинный формирователь к580ва86

- •5.3 Подключение микросхем, входящих в микропроцессорную систему, к

- •5.4 Разработка структурной схемы

- •Заключение

- •Список используемой литературы

5.2 Шинный формирователь к580ва86

Сопряжение модулей микросхем, входящих в микропроцессорную систему, с шиной данных реализовано на микросхемах шинных формирователей К580ВА86.

Рисунок 30 - Шинный формирователь К580ВА86

Передача

информации обеспечивается при сигнале

с уровнем логического 0 на входе СS.

При наличии на входе СS

сигнала с уровнем логической 1 все выходы

переходят в третье состояние. Сигнал

![]() снимается с выхода ОЕ буферного регистра

КР580ИР82.

снимается с выхода ОЕ буферного регистра

КР580ИР82.

Направление

передачи информации зависит от

сигнала

![]() .

При

.

При![]() = 0 информация с выходов микросхем

поступает в шину данных, при

= 0 информация с выходов микросхем

поступает в шину данных, при

![]() =1

из шины данных на входы микросхем.

=1

из шины данных на входы микросхем.

5.3 Подключение микросхем, входящих в микропроцессорную систему, к

шинам адреса и данных

Подключение микросхем, входящих в микропроцессорную систему, к шинам адреса и данных осуществляется посредством буферного регистра КР580ИР82 и шинного формирователя К580ВА86.

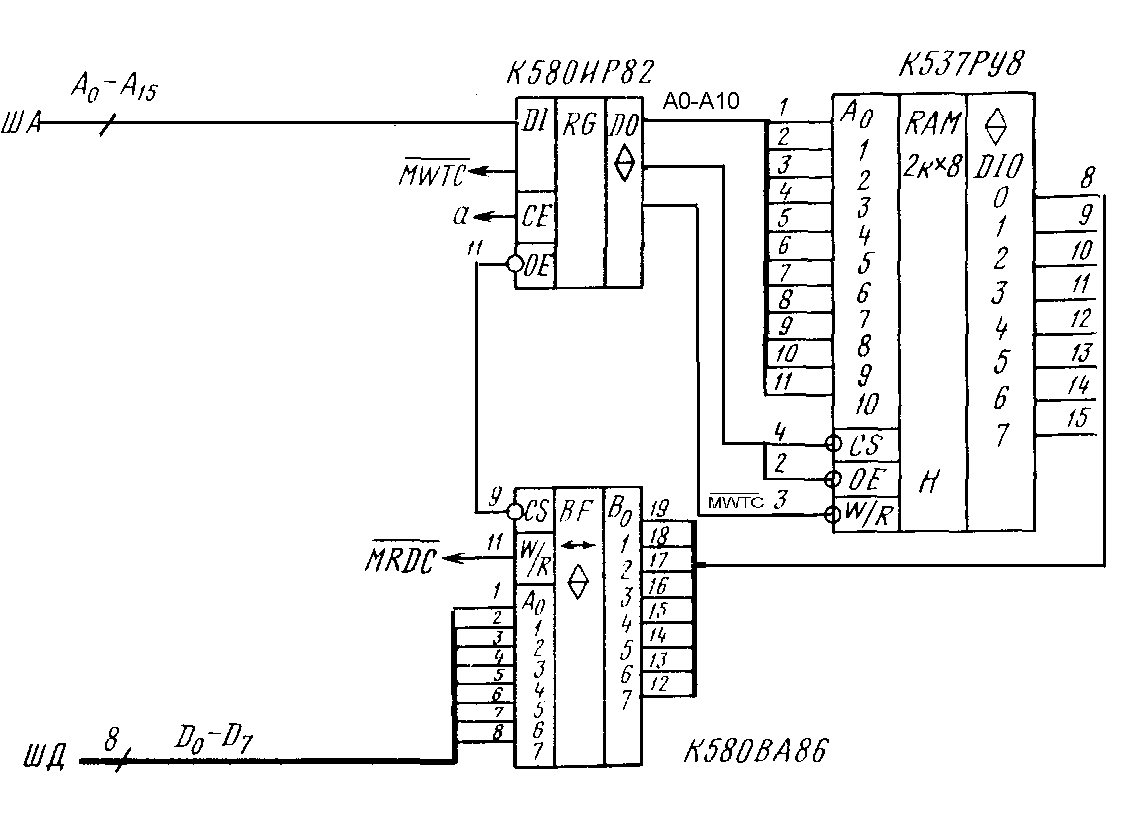

Подключение модуля ОЗУ представлено на рисунке 31.

Рисунок 31 - Подключение ОЗУ к шинам адреса и данных

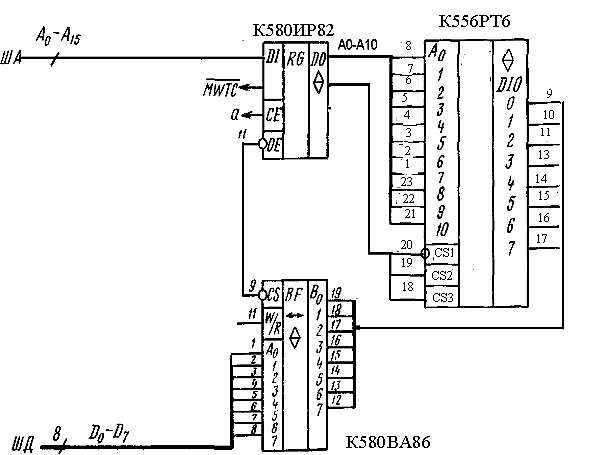

Подключение модуля ПЗУ представлено на рисунке 32.

Рисунок 32 - Подключение ПЗУ к шинам адреса и данных

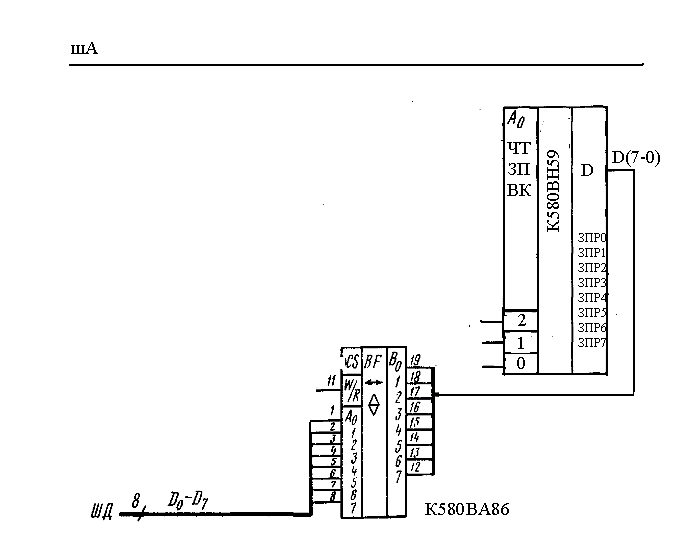

Подключение программируемого интервального таймера представлено на рисунке 33:

Рисунок 33 - Подключение ПИТ к шинам адреса и данных

Подключение программируемого контроллера прерываний представлено на рисунке 34:

Рисунок 34 - Подключение КПДП к шинам адреса и данных

Подключение программируемого периферийного адаптера представлено на рисунке 35:

Рисунок 35 - Подключение программируемого периферийного адаптера

к шинам адреса и данных

Подключение АЦП представлено на рисунке 36:

Рисунок 36 – Подключение АЦП

5.4 Разработка структурной схемы

На основании анализа структурных схем устройств, входящих в разрабатываемую микропроцессорную систему, а также на основании выбранного способа подключения данных устройств к магистралям представим микропроцессорную систему в виде структурной схемы. На схеме каждое устройство представим в виде прямоугольника, обозначим сигналы и выходы устройств МПС, обеспечивающих их сопряжение.

Структурная схема приведена в приложении А.

Заключение

В результате курсового проектирования в соответствии с заданным вариантом разработана микропроцессорная система на базе микроконтроллера К1816ВЕ48. На основании анализа функционирования данного микроконтроллера разработан процессорный модуль и интерфейс микропроцессорной системы.

В соответствии с техническим заданием разработана подсистема памяти на базе БИС ОЗУ К537РУ8 БИС ПЗУ К556РТ6.

Для обеспечения полноценного и бесперебойного функционирования микропроцессорной системы разработана подсистема ввода/вывода и прерываний.

На основании анализа структурных схем устройств, входящих в разрабатываемую микропроцессорную систему, а также на основании выбранного способа подключения данных устройств к магистралям составлена структурная схема микропроцессорной системы.