- •Введение

- •1 Анализ технического задания

- •2.2 Арифметическо-логическое устройство

- •2.3 Память микроконтроллера

- •2.4 Управление работой микроконтроллера

- •2.5 Организация ввода-вывода информации в микроконтроллере

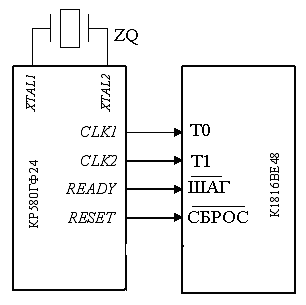

- •Xtal1, xtal2 – входы для подключения кварцевого резонатора.

- •3.2 Постоянное запоминающее устройство

- •4.3 Программируемый интервальный таймер (пит)

- •5.2 Шинный формирователь к580ва86

- •5.3 Подключение микросхем, входящих в микропроцессорную систему, к

- •5.4 Разработка структурной схемы

- •Заключение

- •Список используемой литературы

Xtal1, xtal2 – входы для подключения кварцевого резонатора.

TANK – вход для подключения параллельного LC-контура.

SYNC – вход синхронизации.

RESIN – входной сигнал «СБРОС».

RDYIN – вход сигнала «ГОТОВ», для подачи сигналов о готовности внешних устройств к работе с МП.

OSC – выход генератора, используемый для тактирования периферийных устройств.

CLK1, CLK2 – выходы тактовых импульсов.

STSTB – строб состояния – сигнал L-уровня, используемый для фиксации слова состояния МП.

RESET – выходной сигнал «СБРОС».

READY– выходной сигнал «ГОТОВ».

Питание генератора тактовых импульсов осуществляется источником напряжения +5В.

Рисунок 12 – Подключение ГТИ к центральному микропроцессору

2.8 АЦП

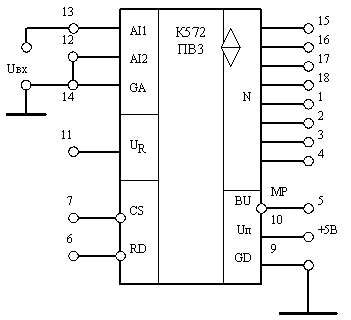

Широкое распространение однобайтных процессоров вызвало разработку восьмиразрядных аналого-цифровых преобразователей. В разрабатываемой МПС применим АЦП типа К572ПВ3.

Схема подключения АЦП К572ПВ3 к МП показана на рисунке 13.

Время преобразования этого АЦП равно 7,5 мкс, ток потребления от одного источника питания 5 В составляет всего лишь 5 мА. АЦП имеет два одинаковых входа AI1 и AI2, соединённых внутренними резисторами с одним входом компаратора.

На этот же вход компаратора подаётся выходной ток цифро-аналогового преобразователя, управляемого регистром последовательного приближения.

Рисунок 13 - Схема подключения АЦП

Таким

образом, АЦП обеспечивает преобразование

в код суммы напряжений, подаваемых на

входы AI1 и AI2. При практическом использовании

этого АЦП на вход AI1 подают входное

напряжение Uвх, а на вход AI2 – напряжение,

с помощью которого производят регулировку

нуля АЦП. Управление работой АЦП К572ПВ3

осуществляется с помощью сигналов,

подаваемых на входы

![]() (выбор кристалла) и

(выбор кристалла) и

![]() (чтение). Переход 0/1 на входе

(чтение). Переход 0/1 на входе

![]() запускает схему сброса АЦП, потенциал

0 на входе

запускает схему сброса АЦП, потенциал

0 на входе

![]() осуществляет запуск преобразователя

при условии, что предварительно был

осуществлён его сброс. Таким образом,

если

осуществляет запуск преобразователя

при условии, что предварительно был

осуществлён его сброс. Таким образом,

если

![]() =0,

то переход 0/1 на входе

=0,

то переход 0/1 на входе

![]() обусловит

сброс и запуск преобразователя. Если

же

обусловит

сброс и запуск преобразователя. Если

же

![]() =1,

то этот переход вызывает только сброс,

а запуск произойдет по спаду 1/0 на входе

=1,

то этот переход вызывает только сброс,

а запуск произойдет по спаду 1/0 на входе

![]() .

Выход BU (АЦП занят) принимает потенциал

«нуль» тогда, когда осуществляется

процесс преобразования. Данные на

кодовом выходе N существуют при сочетании

сигналов

.

Выход BU (АЦП занят) принимает потенциал

«нуль» тогда, когда осуществляется

процесс преобразования. Данные на

кодовом выходе N существуют при сочетании

сигналов

![]() =0,

=0,

![]() =0,

=0,

![]() =1,

если же этого сочетания нет, если же

этого сочетания нет, то выход находится

в высокоимпендансном состоянии.

=1,

если же этого сочетания нет, если же

этого сочетания нет, то выход находится

в высокоимпендансном состоянии.

3 РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

3.1 Оперативное запоминающее устройство

Оперативные ЗУ предназначены для хранения переменной информации и имеют практически одинаковое быстродействие при считывании и записи.

Микросхемы серии К537РУ8 представляют собой оперативные запоминающие устройства с произвольной выборкой статического типа, емкостью 65 536 бит с организацией 2048х8 бит и, следовательно, допускает запись или считывание информации 8- разрядными словами (байтами).

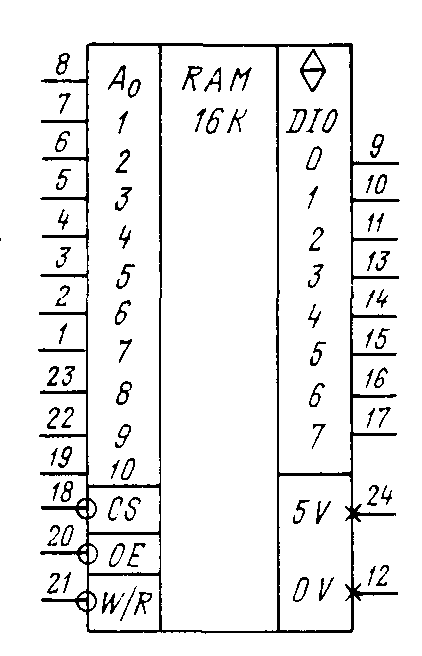

Цоколевка корпуса ОЗУ К537РУ8 представлена на рисунке 11:

Рисунок 14 - Цоколевка корпуса ОЗУ К537РУ8

Сигналы и выводы К537РУ8:

A –сигнал кода адреса

C – тактовый сигнал

![]() – строб

адреса столбца. Фиксирует код адреса

столбца на входном регистре.

– строб

адреса столбца. Фиксирует код адреса

столбца на входном регистре.

![]() –

строб

адреса строки. Фиксирует код адреса

строки на входном регистре.

–

строб

адреса строки. Фиксирует код адреса

строки на входном регистре.

![]() –

управляющий

вход. Сигнал

–

управляющий

вход. Сигнал

![]() разрешает(

разрешает(![]() =0)

или запрещает(

=0)

или запрещает(![]() =1)

обращение к микросхеме по информационным

входу или выходу.

=1)

обращение к микросхеме по информационным

входу или выходу.

CE – разрешение

WR – запись

RD – считывание

W/R – запись - считывание

WE – разрешение записи

OE – разрешение по выходу считывания

O –данные

DI – информационный вход

DO – информационный выход

ADI/O – адрес, данные: вход-выход

DI/O – данные: вход-выход

REF – регенерация

PR – программирование

ER – стирание

Ucc – напряжение питания

Upr - напряжение программирования

0V – общий вывод микросхемы

Входы

и выходы микросхемы совмещены и обладают

двунаправленной проводимостью. Другой

особенностью микросхемы является

наличие сигнала

![]() -

разрешение по выходу, т.е. разрешения

считывания при наличии сигнала

-

разрешение по выходу, т.е. разрешения

считывания при наличии сигнала

![]() -0.

-0.

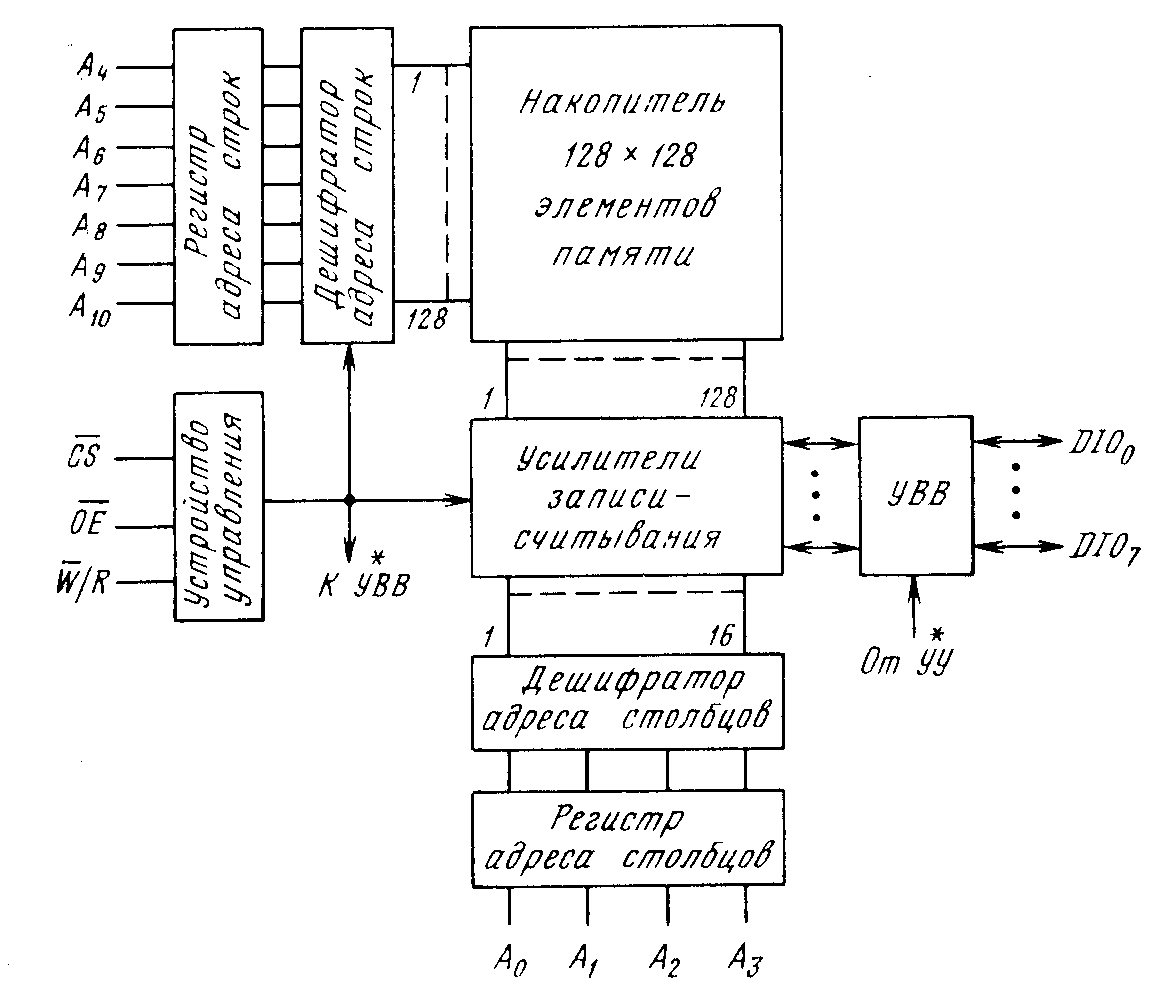

Микросхемы К537РУ8 изготавливаются по КМДП технологии. Структура К537РУ8 представлена на рисунке 15.

Она включает в себя матрицу накопителя с 128*128 ЭП, регистры и дешифраторы кода адреса строк и столбцов, усилители записи/считывания, УУ и УВВ.

Рисунок 15 – Структура К537РУ8

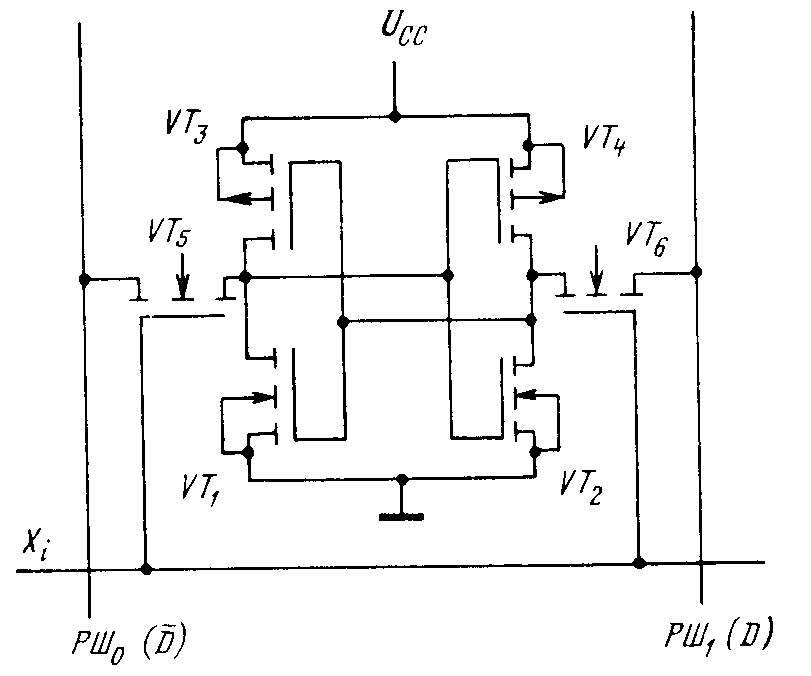

В качестве статического элемента памяти применен триггер на КМДП - транзисторах (рисунок 16).

Накопитель разбит на восемь секций по 128*16 ЭП в каждой. Четыре младших разряда кода адреса А0-А3 выбирают по одному столбцу в каждой секции и коммутируют их с УВВ.

Рисунок 16 – Статический элемент памяти

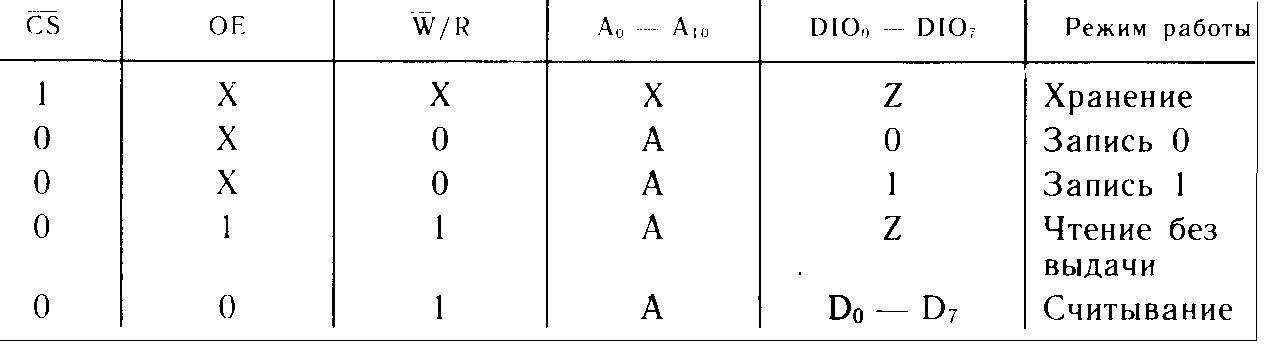

Управление

устройством ввода/вывода осуществляют

сигналы

![]() ,

,

![]() ,

,

![]() /R,

предварительно обработанные устройством

управления. В соответствии с таблицей

истинности (рисунок 17), в зависимости

от значений управляющих сигналов

микросхема может работать в одном из

трех режимов: записи, считывания и

хранения.

/R,

предварительно обработанные устройством

управления. В соответствии с таблицей

истинности (рисунок 17), в зависимости

от значений управляющих сигналов

микросхема может работать в одном из

трех режимов: записи, считывания и

хранения.

Рисунок 17 – Таблица истинности К537РУ8

В

режиме записи информация 8-разрядным

кодом через УВВ и усилители записи/считывания

поступает в выбранную ячейку памяти.

При считывании информация из выбранной

ячейки памяти поступает на УВВ и через

него – на выходы. Сигнал разрешения

выхода

![]() позволяет в режиме считывания запрещать

вывод информации: при

позволяет в режиме считывания запрещать

вывод информации: при

![]() =1

входы/выходы принимают высокоимпедансное

состояние, и информация на выходах

отсутствует.

=1

входы/выходы принимают высокоимпедансное

состояние, и информация на выходах

отсутствует.

Электрические параметры микросхем памяти разделяют на статические и динамические.

Электрические статические параметры К537РУ8:

Напряжение

питания

![]() ,В

5

,В

5

Напряжение выходное:

-

высокого уровня

![]() ,

В

5

,

В

5

-

низкого уровня

![]() ,

В

0,01

,

В

0,01

Напряжение

![]() ,

В

2,5

,

В

2,5

Временные диаграммы работы микросхем в режимах считывания, записи приведены на рисунке 18:

Рисунок 18 – Временные диаграммы циклов записи и считывания

информации

В

режиме записи к выводам микросхемы

вначале подводят сигналы кода адреса

А={A0-A7},

сигнал записи W/R=1

и информационный сигнал D.

Затем устанавливают сигнал

![]() с задержкой во времени

с задержкой во времени

![]() относительно сигналов адреса. Длительность

сигнала

относительно сигналов адреса. Длительность

сигнала

![]() определяют параметром

определяют параметром

![]() .

Кроме того, указывают длительность

паузы

.

Кроме того, указывают длительность

паузы

![]() в последовательности сигналов

в последовательности сигналов

![]() ,

которую следует выдержать для

восстановления потенциалов емкостных

элементов схемы.

,

которую следует выдержать для

восстановления потенциалов емкостных

элементов схемы.

Сигналы

адреса необходимо сохранить на время

![]() после снятия сигнала

после снятия сигнала

![]() .

В течение всего цикла записи

.

В течение всего цикла записи

![]() выход микросхемы находится в

высокоимпедансном состоянии.

выход микросхемы находится в

высокоимпедансном состоянии.

В

цикле считывания порядок подачи сигналов

тот же, что и при записи, но при условии

W/R=0.

Время появления сигнала на информационном

выходе DO

определяют параметрами

![]() (время выбора) и

(время выбора) и

![]() (время

выборки адреса), причем

(время

выборки адреса), причем

![]() =

=![]() +

+![]() .

.

Динамические параметры микросхемы К537РУ8:

Время

цикла записи/чтения

![]() ,

нс 160

,

нс 160

Время

выбора

![]() ,

нс

200

,

нс

200

Время

установления сигнала

![]() ,

нс 70

,

нс 70

Время

сохранения сигнала

![]() ,нс

60

,нс

60

Длительность

сигнала

![]() ,нс

220

,нс

220

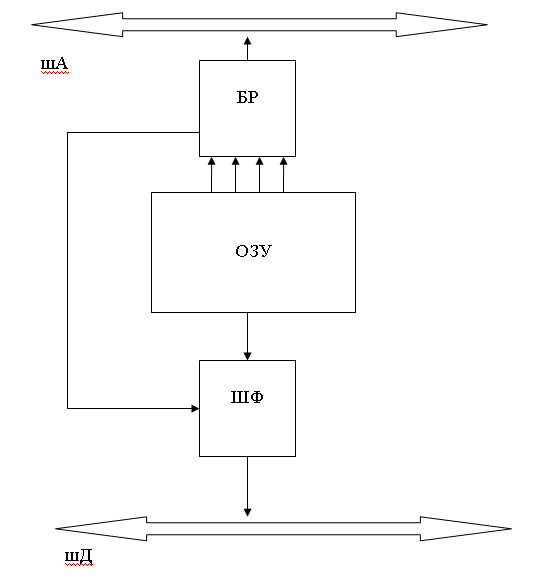

На рисунке 19 приведем обобщенную схему подключения ОЗУ к шинам адреса и данных посредством буферного регистра и шинного формирователя.

Подробная схема подключения ОЗУ к шинам адреса и данных посредством буферного регистра и шинного формирователя будет представлена в пункте разработки уточненной схемы микропроцессорной системы, сигналы и выходы, с помощью которых производится подключение микросхемы будут указаны в пункте подбора буферного регистра и шинного формирователя.

Рисунок 19 – Подключение ОЗУ к шинам данных и адреса