шпоргалка / Shpory_po_mikro_processornym_ustroystvam / Шпоры МП 21-25

.doc|

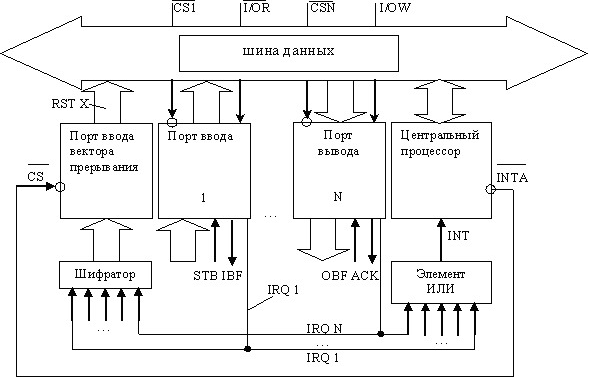

21. Ввод-вывод по прерываниям Основным недостатком программно-управляемого ввода-вывода является нерациональное использование машинного времени микропроцессора. Оно, в основном, тратится на циклы ожидания изменений во входном коде или на циклы ожидания готовности порта. Циклов ожидания может быть очень много из-за низкой скорости работы большинства внешних устройств. Циклы ожидания можно исключить при помощи ввод-вывод по прерываниям. Порты не имеют средств для передачи в микропроцессор сигнала готовности. На основе сигналов готовности они формируют запросы на обслуживание IRQ. Функциональная схема включения портов в микропроцессорную систему

Схема реализует одноуровневую векторную систему прерываний. Она включает в себя порты 1…N, реализующие асинхронный ввод-вывод, элемент «ИЛИ», приоритетный шифратор и порт ввода вектора прерывания. В начальном состоянии все запросы на обслуживания IRQ1…IRQN равны нулю, то есть отсутствуют. Пусть далее появляется запрос от порта ввода No1 IRQ = 1. Этот запрос через элемент «ИЛИ» передается на вход запроса прерываний INT процессора. Процессор, реагируя на этот запрос, выполняет следующие действия: 1. проверяет, разрешены ли прерывания. Если они запрещены, никаких других действий по обслуживанию прерывания не производится. В микро-ЭВМ продолжается выполнение основной программы; 2. запрещает прерывания; 3. завершает выполнение текущей команды; 4. переходит в режим приема кода операции с шины данных; 5. блокирует с помощью системного контроллера выдачу сигнала MEMR шины управления и формирует на отдельной линии этой шины сигнал INTA – «подтверждение прерывания»; 6. принимает с шины данных код команды рестарта RST 1; 7. выполняет эту команду, то есть записывает в стек адрес следующей по порядку команды основной программы и передает управление по адресу 0008H, с которого должна начинаться программа ввода из порта 1; 8. выполняет всю программу ввода и завершающую ее команду RET. По этой команде из стека восстанавливается содержимое счетчика команд, которое было там до прерывания, то есть управление передается очередной команде основной программы. Программа обслуживания прерывания в одноуровневой векторной системе обычно строится по типовой блок-схеме. Типовая блок-схема программы обслуживания прерывания

|

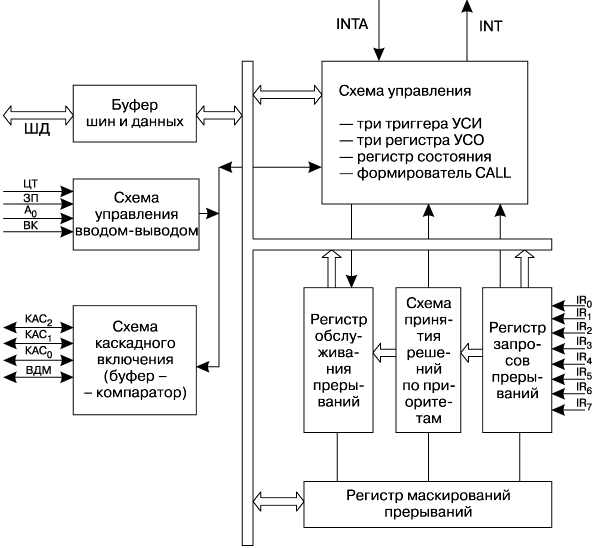

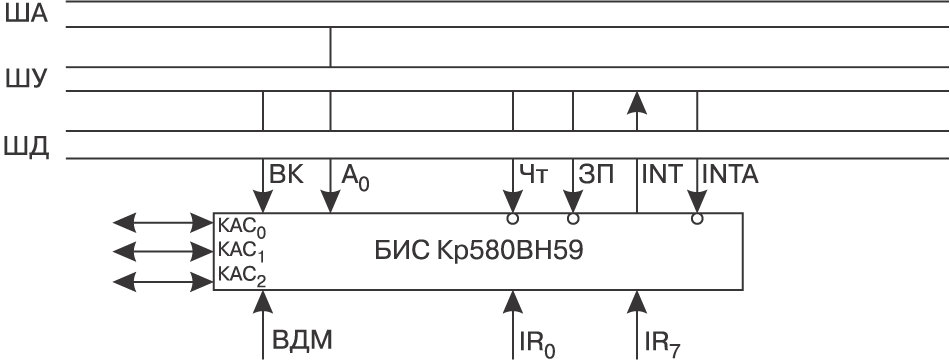

22.Программируемый контроллер прерываний ВН59 БИС КР580ВН59 программируемого контроллера прерываний (ПКП) представляет собой устройство, реализующее до 8 уровней запросов прерывания с возможностями программного маскирования и изменения дисциплины обслуживания прерываний. Упрощенная структурная схема ПКП

Cхема подключения ПКП к системной шине

|

24.Организация параллельного интерфейса Функции: 1) Интерпретирующие сигналы адреса и выбора между памятью и портом ввода-вывода. 2) Определить выполнение операции ввода или вывода. 3) Преобразовать форматы данных из //-х форм в последовательную и наоборот. 4) Формирование сигнала запроса прерываний и прямой доступ к памяти. 5) Должен реагировать на сигнал сброса поступающего от центрального процессора. Периферийное устройство для своей работы требует определенного набора управляемых сигналов протоколов обмена. Если не удовлетворяет требованиям совместимости, то эти периферийные устройства не могут работать. Через интерфейс структура и принцип работы которой определяется совместимостью компонентов. Для подключения периферийных устройств нужно подключение 2-х модулей, адаптеров и контроллеров. Контроллер имеет дополнительные устройства.

|

|

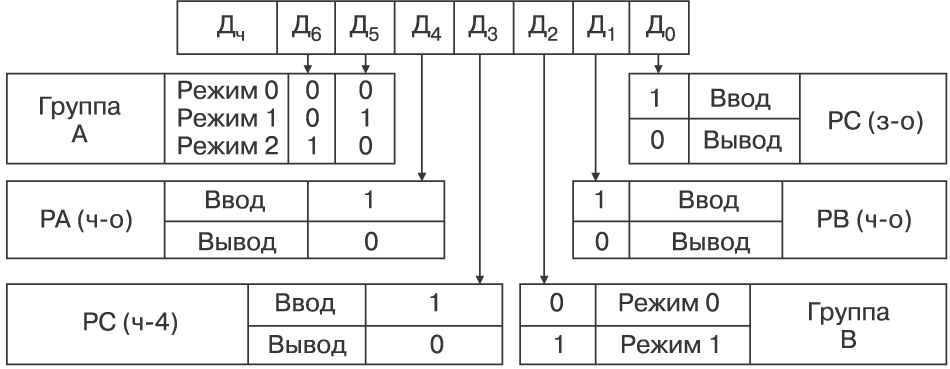

25. Программируемый параллельный адаптер ВВ55 Интерфейс //-го адаптера позволяет реализовать байтовый обмен центрального процессора с периферийными устройствами (АЦП, цифровые датчики). Можно обеспечить 24 линии, 3 порта. Может выполняться в разных режимах работы: синхронный обмен, однонаправленный обмен, двунаправленный обмен (асинхронный, полудуплексный). БИС параллельного интерфейса КР 580ВВ55 предназначена для организации ввода-вывода параллельной информации и позволяет реализовывать большинство известных протоколов обмена по параллельным каналам. Структурная схема БИС КР 580ВВ55

Управляющее слово

В режиме 0 работают 3 порта 24 линии. В режиме 1 (однонаправленный страбирующий обмен) работают только 2 порта. В режиме 2 (двунаправленный страбирующий обмен) работает только порт А. |

||

|

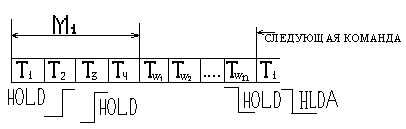

23.Обмен в режиме прямого доступа к памяти (ПДП) Это режим внепроцессорного обмена. Для организации высокоскоростного обмена между ядром МПС и периферийными устройствами большими объемами информации. 1.Режим идентификации. Он основан на том что передача информации между периферийным устройством и памятью выполняется в те моменты времени в которых системный процессор не обращается системной шине. 2. ПДП с пропуском тактов. Для этого есть два сигнала: режим запроса и подтверждения.

|