шпоргалка / 45-47

.docАрхитектура и функциональные возможности контроллера прямого доступа к памяти

Контроллер прямого доступа к памяти (КПДП) КР580ВТ57 предназначен для организации скоростного обмена данными между памятью и внешними устройствами, причем обмен инициируется внешним устройством.

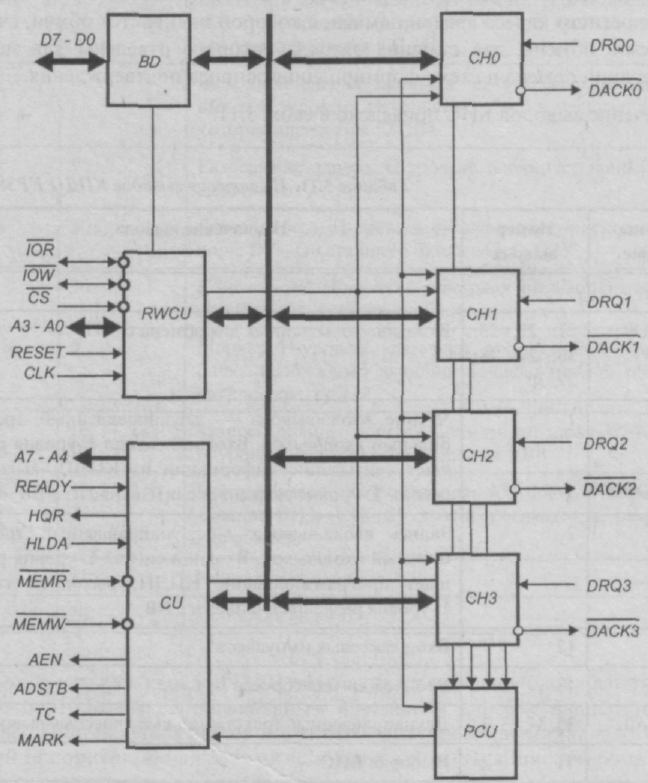

Структурная схема контроллера приведена на рис. 5.45.

|

Рис. 5.45. Структурная схема КР580ВТ57 |

Она содержит: - двунаправленный буфер данных (BD), предназначенный для обмена информацией между МП и КПДП; - схему управления чтением/записью (RWCU), которая адресует внутренние регистры КПДП и управляет обменом по шине D7-D0; - блок управления (CU), задающий режимы работы КПДП; - блок управления приоритетами (PCII), обеспечивающий порядок обслуживания запросов внешних устройств; - четыре канала прямого доступа (СН0-СНЗ), каждый из которых содержит регистр адреса ячейки памяти, с которой начинается обмен, счетчик циклов обмена, два старших разряда которого отведены для задания операций обмена и схему формирования запроса/подтверждения. Каждый из четырех каналов ПДП обеспечивает передачу блока данных емкостью до 16 Кбайт с произвольным начальным адресом в диапазоне 0-64 Кбайт. Приоритеты каналов могут быть фиксированными (канал 0 имеет высший приоритет, канал 3 - низший) или изменяться циклическим образом. В последнем случае каналу, в котором произошло обслуживание запроса ПДП, присваивается низший приоритет, а каналу со следующим номером - высший. |

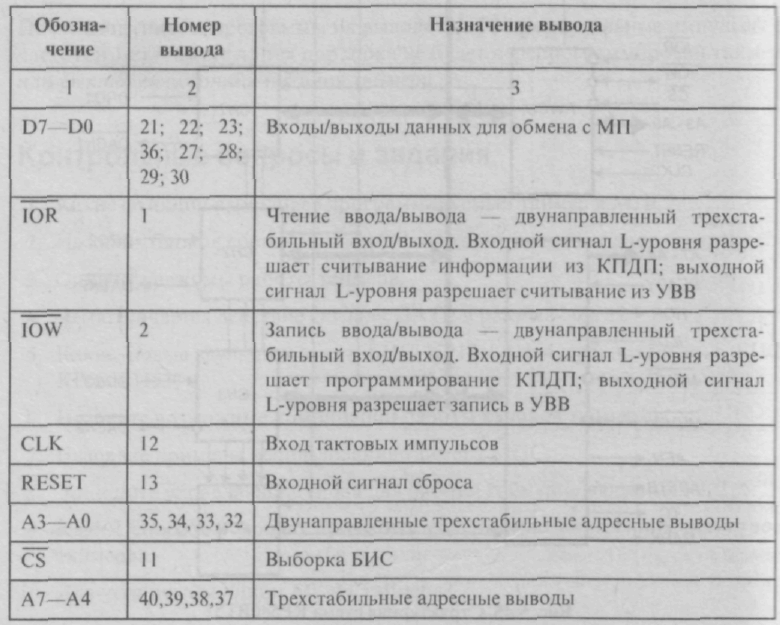

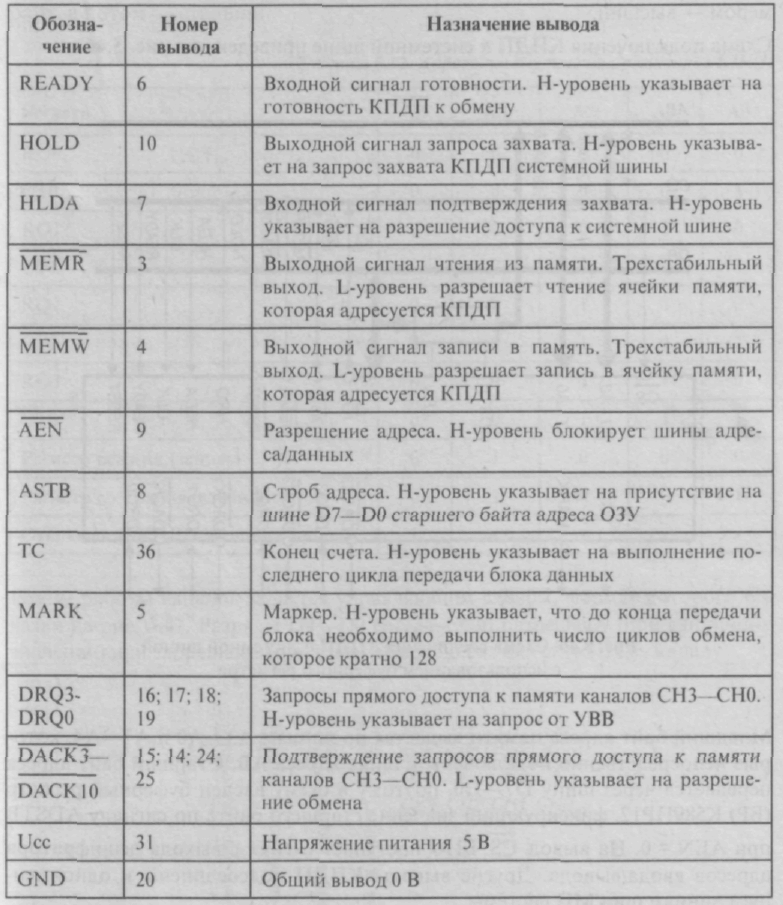

Назначение выводов БИС приведено в табл. 5.11.

Схема подключения КПДП к системной шине приведена на рис. 5.46.

Рис. 5.46. Схема соединения КПДП с системной шиной с использованием буферного регистра

Tаблица 5.11. Назначение выводов КПДП КР580ВТ57

Младший

байт адреса памяти выдается по линиям

A3-А0 и А7-А4, которые непосредственно

подключены к шине адреса АВ. Старший

байт адреса передается через шину D7-D0,

поэтому в схему введен буферный регистр

(БР) К589ИР12, фиксирующий значение старшего

байта по сигналу ADSTB

при

AEN=0.

На вывод

![]() БИС поступает сигнал с выхода дешифратора

адресов ввода/вывода. Другие выводы

КПДП подсоединены к одноименным линиям

шин МП системы.

БИС поступает сигнал с выхода дешифратора

адресов ввода/вывода. Другие выводы

КПДП подсоединены к одноименным линиям

шин МП системы.

Путем программирования КПДП задают режим работы каналов, направление обмена информацией между памятью и устройством ввода/вывода, начальный адрес и длину массива памяти, участвующей в обмене.

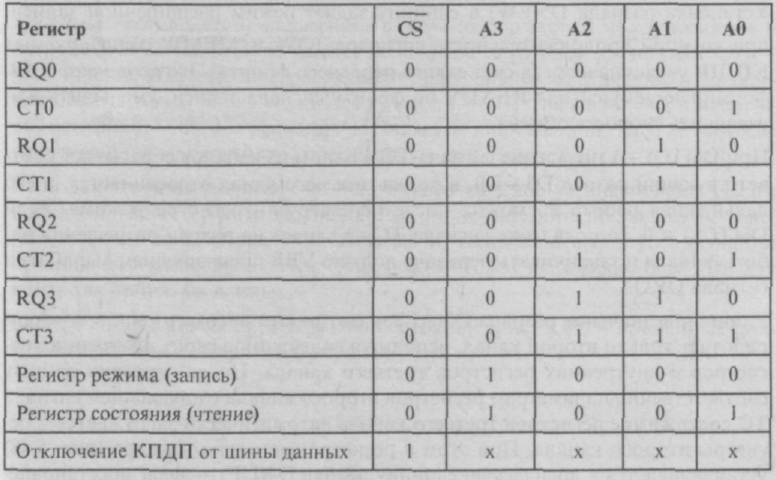

Значения

адресных разрядов A3-А0 и сигнала

![]() при записи и чтении регистров БИС

приведены в табл. 5.12. Запись информации

в 16-разрядные

регистры

осуществляется двумя командами, сначала

записывается младший байт, а потом -

старший.

при записи и чтении регистров БИС

приведены в табл. 5.12. Запись информации

в 16-разрядные

регистры

осуществляется двумя командами, сначала

записывается младший байт, а потом -

старший.

Таблица 5.12. Адресация внутренних регистров КПДП

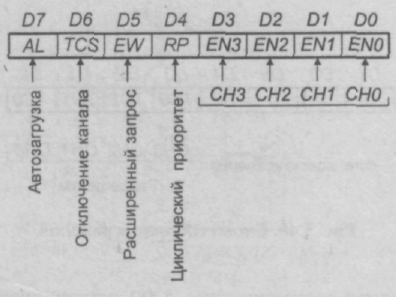

Режим работы каналов задается управляющим словом, формат которого показан на рис. 5.47. Разряды D3-D0 (EN3-EN0) разрешают (при единичном значении) или запрещают (при нуле) обмен по соответствующему каналу.

|

Рис. 5.47. Формат управляющего слова |

Разряд

D4(RP)

устанавливает порядок обслуживания

запросов от каналов. При D4=0

задается фиксированный приоритет

каналов, при D4=1

устанавливается режим циклического

приоритета. Циклический сдвиг

приоритетов происходит после каждого

цикла прямого доступа. Установка

разряда D5(FW)

в единицу задает режим расширенной

записи, при которой продолжительность

сигналов

|

Это позволяет УВВ, формирующему сигнал READY по фронту сигнала записи, уменьшить или увеличить скорость обмена.

При D6(TC)=1 появление сигнала ТС в одном из каналов сбрасывает соответствующий разряд D3-D0, в результате чего канал отсоединяется, и его дальнейшая работа возможна после перезагрузки регистра режима. Если D6(TCS)=0, то появление сигнала ТС не влияет на разряд разрешения работы канала и заканчивать передачу должно УВВ прекращением выработки сигнала DRQ.

Единичное значение разряда D7(AL) задает режим автозагрузки, в котором работает только второй канал, используя содержимое своих внутренних регистров и внутренних регистров третьего канала. После передачи данных соответственно параметрам регистров второго канала с появлением сигнала ТС содержимое регистров третьего канала автоматически загружается в регистры второго канала. При этом в регистре состояния каналов (рис. 5.48) устанавливается в логическую единицу разряд D4(UF)-флаг восстановления. Затем передача данных продолжается соответственно новым параметрам регистров второго канала, а в конце первого цикла прямого доступа с новыми параметрами флаг восстановления сбрасывается. Режим автозагрузки позволяет организовывать повторные пересылки блоков данных с одинаковыми параметрами или соединять несколько блоков с разными параметрами.

|

Рис. 5.48. Слово состояния каналов |

Разряды D3-D0 слова состояния (рис. 5.48) устанавливаются одновременно с появлением сигнала ТС соответствующего канала и сбрасываются cm налом RESET при чтении содержимого регистра состояния. Флаг восстановления UF можно сбросить записью логического нуля в разряд D7 регистра режима {рис. 5.47). |

Начальный адрес ОЗУ задается записью двух байт в регистры каналов RG0-RG3.

Длина массива памяти и направление обмена информацией между памятью и устройством ввода/вывода задаются записью двух байт в счетчики СТ0-СТЗ циклов. Два старших разряда счетчика циклов определяют направление обмена таким образом: запись в память - 01, считывание из памяти - 10, контроль - 00. Комбинация 11 является запрещенной. Другие разряды счетчика определяют число пересылаемых при обмене байт.

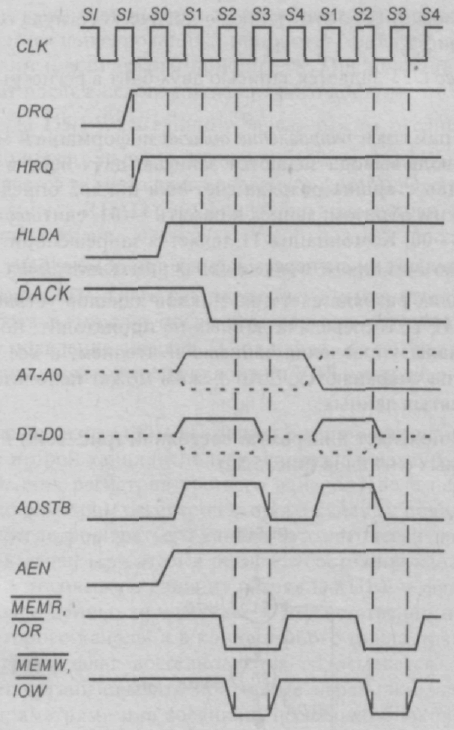

Если два старших разряда счетчика циклов каналов устанавливают режим контроля VERIFY, то передача данных не происходит, поскольку не генерируются сигналы управления записью и чтением, а все другие функции прямого доступа сохраняются. Этот режим может использоваться УВВ для контроля принятых данных. Работу КПДП поясняют временные диаграммы основных сигналов (рис. 5.50). После записи слова режима в регистр управляющего слова КПДП переходит

|

Рис. 5.50. Временные диаграммы основных сигналов |

в холостое состояние, которое длится до тех пор, пока на один из входов КПДП не поступит запрос DRQ от внешнего устройства на прямой доступ к памяти. Контроллер вырабатывает сигнал HRQ и ожидает поступления сигнала подтверждения HLDA от МП. После поступления сигнала HLDA начинается цикл обмена. Формируется сигнал AEN для блокирования других устройств системы от шин данных и управления, выдается код младших разрядов на выходы А7-А0, а код старших разрядов - на выходы D7-D0.

Выдача

старших разрядов адреса сопровождается

стробом ADSTB

для записи их во внешний буферный

регистр.

Формируются сигналы

Состояние КПДП можно контролировать чтением |

Содержимого RGA, СТ и 8-разрядного регистра состояния, общего для всех каналов, с помощью команды in. Для чтения содержимого 16-разрядного регистра используются две команды in с одним и тем же адресом, причем сначала происходит считывание младшего байта, а затем старшего.