- •Федеральное агентство образования российской федерации

- •Кафедра «Электронные, радиоэлектронные и электротехнические системы» курсовой проект по дисциплине «Цифровые устройства и микропроцессоры»

- •Часть 1. Разработка устройства логического управления ……………….………4

- •Часть 2. Разработка таймера на основе микроконтроллера ……………………23

- •Часть 1. Разработка устройства логического управления.

- •Структурный синтез устройства и выбор элементной базы

- •1.1 Структурный синтез устройства, формирующего условия переходов

- •1.2 Структурный синтез дискретного автомата

- •1.3 Синтез декодера выходных состояний

- •1.4 Выбор элементной базы

- •Синтез вспомогательных логических устройств

- •2.2 Синтез таймера

- •Синтез тактового генератора

- •Синтез устройства индикации

- •Синтез устройства начального пуска

- •Моделирование

- •3.1 Моделирование автомата

- •3.2 Моделирование таймера и тактового генератора

- •Часть 2. Разработка таймера на основе микроконтроллера.

- •Анализ задания и составление функциональной схемы

- •Выбор элементной базы

- •6.1 Выбор микропроцессорного устройства

- •6.2 Выбор устройства индикации

- •Устройство звуковой сигнализации

- •Разработка принципиальной схемы системы

- •Разработка алгоритма работы таймера

- •8.1 Словесное описание

- •8.2 Блок-схема алгоритма работы таймера

- •Разработка программы

- •Моделирование

Часть 1. Разработка устройства логического управления.

-

Структурный синтез устройства и выбор элементной базы

1.1 Структурный синтез устройства, формирующего условия переходов

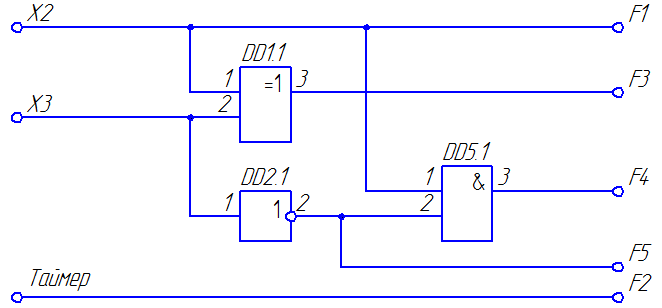

Для синтеза устройства, преобразующего входные логические сигналы X1, X2, X3 в условия переходов F1, F2, F3, F4, F5, запишем каждое из условий в виде логических функций сигналов X1, X2, X3. Согласно данным задания, имеем следующие функции переходов:

![]() – логическая

функция сигналов X1,

X2,

X3

:

– логическая

функция сигналов X1,

X2,

X3

:

![]() ,

если X

= 2,3,6,7, иначе

,

если X

= 2,3,6,7, иначе

![]()

![]() – временная

задержка 35 с.

– временная

задержка 35 с.

![]()

![]()

![]()

Функция перехода

![]() реализуется с помощью таймера. Реализация

таймера будет рассмотрена в п.

реализуется с помощью таймера. Реализация

таймера будет рассмотрена в п.

Функцию переходов

![]() целесообразно упростить, однако прежде

реализуем функцию

целесообразно упростить, однако прежде

реализуем функцию

![]() .

Для этого составим таблицу истинности

(табл. 1)

.

Для этого составим таблицу истинности

(табл. 1)

|

X |

X1 |

X2 |

X3 |

F1 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

0 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

1 |

логическим сигналом Х2. Это можно доказать путём записи совершенной дизъюнктивной нормальной функции:

Упростим функции

![]()

![]() Итак, в итоге

мы получили функции переходов, которые

необходимо реализовать на дискретных

логических элементах. Принципиальная

схема устройства преобразования входных

логических сигналов представлена на

рис.1

Итак, в итоге

мы получили функции переходов, которые

необходимо реализовать на дискретных

логических элементах. Принципиальная

схема устройства преобразования входных

логических сигналов представлена на

рис.1

Рис. 1 Устройство преобразования входных логических сигналов

1.2 Структурный синтез дискретного автомата

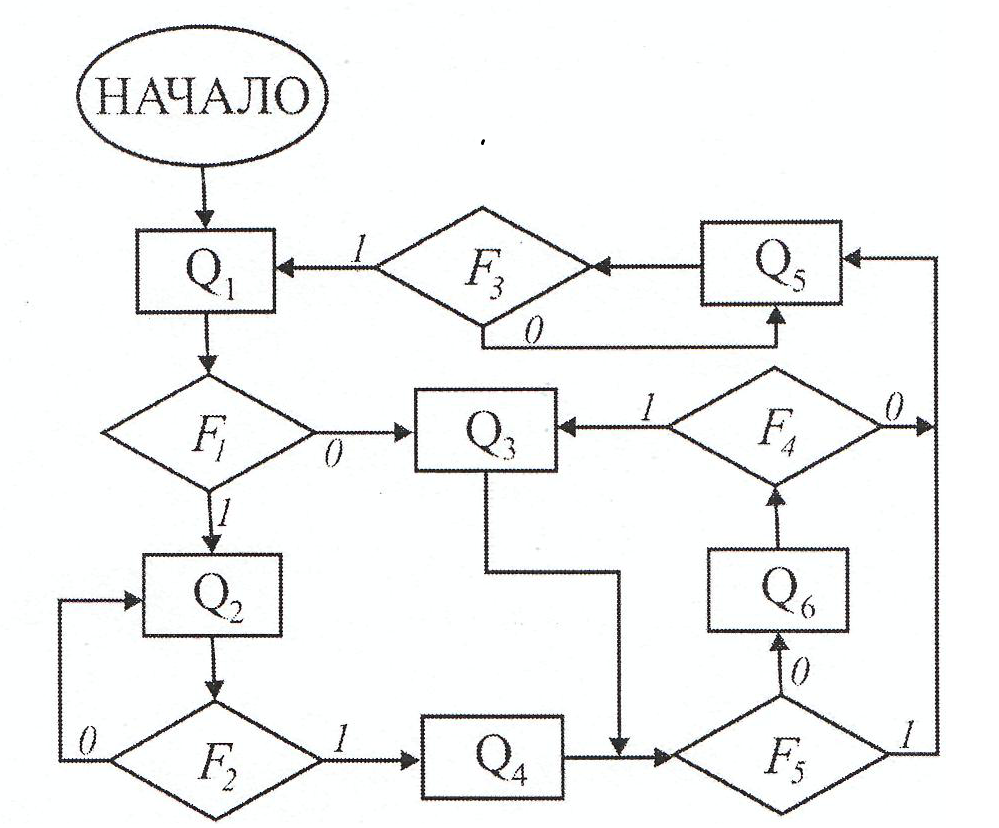

Синтезируем устройство, принцип функционирования которого должен отвечать алгоритму, приведенному на рис. 2

Рис. 2 Алгоритм работы устройства логического управления

где Q1, Q2, Q3, Q4, Q5, Q6 – внутренние состояния автомата, а F1, F2, F3, F4, F5 – условия переходов.

Требуемый объем памяти для автомата определяется по следующей формуле:

![]() ,

где n

– число ячеек памяти, N

– число внутренних состояний автомата.

Так как число внутренних состояний

автомата равно

,

где n

– число ячеек памяти, N

– число внутренних состояний автомата.

Так как число внутренних состояний

автомата равно

![]() ,

получим, что для реализации устройства

логического управления нам необходимо

3 ячейки памяти, т.е.

,

получим, что для реализации устройства

логического управления нам необходимо

3 ячейки памяти, т.е.

![]() .

.

Закодируем

внутренние состояния автомата

![]()

|

Q |

Z2 |

Z1 |

Z0 |

|

Q1 |

0 |

0 |

0 |

|

Q2 |

0 |

0 |

1 |

|

Q3 |

0 |

1 |

0 |

|

Q4 |

0 |

1 |

1 |

|

Q5 |

1 |

0 |

0 |

|

Q6 |

1 |

0 |

1 |

Составим направленный граф, в котором укажем все возможные переходы согласно алгоритму. С учётом кодирования граф будет представлен в следующем виде:

Рис. 3 Направленный граф автомата

Проверим составленный граф на непротиворечивость, т.е. дизъюнкция попарных конъюнкций условий перехода для каждой вершины должна быть тождественна 0:

Проверим граф на полноту, т.е. дизъюнкция всех условий перехода из каждой вершины должна быть тождественна 1:

Направленный граф автомата составлен верно. Теперь мы можем перейти к реализации синхронного автомата Мура на основе D-триггеров. Для этого необходимо составить функции возбуждения памяти, которые записываются в виде дизъюнкции конъюнкций разрядов состояний (включая тот разряд, для которого записывается функция) и условия переходов. В функцию входят только те переходы и состояния, в которых требуемый разряд переходит из «0» в «1» или сохраняет при переходе единичное значение, т.е. переходит из «1» в «1». Для записи функций составим соответствующую таблицу (табл. 2)

Таблица 3

|

Q1..6 |

|

Q1..6 |

|

D0 |

D1 |

D2 |

||||

|

Z2 |

Z1 |

Z0 |

Z2 |

Z1 |

Z0 |

|||||

|

0 |

0 |

0 |

|

0 |

0 |

1 |

|

|

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

||

|

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

||

|

0 |

0 |

1 |

0 |

1 |

1 |

|

|

0 |

||

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

|

||

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

|

||

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

||

|

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

|

||

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

||

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

||

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

||

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

||

На основании таблицы для каждого из разрядов получаем следующие функции возбуждения:

![]()

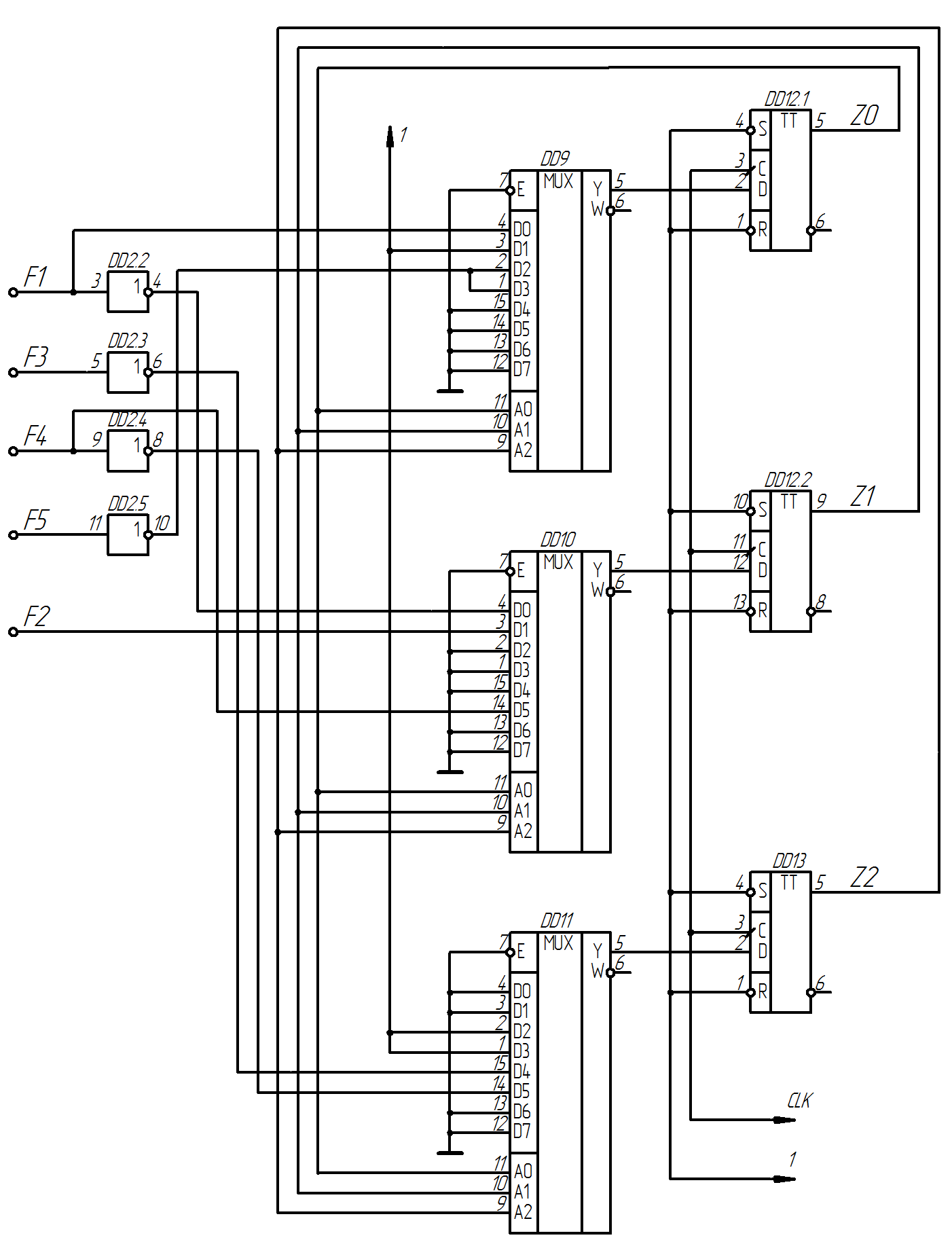

Входное комбинационное логическое устройство по заданию курсового проекта, необходимо реализовать на основе восьмивходовых мультиплексоров. Таким образом уравнение мультиплексора в общем виде:

![]()

Согласно функциям возбуждения памяти получаем следующие уравнения для мультиплексоров:

![]()

![]()

![]()

На

информационные входы мультиплексоров

![]() ,

,

![]() ,

,

![]() подаются

соответствующие функции переходов,

согласно функциям возбуждения. На

адресные входы

подаются

соответствующие функции переходов,

согласно функциям возбуждения. На

адресные входы

![]() мультиплексоров

подадим комбинации выходных сигналов

триггеров

мультиплексоров

подадим комбинации выходных сигналов

триггеров

![]() ,

,

![]() и

и

![]() .

.

Составим таблицу для информационных входов мультиплексоров (табл. 4)

Таблица 4

|

Информационный вход |

|

|

|

|

|

|

|

0 |

|

|

1 |

|

0 |

|

|

|

0 |

1 |

|

|

|

0 |

1 |

|

|

0 |

0 |

|

|

|

0 |

|

|

|

|

0 |

0 |

0 |

|

|

0 |

0 |

0 |

Принципиальная схема устройства изображена на рис. 4.

Рис. 4 Устройство логического управления