- •А. В. Бубнов, к. Н. Гвозденко, м. В. Гокова аналоговая и цифровая схемотехника

- •Оглавление

- •Введение

- •Математические основы проектирования цифровых устройств

- •Понятие системы счисления. Ее типы

- •Перевод чисел из десятичной системы счисления в любую не десятичную

- •Перевод чисел из любой не десятичной системы счисления в десятичную

- •Перевод чисел из двоичной системы счисления в шестнадцатеричную (восьмеричную) и обратно

- •Основы алгебры логики

- •Логические функции

- •Правила алгебры логики

- •Составление логических функций

- •Минимизация логических функций

- •Принципы построения простейших логических элементов

- •Логические устройства

- •Комбинационные логические устройства

- •Простейшие логические элементы

- •Сложные логические элементы

- •Реализация логических функций на логических элементах

- •Дешифраторы

- •Шифраторы

- •Демультиплексоры и мультиплексоры

- •Цифровые вычислительные устройства

- •Сумматоры цифровых кодов

- •Полный одноразрядный сумматор

- •Многоразрядные сумматоры

- •Вычитание двоичных сигналов (кодов)

- •Арифметико-логическое устройство

- •Алгоритм проверки на четность и нечетность

- •Сравнение двоичных чисел

- •Умножители двоичных чисел

- •Тактируемые цифровые устройства

- •Цифровые запоминающие устройства

- •Триггеры

- •Асинхронные триггеры

- •Синхронные триггеры

- •Двухтактные триггеры

- •Регистры

- •Счётчики импульсов

- •Асинхронные счётчики импульсов

- •Счетчики с переносом

- •Синхронные счётчики

- •Распределители сигналов

- •Импульсный частотно-фазовый дискриминатор

- •Устройства согласования работы цифровых устройств

- •Устройства, согласующие работу элементов цифровой и аналоговой техники

- •Цифроаналоговые преобразователи

- •Аналогово-цифровые преобразователи

- •Ацп со сравнением входного преобразуемого сигнала с дискретными уровнями напряжений

- •Ацп с зарядом конденсатора (интегрирующие ацп)

- •Аналоговые Интегральные Схемы

- •Усилители с отрицательной обратной связью

- •Инвертирующий и неинвертирующий усилители

- •Дифференциальные усилители

- •Интеграторы

- •Дифференциаторы

- •Перемножители напряжений

- •Компараторы

- •Аналоговые ключи

- •Библиографический Список

Синхронные триггеры

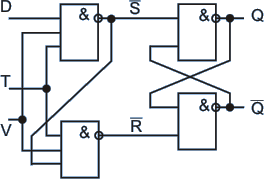

RS-триггер. В основе этой схемы лежит асинхронный RS-триггер, по входам которого устанавливаются 2 цифровых ключа 2И-НЕ. Эти ключи управляются дополнительным тактовым импульсом T, поэтому информация с входа R и S приходит на входы асинхронных триггеров только при поступлении импульса T. На рисунке 3.30 показана функциональная схема и временная диаграмма тактируемого RS-триггера.

Рис. 3.35. Однотактный RS-триггер (слева) и его временные диаграммы (справа)

В

синхронном триггере могут быть

предусмотрены входы асинхронной

установки

и

и

.

По этим входам состояние триггера может

быть изменено в любой момент времени

(рис. 3.31).

.

По этим входам состояние триггера может

быть изменено в любой момент времени

(рис. 3.31).

Рис. 3.36. Функциональная схема однотактного RS-триггера с входами асинхронной установки (слева) и его УГО (справа)

Триггер

D-типа. Основным

недостатком вышерассмотренного

тактируемого RS-триггера

является наличие двух информационных

входов. В то же время в режиме записи в

него информации на входах R

и S

должны присутствовать противоположные

сигналы. Поэтому из тактируемого

RS-триггера

получают тактируемый

D-триггер путём

замещений входа S

на вход D

и подачи на вход R

сигнала

(рис. 3.32). Таким образом, D-триггеры

имеют один информационный вход.

(рис. 3.32). Таким образом, D-триггеры

имеют один информационный вход.

|

|

|

|

|

а) |

б) |

в) |

|

Рис. 3.37. Однотактный D-триггер: его функциональная схема (а), УГО (б) и временные диаграммы (в)

|

||

|

Рис. 3.38. DV-триггер |

DV-триггер (рис. 3.33). Этот триггер дополнительно снабжен входом разрешения работы, который может блокировать его работу. По сути, действие данного входа аналогично действию T входа. Поэтому структурно этот вход может быть выполнен как объединение дополнительных входов элементов

И-НЕ входной логики триггера.

Триггер T-типа (счётный триггер). T-триггер называется счётным, т.к. при поступлении тактового импульса его выходное состояние инвертируется, что эквивалентно прибавлению к выходному состоянию единицы по модулю два. Счётный триггер лежит в основе построения практически всех счётчиков импульсов (рис. 3.34).

|

|

|

|

Рис. 3.39. Однотактный T-триггер (слева) и однотактный TV-триггер (справа) |

|

Во

время паузы тактового импульса T

через время задержки τз

на входе S

появляется сигнал, соответствующий

,

а на входе R – Q, поэтому при приходе

следующего тактового импульса эта

информация записывается в триггер и в

результате состояние триггера меняется

на противоположное.

,

а на входе R – Q, поэтому при приходе

следующего тактового импульса эта

информация записывается в триггер и в

результате состояние триггера меняется

на противоположное.

Для надёжной работы схемы должно выполняться условие Tи < τз < Tпаузы. Иначе, если к моменту изменения сигналов на входах R и S сигнал T еще не снят, происходит следующее переключение триггера, в результате устройство начинает функционировать как мультивибратор (генератор прямоугольных импульсов) до тех пор, пока не будет снят сигнал T.

Разновидностью T-триггера является TV-триггер (рис. 3.34) и отличается от него дополнительным входом V – разрешения работы. При V = 1 работа триггера разрешена.