- •3. Задание на лабораторную работу

- •Исходные данные к работе

- •3. Методические указания

- •3.1. Работа с системой «Matlab»

- •3.3. Работа с ассемблером и симулятором процессора adsp2181

- •3.3. Работа с отладочной платой ez-Kit Lite процессора adsp2181

- •4. Содержание отчета.

- •Общие сведения

- •5.1. Сигналы с частотной манипуляцией и непрерывной фазой

- •5.2. Алгоритмы цифрового формирования сигналов чмнф и чмнф гф

- •6. Контрольные вопросы.

- •7. Список литературы

- •Приложение Подпрограмма формирователя сигналов чмнф

- •Подпрограмма формирователя сигналов гммс

5.2. Алгоритмы цифрового формирования сигналов чмнф и чмнф гф

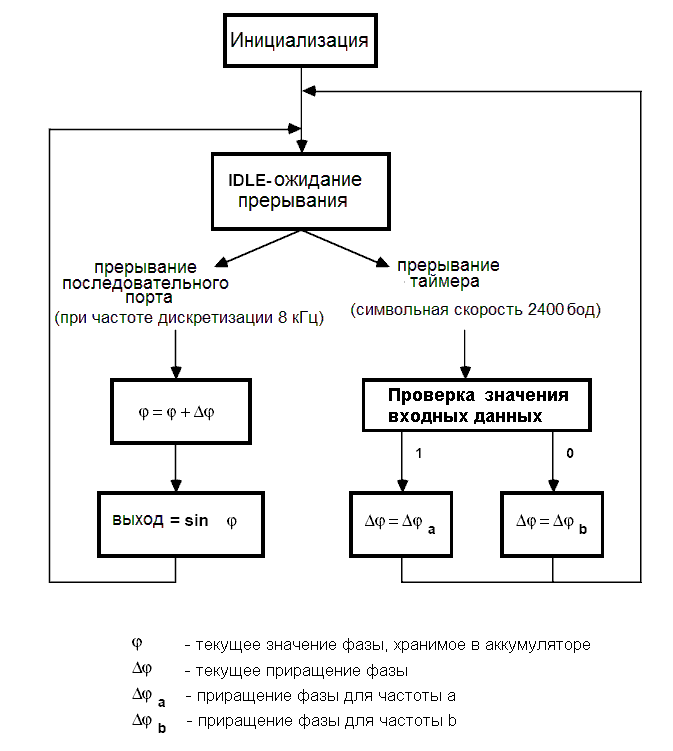

На рис. 1. показан алгоритм, реализованный на процессоре серии ADSP-21хх на примере процессора ADSP-2101 [5], в этом примере показаны преимущества серийных портов и таймера, находящихся в микросхеме. Таймер вырабатывает синхроимпульсы с символьной скоростью 2400 бод для чтения входных данных. Процессор ADSP-2101 подает модулированные ЧМНФ данные на цифроаналоговый преобразователь (ЦАП) со скоростью 8 кГц. Обычно, данные поступают от входного устройства, и их можно прочитать с помощью функции FI (Flag In), на входе ADSP-2101.

Алгоритм формирования сигналов ЧМНФ содержит не показанные здесь две внешние подпрограммы. Подпрограмма Boot_sin вычисляет синус входа в AX0, возвращая на выходе AR. После загрузки (инициализации переменных, и т.д.) процессор ожидает одно из двух прерываний. Прерывание SPORT0 заставляет процессор вычислять следующий выходной отсчет, добавляя текущее приращение фазы к сумматору фазы и вычисляя синус результата. Выходные отсчеты передаются от SPORT0 и также посылаются в ЦАП.

Прерывания таймера заставляют процессор выбирать новое приращение фазы, основанное на значении данных входа. Поскольку данные являются двоичными (1 или 0), их можно вводить с помощью flag input (FI), а не из памяти данных, как показано на рисунке. Код необходимо изменить, чтобы использовать режим input flag как условие для выбора приращения фазы.

На вход модулятора Частотной манипуляции с непрерывной фазой (ЧМНФ) поступает: поток данных, обычно хранящихся в циклическом буфере DM (памяти данных), данные могут быть вида: FLAG_IN: pin (вывод FLAG IN).

К достоинствам данного алгоритма следует отнести простоту реализации и небольшой необходимый объем памяти, так как нет необходимости хранить значения таблицы синуса (формирование синусоидального колебания производится методом аппроксимации).

Рис.1. Алгоритм реализации ЧМНФ колебания на ЦСП ADSP-2101

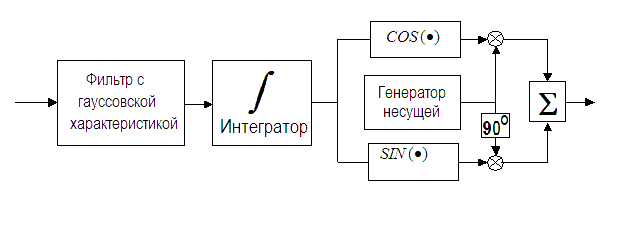

Формирование сигналов с минимальным частотным сдвигом возможно на основе обычного квадратурного модулятора. На вход поступает цифровая последовательность, а на выходе квадратурного модулятора (после сложения двух квадратурных сигналов) формируется сигнал ММС. По существу на обычный модулятор КФМ подается последовательность не прямоугольных импульсов, а импульсов с огибающей близкой к синусоиде. В результате энергия сигнала постоянно перераспределяется между квадратурными составляющими.

Рис. 2. Алгоритм формирования сигнала ЧМНФ ГФ.

Алгоритм формирования сигнала ЧМНФ ГФ можно представить в виде структурной схемы, показанной на рис.2 [1]. На входе фильтра действует биполярная последовательность, сформированная из входной битовой последовательности, на выходе ФНЧ с гаусовской импульсной характеристикой получаем отклик, который поступает на вход интегратора. Поскольку после интегратора стоят блоки периодических функций sin и cos, то интегрирование удобно производить по модулю . Затем синфазная и квадратурная составляющие сигнала поступают на перемножители, где происходит перенос на высокую частоту. При сложении синфазных и квадратурных составляющих получаем сигнал ЧМНФ ГФ.