- •Аналоговые и цифровые сигналы

- •Элементы цифровой вычислительной техники

- •Синтез комбинационных схем

- •Сднф, скнф

- •Выбор базиса

- •Методы минимизации. Минимизация системы уравнений в заданном базисе с использованием карт Карно

- •Сложность схемы по Квайну

- •Расчет быстродействия схемы

- •Транзисторно-транзитивная логика

- •Дешифратор. Виды дешифраторов

- •Синхронизированный rs-триггер

- •Синхронный d-триггер

- •Jk-триггер

- •Т-триггер

- •Закон функционирования триггера

- •Суммирующие и вычитающие счетчики

- •Реверсивные счетчики

- •Регистры, сдвигающие регистры

- •Реверсивный регистр на d-триггерах

- •Сумматоры, одноразрядный сумматор

- •Параллельный сумматор с последовательным переносом

- •Сумматор с параллельным переносом

- •Мультиплексоры

- •Демультиплексоры

- •Шифратор

- •Программируемая логическая матрица

- •Управляющие цифровые автоматы

- •Микропроцессоры

- •Основные микрооперации операционного блока

- •Содержательная, закодированная, отмеченная граф-схема алгоритмов

- •Синтез управляющих автоматов

- •Микропрограммные автоматы с программированной логикой

- •Синтез автоматов с программируемой логикой

- •Кодирование адресной части, мпа

- •Кодирование постоянного запоминающего устройства. Кодирование микрокоманды с естественной адресацией

- •Построение функциональной схемы

- •Операционные усилители

- •Обратные связи в усилительных устройствах

- •Усилительные каскады переменного и постоянного тока

- •Вторичные источники питания

- •Решающие усилители

- •Частотные и переходные характеристики

- •Схемы замещения полупроводниковых приборов

- •Активные фильтры

- •Аналоговые компараторы напряжений

- •Аналоговые ключи и коммутаторы

- •Источники эталонного напряжения и тока

Синхронизированный rs-триггер

Синхронизированный RS-триггер

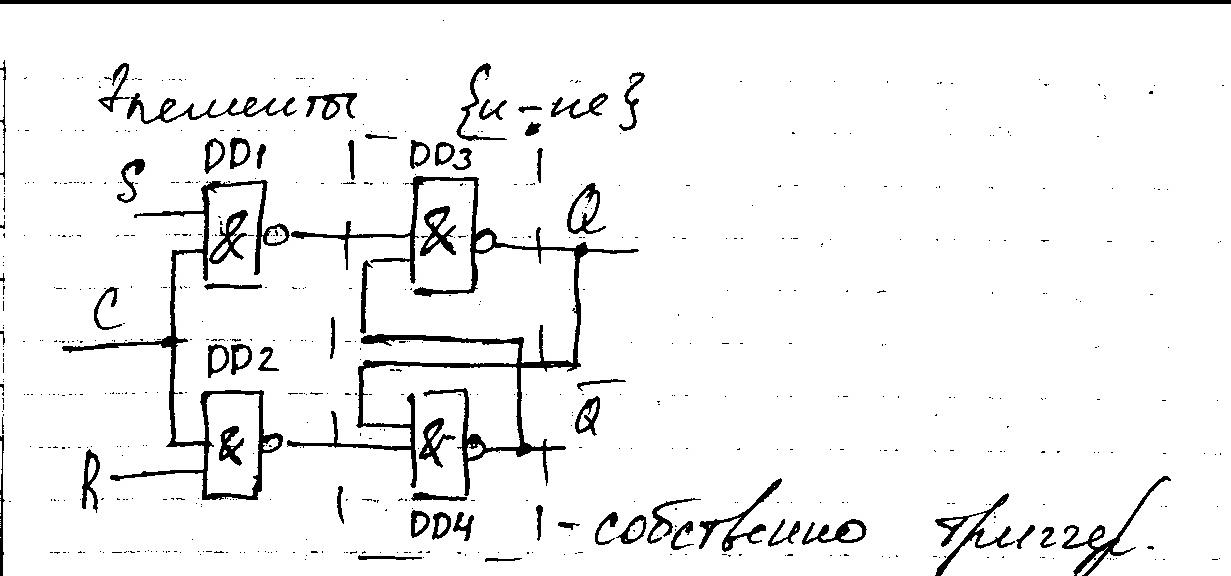

Синхронизированные RS-триггеры могут строится на элементах{или,не}

Особенностью этих триггеров является, то что они имеют дополнительный вход управлений который называется – синхронизированный в отсутствии сигнала. На этом входе триггер сохраняет представление состояние и можно в этот момент менять состояние на входах SR, причем выполняется состояние S=R=1 при этом критерии обычный триггер работает не устойчиво и неопределенно

Уравнение такого вида

Q(t)=неC ∙Q (t-1)vC((Sv(неR)∙Q)∙(t-1))

Q(t)- последнее состояние триггера

не С- состояние на синхросигнале

Q(t-1) – предыдущее состояние

S – состояние установочного входа S

R – состояние обнуляющего входа R

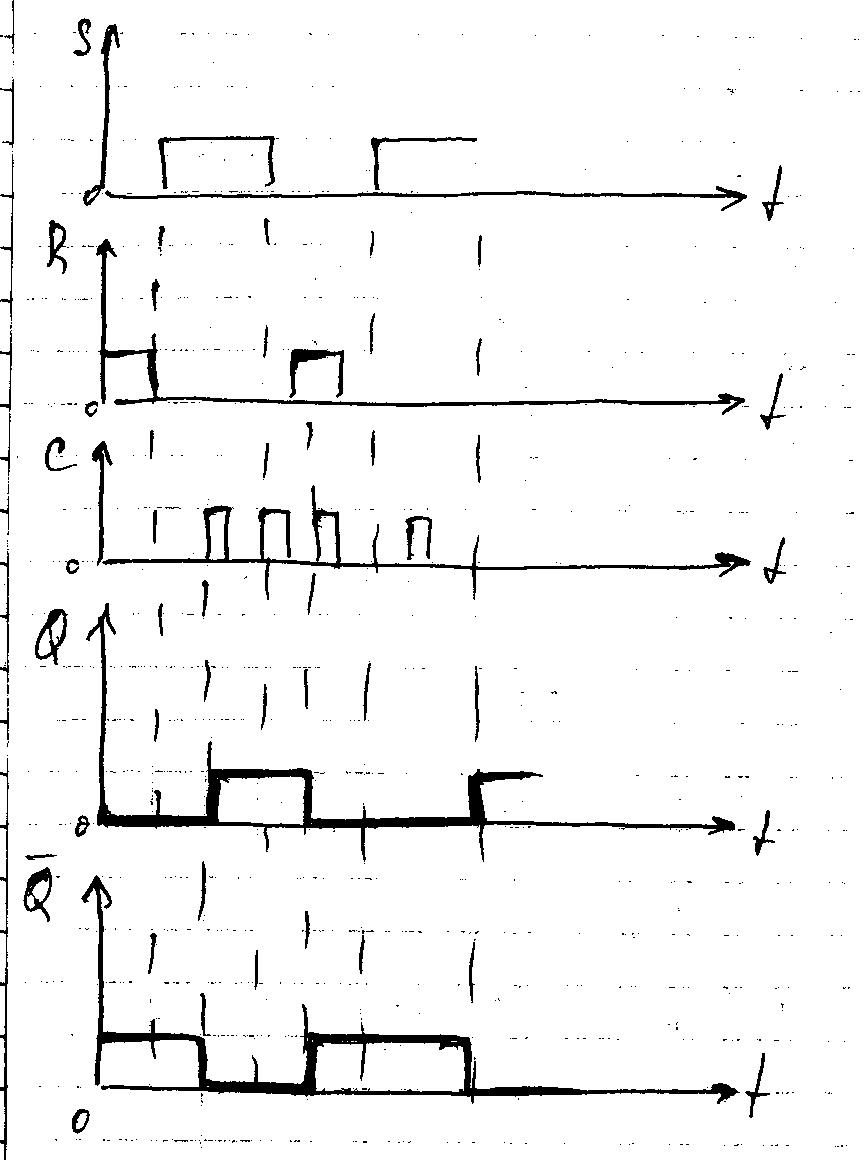

При отсутствии синхросигнала триггер работает т.к. обычно RS- триггер. На выходе Q будет 1, на выходе не Q = 0 (при подаче на вход R единицы)

Рассмотрим схем синхронизированного RS-триггера на электродах & не

Элементы DD1 и DD2 являются коммутирующими и зависящие от состояния синхро вход. Если на синро входе С, то на выходе этих элементов 11, любой 0 на входе дает на выходе 1

Единственные выходы с этих элементов в последующем не влияют на состояние собственно триггер. Собранный на элементах DD3,DD4 ион хранит своё предыдущее состояние (режим хранения). При этом как бы мы не меняли состояние входов S и R они не влияют на работу триггеров.

Режим установки в единицу на вход S подается 1 на входы -0 и после того как установившись состояние этих входов, подается синхросигнал.

С подачей синхросигнала срабатывает элемент DD1.На его входах появляются 2 единицы на выходе 0 . На выходе DD2 – 1,т.к. на входе R-0 элемент DD3 в соответствии с “0” на выходе DD1 переключается на “1”. При этом эта “1” поступает на вход DD4 и на его входе появляется 2 логические “1” и он переключается в “0” и этот “0” в дальнейшем удерживает триггер в единичном состоянии. Замети, что данный триггер срабатывает на передний фронт, который на схеме рисуемая Δ-ым триггером.

В момент включения триггер устанавливается в произвольное значение что бы избегать этого его специально обнуляют перед выключением.

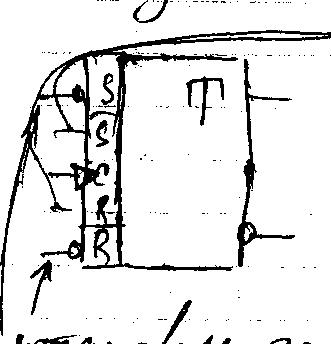

Триггер имеет 2 установочных входа, 1 или установочные входы 2 информационных. Установочные входы рисуются в режиме начальной установки 1 начале работы.

Информационные – для организации преобразования информации – для выполнения микроопераций

RS- триггер используется в качестве основы для построения других триггеров, в частности D – JK –T триггеров.

Быстродействие триггеров определяется по формуле

=3cp+cp

Где cp – время срабатывания элементов триггера (среднее)

3 cp - время срабатывания собственно триггера

тр- DD1 иDD2

Недостатком является , по прежнему неопределённое состояние при S=R=1 и C=1 на информационных и синхровходе, а также необходимость парафазной передачи.

Парафазные передачи требуют в 2 раза больше проводов но распространению сигналов по шинам. Кроме того усложняются схемы устройств (счетчики, регистры и т.д.) посему, часто используют D-триггеры