- •1. Двоичные сигналы в цифровой технике

- •2. Интегральные технологии

- •3. Переключательные схемы. Логические элементы и (and), или (or), не (not)

- •4. Переключательные схемы. Логические элементы и-не (nand) или-не (nor) исключающее или (xor), эквивалентность (xnor), буфер

- •5. Ассоциативность функций и (and), или (or), и-не (nand) или-не (nor), xor, xnor.

- •6. Степени интеграции микросхем. Позитивная и негативная логика

- •7. Операции кубического исчисления конъюнкция (and), дизъюнкция (or), исключающее или (xor)

- •8. Операции кубического исчисления пересечение, объединение и дополнение

- •9. Кубические покрытия элементов и (and), или (or), и-не (nand) или-не (nor), xor, xnor (доделать!!!)

- •10. Два подхода в минимизации систем булевых функций

- •11. Автоматизация проектирования

- •12. Сумматоры

- •13. Мультиплексоры

- •14. Демультиплексоры

- •15. Дешифраторы

- •16. Шифраторы

- •17. Программируемые логические матрицы (плм или pla)

- •18. Программируемая матричная логика (пмл или pal)

- •19. Универсальные логические модули на основе мультиплексоров (lut)

- •20. Асинхронные триггеры: rs-триггер, r*s*-триггер

- •21. Асинхронные триггеры: jk-триггер, j*k*-триггер

- •22. Асинхронные триггеры: d-триггер, vd-триггер, т-триггер

- •23. Синхронные триггеры

- •24. Одноступенчатые и двухступенчатые триггеры

- •25. Параллельные регистры. Последовательные регистры

- •26. Последовательно-параллельные регистры

- •27. Синтез триггеров на базе других триггеров (доделать!!!)

- •28. Определение абстрактного цифрового автомата

- •29. Автомат Мили

- •30. Автомат Мура

- •32. Задание автомата графом переходов

- •33. Табличный способ задания автоматов

- •34. Автоматная лента

- •35. Задание автомата деревом функционирования

- •36. Матричный способ представления автомата

- •37. Алгоритм трансформации автомата Мура в автомат Мили

- •38. Алгоритм перехода от автомата Мили к автомату Мура

- •39. Концепция операционного и управляющего автомата

- •40. Принцип микропрограммного управления

- •41. Содержательные и закодированные гса

- •42. Канонический метод структурного синтеза сложного цифрового автомат

- •43. Канонический метод синтеза микропрограммных автоматов Мили

- •44. Кодирование состояний автоматов с целью минимизации аппаратурных затрат

- •45. Противогоночное кодирование состояний автоматов. Кодирование состояний автоматов, реализуемых на плис

- •46. Канонический метод синтеза микропрограммных автоматов Мура

- •47. Vhdl-модель управляющего автомата Мили

- •48. Vhdl-модель управляющего автомата Мура

- •49. Vhdl-модель операционного автомата

- •50. Синтез канонической структуры операционного автомата

- •51. Характеристики операционного автомата. Явление гонок в операционных автоматах

- •52. Эквивалентные операции и обобщенный оператор

- •53. Операционный автомат типа I

- •54. Операционный автомат типа м

- •55. Оа типа im с параллельной комбинационной частью

- •56. Оа типа im с последовательной комбинационной частью

- •57. Операционный автомат типа s

- •58. Дребезг механических переключателей и метод его устранения

- •59. Делитель частоты

49. Vhdl-модель операционного автомата

|

Десятичные слагаемые |

Слагаемые в прямых кодах |

Слагаемые в обратных кодах |

Сложение в дополнительных кодах |

Результат в прямых кодах |

|

-8 -9 |

11 1000 11 1001 |

11 0111 11 0110 |

11 1000 + 11 0111 1|10 1111 |

ПП– |

|

+9 +12 |

00 1001 00 1100 |

00 1001 00 1100 |

00 1001 + 00 1100 01 0101 |

ПП+ |

|

+7 +3 |

00 0111 00 0011 |

00 0111 00 0011 |

00 0111 + 00 0011 00 1010 |

+10 |

|

-2 -3 |

11 0010 11 0011 |

11 1101 11 1100 |

11 1110 + 11 1101 1|11 1011 |

11 0100 обр. + 1 11 0101 прям.

-5 |

|

+5 -8 |

00 0101 11 1000 |

00 0101 11 0111 |

00 0101 + 11 1000 11 1101 |

11 0010 обр. + 1 11 0011 прям. -3 |

Листинг 6.1 – VHDL-модель операционного модуля (автомата)

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity OA is

port(

Done, y1, y2, y3, y4, y5, y6, CLK: in STD_LOGIC; -- control signals

A : in STD_LOGIC_VECTOR(5 downto 0); -- summand

B : in STD_LOGIC_VECTOR(5 downto 0); -- summand

C : out STD_LOGIC_VECTOR(5 downto 0); -- sum

x1, x2, x3 : out STD_LOGIC; -- informative signals

pp: out STD_LOGIC -- overflow

);

end OA;

--}} End of automatically maintained section

architecture OA of OA is

-- enter your statements here --

signal RG:STD_LOGIC_VECTOR(5 downto 0); -- - register

signal SM:STD_LOGIC_VECTOR(5 downto 0); -- - register-adder

begin

process (CLK, y1, y2, y3, y4, y5, y6)

begin

if (CLK'event and CLK='1')then

If (y1 = '1' and y2 = '1') then

RG <=B;

SM <=A;

elsif (y3 = '1')then

SM <=SM(5 downto 4) & ((not SM(3 downto 0))+1);

elsif (y4 = '1')then

SM <= SM + (RG(5 downto 4) & ((not RG(3 downto 0))+1));

elsif (y5 = '1')then

SM <= SM + RG;

elsif (y6 = '1')then

pp <= '1';

else pp <= '0';

end if;

end if;

end process;

C <= SM when Done = '1' else (others =>'0');

x1<= '1'when SM(5 downto 4)="11" else '0';

x2<= '1'when RG(5 downto 4)="11" else '0';

x3<= '1'when SM(5 downto 4)="01" or SM(5 downto 4)="10" else '0';

end OA;

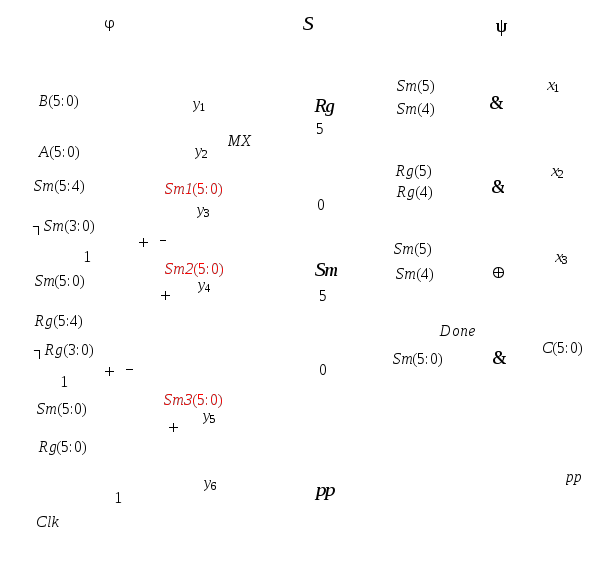

На рис. 6.4 Приведены временные диаграммы работы операционного автомата.

Рисунок 6.4 – Временные диаграммы работы операционного автомата

50. Синтез канонической структуры операционного автомата

Структуру операционного автомата можно синтезировать непосредственно по функции, заданной:

1) множеством слов S = {s1, …, sm, …sM}, которые могут быть входными, выходными, и внутренними.

Для примера на рис. 6.1 множество входных слов состоит из A(5:0) и B(5:0), множество выходных слов состоит из С(5:0), множество внутренних слов состоит из Sm(5:0), Rg(5:0) и рр.

2) множеством микроопераций Y = {y1, …, yg, …yG}.

Для примера на рис. 6.1 множество микроопераций состоит из y1, y2, y3, y4, y5, y6, Done.

3) множеством логических условий Х = {x1, …, xf, …xF}. Для примера на рис. 6.1 множество микроопераций состоит из логических условий x1, x2, x3.

Структура автомата синтезируется следующим образом.

1. Словам, описанных в качестве внутренних ставятся в соответствие регистры с длинами, равными длинам слов.

Sm(5:0) – шестиразрядный регистр, Rg(5:0) – шестиразрядный регистр, рр – триггер.

2. Словам, описанных в качестве входных ставятся в соответствие внешние входы схемы, которые соединяются с регистрами шиной, исходящей из входов.

3. Словам, описанных в качестве выходных ставятся в соответствие внешние выходы схемы, которые соединяются с регистрами шиной, входящей в выходы.

4. Каждой микрооперации yi Y, описываемой оператором присвоения (:=) ставится в соответствие комбинационная схема φ i φ (рис. 5.2), входы которой подключаются к регистрам и выходы которой соединяются с управляемой шиной регистра. Управляемая шина помечается сигналом yi, инициирующим микрооперацию – присвоение слову значение некоторой функции. Для выполнения микрооперации передачи не требуется, комбинационная схема, вычисляющая значение некоторой функции. Поэтому структурная реализация микрооперации передачи, обеспечивается управляемой шиной, соединяющей регистр с регистром и отмеченной соответствующим управляющим сигналом. Аналогично микрооперации установки (S:= const) реализуется управляющей шиной, начало которой отмечается константой const и соответствующим управляющим сигналом.

5. Каждому логическому условию xf ставится в соответствие комбинационная схема ψ f ψ, входы которой соединяются с регистром, а выходы с отмечаются осведомительным сигналом xf . Если ψ f тривиальная функция, которая, например, показывает содержимое разряда (разрядов) регистра, то логическое условие изображается шиной. Выход шины соответствует осведомительному сигналу.

Каноническая структура имеет вид, представленный на рис. 6.15.

В соответствии с данной моделью операционный автомат разделяется на три части: память S; комбинационную схему φ, реализующую функции φ i, связанные с выполнением микроопераций Y; комбинационную схему ψ, вычисляющую значения логических условий Х.

Функционирование операционных автоматов. Операционный автомат функционирует во времени в порядке, определяемом управляющим автоматом. Процесс функционирования разделяется на интервалы времени, называемые тактами. В течение такта выполняются следующие действия:

1) управляющий автомат формирует набор из одного, двух или более сигналов уа, ..., yw

2) под воздействием управляющих сигналов уа, ..., yw в комбинационных схемах φi автомата вычисляются значения двоичных выражений φ i(S), ..., φ i(S);

3) соответствующие регистры переключаются в новые состояния, определяемые значениями φ i(S), ..., φ i(S);

4) комбинационные схемы ψ вычисляют новые значения осведомительных сигналов X, соответствующие новому состоянию памяти S, т. е. новым значениям слов s1, …, sm. Длительность такта Т определяется структурой схем и быстродействием логических и запоминающих элементов, используемых в схемах управляющего и операционного автоматов.

Таким образом, такт – это промежуток времени между соседними моментами переключения состояния памяти. В течение такта память автомата переключается в новое состояние, отличное от предыдущего.

Операционный автомат можно рассматривать как самостоятельный объект. В таком случае термин «такт» условно применяется только к операционному автомату. Такт операционного автомата Т – это промежуток времени, необходимый для выполнения заданного набора микроопераций и вычисления значений логических условий, и равный интервалу времени от момента поступления на вход автомата управляющих сигналов до момента выработки значений осведомительных сигналов, соответствующих состоянию памяти автомата.

Обычно распределение действий во времени производится на основе синхронного принципа. При этом длительность такта Т определяется максимальным значением, необходимым для выполнения любой микрооперации и вычисления значения любого логического условия. Ход времени отмечается с помощью синхронизирующих сигналов, вырабатываемым генератором синхронизирующих импульсов, которые следуют с периодом, равным длительности такта Т. Эти сигналы используются для синхронизации моментов переключения триггеров.

Рисунок 6.15 – Каноническая структура ОА

На рис. 6.16 представлен фрагмент канонической структуры ОА - реализация мультиплексоров MX.

Рисунок

6.16 – Фрагмент каноническая структура

ОА

Рисунок

6.16 – Фрагмент каноническая структура

ОА