- •1. Двоичные сигналы в цифровой технике

- •2. Интегральные технологии

- •3. Переключательные схемы. Логические элементы и (and), или (or), не (not)

- •4. Переключательные схемы. Логические элементы и-не (nand) или-не (nor) исключающее или (xor), эквивалентность (xnor), буфер

- •5. Ассоциативность функций и (and), или (or), и-не (nand) или-не (nor), xor, xnor.

- •6. Степени интеграции микросхем. Позитивная и негативная логика

- •7. Операции кубического исчисления конъюнкция (and), дизъюнкция (or), исключающее или (xor)

- •8. Операции кубического исчисления пересечение, объединение и дополнение

- •9. Кубические покрытия элементов и (and), или (or), и-не (nand) или-не (nor), xor, xnor (доделать!!!)

- •10. Два подхода в минимизации систем булевых функций

- •11. Автоматизация проектирования

- •12. Сумматоры

- •13. Мультиплексоры

- •14. Демультиплексоры

- •15. Дешифраторы

- •16. Шифраторы

- •17. Программируемые логические матрицы (плм или pla)

- •18. Программируемая матричная логика (пмл или pal)

- •19. Универсальные логические модули на основе мультиплексоров (lut)

- •20. Асинхронные триггеры: rs-триггер, r*s*-триггер

- •21. Асинхронные триггеры: jk-триггер, j*k*-триггер

- •22. Асинхронные триггеры: d-триггер, vd-триггер, т-триггер

- •23. Синхронные триггеры

- •24. Одноступенчатые и двухступенчатые триггеры

- •25. Параллельные регистры. Последовательные регистры

- •26. Последовательно-параллельные регистры

- •27. Синтез триггеров на базе других триггеров (доделать!!!)

- •28. Определение абстрактного цифрового автомата

- •29. Автомат Мили

- •30. Автомат Мура

- •32. Задание автомата графом переходов

- •33. Табличный способ задания автоматов

- •34. Автоматная лента

- •35. Задание автомата деревом функционирования

- •36. Матричный способ представления автомата

- •37. Алгоритм трансформации автомата Мура в автомат Мили

- •38. Алгоритм перехода от автомата Мили к автомату Мура

- •39. Концепция операционного и управляющего автомата

- •40. Принцип микропрограммного управления

- •41. Содержательные и закодированные гса

- •42. Канонический метод структурного синтеза сложного цифрового автомат

- •43. Канонический метод синтеза микропрограммных автоматов Мили

- •44. Кодирование состояний автоматов с целью минимизации аппаратурных затрат

- •45. Противогоночное кодирование состояний автоматов. Кодирование состояний автоматов, реализуемых на плис

- •46. Канонический метод синтеза микропрограммных автоматов Мура

- •47. Vhdl-модель управляющего автомата Мили

- •48. Vhdl-модель управляющего автомата Мура

- •49. Vhdl-модель операционного автомата

- •50. Синтез канонической структуры операционного автомата

- •51. Характеристики операционного автомата. Явление гонок в операционных автоматах

- •52. Эквивалентные операции и обобщенный оператор

- •53. Операционный автомат типа I

- •54. Операционный автомат типа м

- •55. Оа типа im с параллельной комбинационной частью

- •56. Оа типа im с последовательной комбинационной частью

- •57. Операционный автомат типа s

- •58. Дребезг механических переключателей и метод его устранения

- •59. Делитель частоты

23. Синхронные триггеры

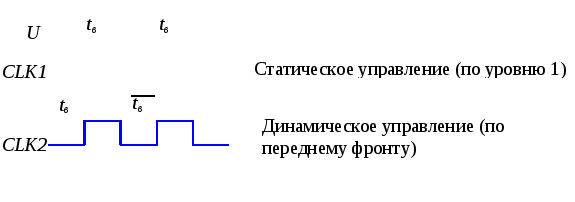

Синхронные триггеры – триггеры, у которых переход в новое состояние вызывается не только изменениями информационных сигналов, но и синхросигнала (синхронизирующего, тактирующего). Синхросигнал (тактовый сигнал) дважды в течение такта меняет свое значение. Примеры синхроимпульсов (CLK1, CLK2) приведены на рис. 3.16.

Рисунок 3.16 – Примеры синхроимпульсов

Синхронизирующий сигнал CLK имеет уровни 1, 0, передний фронт (или в некоторых источниках фронт) – переход из 0 в 1 и задний фронт (спад) – переход из 1 в 0 (рис. 3.17). Иногда условно передний фронт обозначают буквой E, а задний фронт – буквой H.

Рисунок 3.17 – Условные обозначения фронтов синхроимпульсов

Существует синхронизация по уровню (статическое управление) и по фронту (динамическое управление). В случае статического управления восприимчивость tв триггера к входным сигналам ограничивается временем, когда CLK=1 (по уровню 1) или CLK=0 (по уровню 0). Чаще всего это полтакта, а в общем случае это время, в течение которого синхросигнал принимает значение 1 (по уровню 1) или 0 (по уровню 0). Это часто накладывает временные ограничения на схему, где эти триггеры используются.

Чтобы уменьшить время, в течение которого триггер был бы чувствителен к изменению состояния, используют динамическую синхронизацию. В данном случае триггер чувствителен к изменению состояния в течение короткого промежутка времени – в окрестностях фронта (спада) (см. рис. 3.18). Это дает преимущество перед другими триггерами, поскольку таким триггером легче управлять. Вероятность неожиданных переключений такого триггера сводится к нулю.

Если триггер асинхронный, он чувствителен к изменению состояния в течении всего времени функционирования. Статически управляемые триггеры называют latch, динамически управляемые триггеры называют flip-flop.

Рисунок 3.18 – Статическая и динамическая синхронизации

Условные обозначения триггеров с различными типами синхронизации приведены на рис. 3.19 на примере RS-триггера.

Рисунок 3.19 – Условные обозначения RS-триггеров

Сокращенная таблица переходов синхронного RS-триггера по уровню 1 приведена в табл. 3.27.

Таблица 3.27 – Сокращенная таблица переходов синхронного RS-триггера по уровню 1

|

С |

R |

S |

Q t+1 |

|

0 |

0 |

0 |

Q t |

|

0 |

0 |

1 |

Q t |

|

0 |

1 |

0 |

Q t |

|

0 |

1 |

1 |

Q t |

|

1 |

0 |

0 |

Q t |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

х |

Сокращенная таблица переходов синхронного RS-триггера по переднему фронту приведена в табл. 3.28.

Таблица 3.28 – Сокращенная таблица переходов синхронного RS-триггера по переднему фронту

|

С |

R |

S |

Q t+1 |

|

Е |

0 |

0 |

Q t |

|

Е |

0 |

1 |

1 |

|

Е |

1 |

0 |

0 |

|

Е |

1 |

1 |

х |

|

0 |

х |

х |

Q t |

|

1 |

х |

х |

Q t |

|

H |

х |

х |

Q t |

Для понимания разницы в работе между выше приведенными триггерами (рис. 3.19), необходимо разобраться во временных диаграммах, приведенных на рис. 3.20.

Рисунок 3.20 – Временные диаграммы работы RS-триггеров

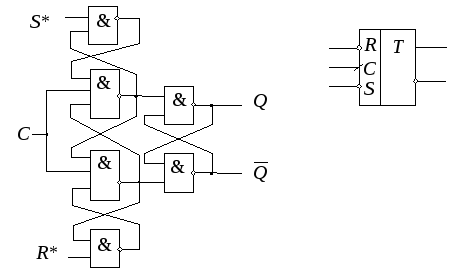

Преимущество, которое дает динамическая синхронизация достигается усложнением внутренней структуры триггера. На рис. 3.21 и 3.22 для сравнения приведены структуры двух триггеров типа R*S* - синхронизируемого уровнем 1 и передним фронтом. Структура асинхронного R*S*-триггера приведена на рис. 3.3.

Рисунок 3.21 – Структура и условное обозначение R*S*-триггера, синхронизируемого уровнем 1

Рисунок 3.22 – Структура и условное обозначение R*S*-триггера, синхронизируемого передним фронтом

Также на рис. 3.23 и 3.24 для сравнения приведены структуры двух триггеров типа D (VD) - синхронизируемого уровнем 1 и передним фронтом.

Рисунок 3.23 – Структура и условное обозначение D (VD) -триггера, синхронизируемого уровнем 1

Рисунок 3.24 – Структура и условное обозначение D -триггера, синхронизируемого передним фронтом c асинхронной установкой

Асинхронная установка D-триггера (рис.3.24) осуществляется подачей комбинации R* = 0 и S* = 1 для сброса триггера в 0 и R* = 1 и S* = 0 для сброса триггера в 1. В случае подачи комбинации R* = 1 и S* = 1 триггер выполняет функции D-триггера, комбинацию R* = 0 и S* = 0 подавать нельзя.

Вообще существует большое количество D-триггеров.