Билет №9.

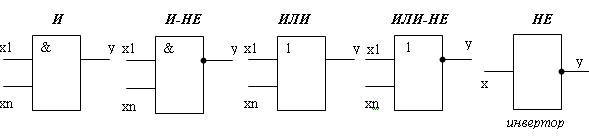

1.Логические элементы.

Логический элемент (логический вентиль) – это электронная схема, выполняющая некоторую простейшую логическую операцию.

Л огический

элемент может быть реализован в виде

отдельной интегральной схемы. Часто

интегральная схема содержит несколько

логических элементов.

огический

элемент может быть реализован в виде

отдельной интегральной схемы. Часто

интегральная схема содержит несколько

логических элементов.

Логические элементы используются в устройствах цифровой электроники (логических устройствах) для выполнения простого преобразования логических сигналов.

Выделяются следующие классы логических элементов (так называемые логики):

-

резисторно-транзисторная логика (РТЛ);

-

диодно-транзисторная логика (ДТЛ);

-

транзисторно-транзисторная логика (ТТЛ);

-

эмиттерно-связанная логика (ЭСЛ);

-

транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ);

-

логика на основе МОП-транзисторов с каналами типа р (р-МДП);

-

логика на основе МОП-транзисторов с каналами типа n (n-МДП);

-

логика на основе комплементарных ключей на МДП-транзисторах (КМДП, КМОП);

-

интегральная инжекционная логика И²Л;

-

логика на основе полупроводника из арсенида галлия GaAs.

2.Программируемые логические интегральные схемы.

Программи́руемая логи́ческая интегра́льная схе́ма (ПЛИС, англ. programmable logic device, PLD) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). По структурному признаку (по архитектуре) ПЛИС подразделяют на следующие классы:

-

Программируемые логические матрицы (ПЛМ или PLA, Programmable Logic Array) — ПЛИС, имеющие программируемые матрицы И и ИЛИ.

-

Программируемая матричная логика (ПМЛ или PAL, Programmable Array Logic) — ПЛИС, имеющие программируемую матрицу И и фиксированную матрицу ИЛИ.

В зарубежной литературе ПЛИС этих двух классов ПЛМ и ПМЛ объединяют аббревиатурой PLD (Programmable Logic Devices).

-

Базовые матричные кристаллы (БМК), которые также называют вентильными матрицами (ВМ или GA, Gate Array). ВМ представляют собой набор несоединенных логических элементов.

-

Программируемые вентильные матрицы (ПВМ или у FPGA, Field Programmable Gate Array). ПВМ — это ПЛИС, состоящая из логических блоков, содержащих логические элементы, и программируемых матриц соединений.

-

Программируемые коммутируемые матричные блоки ПКМБ. В зарубежной литературе их обозначают аббревиатурой CPLD (Complex Programmable Logic Devices). ПКМБ — это ПЛИС, содержащие несколько матричных логических блоков (каждый из которых имеет структуру ПМЛ), объединенных коммутирующей матрицей.

-

ПЛИС комбинированной архитектуры и типа «система на кристалле».

Следовательно, укрупненная структура ПЛИС выглядит следующим образом

![]()

Билет №10.

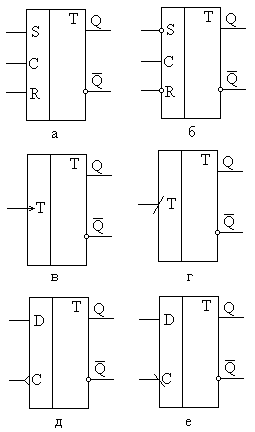

1.Триггеры

Триггер – это простейший элементарный конечный автомат, который обладает памятью и применяется для хранения одного бита информации (0 или 1).

Триггер, как конечный автомат характеризуется следующими свойствами:

1. возможное число внутренних состояний 2: веден (1) и сброшен (0), что соответствует одной внутренней переменной z. В триггерах z обозначается как z=Q;

2.

число выходных переменных y

одно. Значение переменой у совпадает с

одним из значений Q,

т.е.

![]() ,

поэтому триггер является конечным

автоматом Мура;

,

поэтому триггер является конечным

автоматом Мура;

3. число входных переменных х зависит от типа триггера;

4.

вход у = Q

называется прямым. Триггер имеет и

другой – инверсный выход

![]() .

.

Триггеры классифицируют по ряду признаков. По функциональным возможностям или организацией входных цепей и цепей памяти выделяют:

1) триггер с раздельной установкой 0 и 1 или с двумя установочными входами (RS-триггер);

2) триггер с приемом информации по одному входу (D-триггер), другое название - триггер задержки;

3) триггер со счетным входом или счетные триггеры (Т-триггер);

4) универсальный триггер с несколькими входами (JK - триггер).

По способу приема информации триггеры подразделяют на асинхронные (нетактируемые) и синхронные (тактируемые).

Асинхронные триггеры реагируют на информационные сигналы в момент их появления на входах триггера.

Синхронные триггеры реагируют на информационные сигналы при наличии разрешающего сигнала на специально предусматриваемом входе С. Синхронные триггеры подразделяются на триггеры со статическим управлением по С-входу и с динамическим управлением.

Триггеры со статическим управлением реагируют на информационные сигналы при подаче на вход С уровня 1 (прямой С-вход) или 0 (инверсный С-вход).

Триггеры с динамическим управлением реагируют на информационные сигналы в момент изменения сигнала на С-входе от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

По принципу построения триггеры со статическим управлением можно разделить на одноступенчатые и двухступенчатые.

Одноступенчатые триггеры имеют одну ступень запоминания информации. Запись информации в такие триггеры представляет собой непрерывный во времени процесс установления состояния триггера под воздействием информационных сигналов.

Двухступенчатые триггеры имеют две ступени запоминания информации, которые тактовым импульсом управляются таким образом, что в начале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе триггера.

Для всех типов триггеров характерны следующие параметры:

h – коэффициент разветвления, характеризует нагрузочную способность триггера. Он означает количество параллельно соединенных ИМС, следующих за триггером, на которые можно подать сигнал с выхода триггера.

m – коэффициент объединения, означающий количество входных сигналов подаваемых на вход триггера.

tи – наименьшая длительность входного сигнала (импульса), при котором еще происходит переключение триггера из состояния 1 в 0 (0 в 1).

tзд – время задержки между моментом подачи входного сигнала и моментом появления выходного сигнала.

tр - разрешающее время - это наименьший интервал между моментом подачи двух входных сигналов длительностью tи и вызывающих переключение триггера.

На всех рисунках (см. рис. 1.1) кружочек обозначает инверсию выходного, либо входного сигнала. Рисунок а) и б) RS-триггер со статическими входами синхронизирующихся потенциалом равным логической 1 (вход С). Рисунок в) и г) асинхронный Т-триггер с динамическим входом, который срабатывает от перехода потенциала соответствующего логическому 0 и логической 1. Переход от 0 к 1 указывается линией /. Рисунок д) и е) триггер задержки со статическим входом D, который синхронизируется фронтом сигнала синхронизации С.

/, - переход от 0 к 1.

\, - переход от 1 к 0.

а) и б) - RS-триггер со статическими входами;

в) и г) - асинхронный Т-триггер с динамическим входом;

д) и е) - триггер задержки со статическим входом D.