- •1. Циклические коды (цк)

- •1.1 Циклические корректирующие коды

- •1.2 Построение цк

- •1.3 Определение параметров цк(цск) по m,s,r

- •1.4 Определение параметров цк, обеспечивающих заданную вероятность передачи по каналу с шумом

- •1.5 Кодеры цск

- •1.5.1 Кодирование с помощью полинома h(X)

- •1.5.2 Кодирование с помощью полинома g(X)

- •1.6 Декодеры цск

- •1.6.1 Декодеры Меггита

- •1.6.1.1 Режим исправления и обнаружения ошибок

- •1.6.1.2 Режим обнаружения ошибок

- •1.7 Примеры

- •1.7.1 Пример 1

- •1.7.2 Пример 2

- •1.7.3 Пример 3

- •1.7.4 Пример 4

- •1.7.5 Пример 5

- •1.7.7 Пример 7

- •1.7.8 Пример 8

- •1.7.9 Пример 9

- •1.7.10 Пример 10

- •1.7.11 Пример 11

- •1.8 Справочные материалы

- •1.8.1 Теоремы бчх

- •1.8.2 Таблица неприводимых многочленов

1.7.7 Пример 7

Требуется построить кодер по полиномуh(x)имеет вид:

h(x)=1+x2+x3+x4.

Выберем произвольно m=4 информационных символов:

![]()

В нашем случае кодовый вектор, в соответствии с (12), имеет вид:

![]()

Информационными являются символы: a0,a1,a2,a3

Контрольными – a4,a5,a6.

По формуле (11`), найдем:

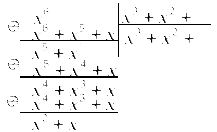

![]()

![]()

![]()

![]()

![]()

![]()

Таким образом, вид кодового вектора, посылаемого в линию связи, начиная с информационных разрядов, такой:

а6 а5 а4 а3 а2 а1 а0

0 1 1 0 0 0 1

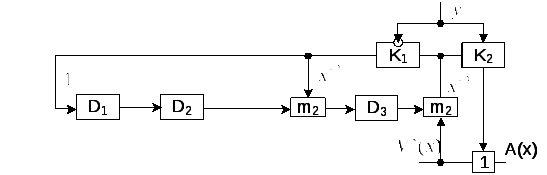

Для реализации данного способа кодирования требуется регистр, сдвига с логическими обратными связями, содержащий m=4 ячеек памяти. Вид обратной связи полностью определяется полиномомh(x) (смотри соотношение 11 и 11`). Нарис.1а приведен указанный кодирующий регистр (построен с помощью обобщенной структурной схемы кодера по полиномуh(x)см.рис.1).

рис.1а. Кодирующий регистр кода (7,4,3)

на основе ![]()

(m2 – сумматор по модулю 2)

Работа устройства. В исходном состоянии

в регистр записывают произвольно

выбранные m=4 информационных

разрядов![]() .

Далее на регистр от генератор тактовых

(сдвиговых) импульсов поступаетn=7

импульсов. С выхода 1-й ячейки памяти

(D0 ) регистра в линию

связи поступают кодовые элементы

систематического циклического кода,

начиная с информационных символов. При

этом на каждом такте в 4-ю ячейку (D3)

регистра записывается символ, значение

которого определяется на основании

выражения (11`):

.

Далее на регистр от генератор тактовых

(сдвиговых) импульсов поступаетn=7

импульсов. С выхода 1-й ячейки памяти

(D0 ) регистра в линию

связи поступают кодовые элементы

систематического циклического кода,

начиная с информационных символов. При

этом на каждом такте в 4-ю ячейку (D3)

регистра записывается символ, значение

которого определяется на основании

выражения (11`):

![]() (i=

(i=![]() –

номер такта).

–

номер такта).

Таблица переходов:

|

№ такта |

Разряд регистра |

Выход | ||||

|

D3 |

D2 |

D1 |

D0 | |||

|

0 |

0 |

0 |

0 |

1 |

- | |

|

1 |

1 |

0 |

0 |

0 |

1 |

m=4 |

|

2 |

1 |

1 |

0 |

0 |

0 | |

|

3 |

0 |

1 |

1 |

0 |

0 | |

|

4 |

1 |

0 |

1 |

1 |

0 | |

|

5 |

0 |

1 |

0 |

1 |

1 |

k=3 |

|

6 |

0 |

0 |

1 |

0 |

1 | |

|

7 |

0 |

0 |

0 |

1 |

0 | |

Временная диаграмма:

1.7.8 Пример 8

Задан порождающий полином:

![]()

Данному полиному соответствует код (7,4), т.е. m=4,k=3.

Пусть:

![]()

Тогда:

![]()

Найдем r(x):

Итак,

![]()

Тогда кодовый вектор:

![]() ,

,

где первые четыре символа – произвольно выбранные информационные символы, а последние три – соответствующие им проверочные символы (счет справа налево).

При реализации данного способа кодирования требуется регистр сдвига с логическими обратными связями, содержащий k=3 ячеек памяти. Необходимое число сумматоров поmod2 определяется, как количество плюсов в полиномеg(x)(У нас 2).

Вид обратной связи полностью определятся

полиномом g(x)

=1+x2+x3.

(Пояснение:D3соответствуетx2

в полиномеg(x),

значит в кодере должен присутствовать

сумматор, который ставиться переда

данной ячейкой памяти и осуществляет

суммирование поmod2

значения предыдущей памяти на предыдущем

такте и обратной связи на данном такте).

Структура кодера (кодопреобразователя),

приведена нарис.2а, в ней регистр

выполняет деление вектора![]() на

полиномg(x)(построен с помощью обобщенной структурной

схемы кодера по полиномуg(x).

см. рис.2).

на

полиномg(x)(построен с помощью обобщенной структурной

схемы кодера по полиномуg(x).

см. рис.2).

рис.2а. Кодирующий регистр кода (7,4) на

основе ![]()

с предварительным умножением ![]()

В таблице переходов приведена последовательность смены состояний регистра (см.рис.2а) с обратными связями (ОС) при подаче на его вход последовательности 0001, начиная с крайней правой единицы.

Таблица переходов:

|

Состояние ключей |

№ такта |

Вход |

Разряд регистра |

Выход | |||

|

D1 |

D2 |

D3 | |||||

|

|

0 |

0 |

0 |

0 |

0 |

- | |

|

1 |

1 |

1 |

0 |

1 |

1 |

m=4 | |

|

2 |

0 |

1 |

1 |

1 |

0 | ||

|

3 |

0 |

1 |

1 |

0 |

0 | ||

|

4 |

0 |

0 |

1 |

1 |

0 | ||

|

5 |

0 |

1 |

0 |

1 |

1 |

k=3 | |

|

6 |

0 |

0 |

1 |

0 |

1 | ||

|

7 |

0 |

0 |

0 |

1 |

0 | ||

Рассмотрим потактно работу схемы.

0 такт: все ячейки памяти находятся в нуле, ключ К1 открыт, К2 закрыт, на входе и на выходе сигналов нет.

1 такт: на вход поступает 1-ый информационный

символ 1, на m2 происходит

его суммирование со значением ячейкиD3 (которое было на

предыдущем такте):![]() результат

идет через открытый ключ К1 в

обратную связь. В регистре происходит

сдвиг. ЯчейкаD1 изменяет

своё состояние на 1(записывается значение

сигнала пришедшего по обратной связи).

ВD2 записывается 0

(значение ячейкиD1 на

предыдущем такте). В ячейку памятиD3

записывается сумма поmod2 сигнала обратной связи и значения

ячейкиD2 (на предыдущем

такте), получаем

результат

идет через открытый ключ К1 в

обратную связь. В регистре происходит

сдвиг. ЯчейкаD1 изменяет

своё состояние на 1(записывается значение

сигнала пришедшего по обратной связи).

ВD2 записывается 0

(значение ячейкиD1 на

предыдущем такте). В ячейку памятиD3

записывается сумма поmod2 сигнала обратной связи и значения

ячейкиD2 (на предыдущем

такте), получаем![]() .

На выход поступает сигнал со входа, т.е.

1.

.

На выход поступает сигнал со входа, т.е.

1.

2-4 такт: работа аналогична работе кодера на 1-ом такте.

5 такт: ключ К1 закрывается, а К2 открывается, т.ет обратная связь разрывается, а на выход поступает значение из регистра. ПолучаемD1 становится в 0 (т.к. обратная связь разорвана). ВD2 передвигается значение изD1 (которое было на предыдущем такте). ВD3 записывается предыдущее значениеD2 1. Как видим кодер, начиняя с 5(m+1) такта работает как сдвиговый регистр.

6-7 такт: работает в режиме сдвигового регистра со сдвигом вправо.

Временная диаграмма: