- •Лекция 1. Элементы ЭВМ

- •1.1. Логические элементы

- •Лекция 2. ЗАПОМИНАЮЩИЕ ЭЛЕМЕНТЫ

- •1.2. Комбинационные узлы

- •Лекция 4. НАКАПЛИВАЮЩИЕ УЗЛЫ

- •1.2.6. Счетчики

- •Лекция 5. УСТРОЙСТВА ЦВМ

- •Лекция 6. УСТРОЙСТВО УПРАВЛЕНИЯ

- •1.3.6. Датчик сигналов на сдвиговом регистре

- •Лекция 7. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

- •Лекция 8. ОРГАНИЗАЦИЯ КОМПЬЮТЕРНЫХ СИСЕТЕМ

- •2.1. Основные понятия

- •2.2. Что такое микропроцессор

- •Лекция 9. ОБМЕН ДАННЫМИ В МИКРОПРОЦЕССОРНОЙ СИСТЕМЕ

- •2.3. Шинная структура связей

- •Лекция 10. АРХИТЕКТУРА 16-РАЗРЯДНОГО МИКРОПРОЦЕССОРА

- •2.5. Архитектура микропроцессора Intel 8086

- •2.6. Архитектура микропроцессора Intel 80286

- •Лекция 11. АРХИТЕКТУРА НАБОРА КОМАНД

- •3.1. Классификация команд

- •3.2. Режимы адресации

- •3.3. Адресация операндов

- •3.4. Регистры процессора

- •3.5. Система команд процессора

- •3.5.2. Арифметические команды

- •3.5.3. Логические команды

- •3.5.4. Команды переходов

- •Лекция 12. СИСТЕМА КОМАНД МИКРОПРОЦЕССОРА INTEL 8086

Лекция 3. ÓÇËÛ ÝÂÌ

1.2. Комбинационные узлы

Узлы ЭВМ можно подразделить на два типа – комбинационные узлы и накапливающие.

Узел ЭВМ представляет собой совокупность нескольких логических схем и, в общем случае, элементов памяти, формирующих выходные сигналы, соответствующие нескольким логическим функциям от входных сигналов.

Характерной особенностью узлов комбинационного типа является то, что их выходные сигналы определяются только действующими в данный момент входными сигналами (не зависят от «истории» входных сигналов).

Характерной особенностью узлов накапливающего типа является то, что их выходные сигналы определяются не только действующими в данный момент входными сигналами, но и тем, какие входные сигналы поступали на узел ранее, т. е. зависят от «истории» входных сигналов. Свойство хранить историю обеспечивается у накапливающих узлов наличием памяти, представленной некоторой совокупностью запоминающих элементов.

Рассмотрим некоторые примеры комбинационных узлов.

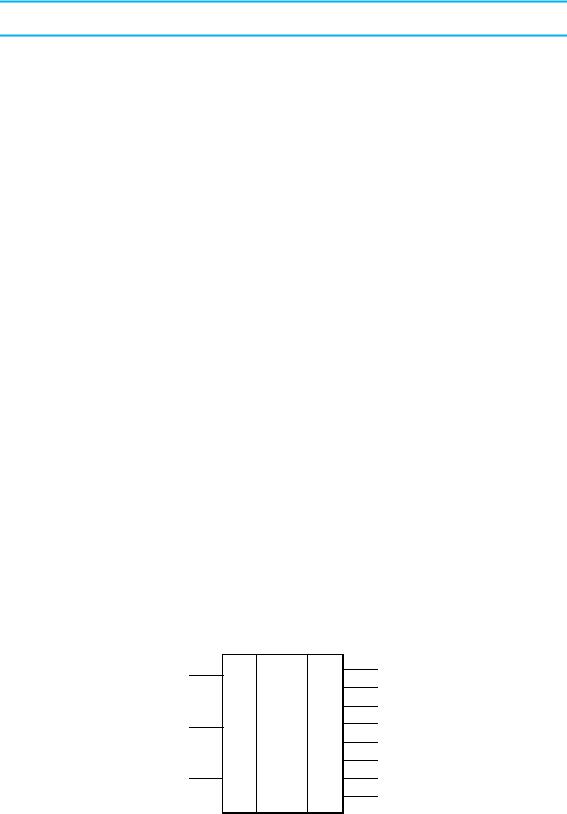

1.2.1. Дешифратор. Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах. Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000. Условно-графическое обозначение дешифратора на три входа приведено на рис. 1.20.

0 DC 0

1

2

13

4

5

26

7

Рис. 1.20. Условно-графическое обозначение трехвходового дешифратора

20

Номер разряда, в котором устанавливается «1» на выходе дешифратора, определяется кодом на его входах. Ниже приведена таблица истинности трехвходового дешифратора (табл. 1.5).

Таблица 1.5

|

|

Таблица истинности трехвходового дешифратора |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

|

2 |

1 |

0 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Реализация дешифратора в одноэлементном базисе «Штрих Шеффера» достаточно проста, так как таблица истинности для любого выхода имеет только одну единицу. На рис. 1.21 представлена схема формированиясигналанаодномизвыходовдешифратора(сигналf5 навыходе5).

x0 |

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

& |

|

|

|

|

& |

|

|

& |

|

|

|

|

|

|

|

|||

|

|

x |

|

|

f5 |

f5 |

|||||

|

|

|

|

|

|||||||

|

|

|

|

||||||||

|

|

|

|

1 |

|

|

|

|

|

|

|

x2 |

|

|

1 |

|

|

2 |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.21. Схема формирования сигнала на выходе 5 трехвходового дешифратора

Из представленной схемы видно, что фактически логику преобразования выполняет лишь элемент 2, в то время как элемент 1 служит для получения инверсии сигнала x1, а элемент 3 преобразует полученное на элементе 2 инверсное значение функции в прямое. Многие элементы хранения, например триггерные схемы, позволяют получать сигнал в парафазном коде, то есть имеют два выхода, на одном из которых сигнал имеет прямое, а на другом – инверсное значение. Это позволяет избавиться от элемента 1 в схеме. Если предположить, что значения выходных сигналов имеют инверсный вид по отношению к представленному в табл. 1.5, то отпадает необходимость в элементе 3. В большинстве реальных интегральных микросхем реализованы

21

именно дешифраторы с инверсными выходами. Обозначение такого дешифратора показано на рис. 1.22.

DC 0

01

2

13

4

25

6

7

Рис. 1.22. Условно-графическоеобозначение дешифраторас инверсными выходами

На выходах такого дешифратора образуется унитарный код, содержащий один и только один ноль. Например, если входные сигналы имеют значение 1102 = 610, то выходы дешифратора, представленного на рис. 1.3, будут находиться в состоянии 10111111, то есть выход 6 будет иметь значение, отличное от остальных выходов.

Дешифраторы широко применяются в различных устройствах компьютеров. Прежде всего, они используются для выбора ячейки запоминающего устройства, к которой производится обращение для записи или считывания информации. При этом часть разрядов адресного кода может дешифрироваться дешифраторами, выполненными в виде отдельных интегральных схем, а другая часть разрядов (обычно младшая) дешифрируется с помощью дешифраторов, встроенных непосредственно в БИС запоминающего устройства. Кроме того, дешифраторы находят применение в устройстве управления для определения выполняемой операции, построения распределителей импульсов и в других блоках.

1.2.2. Шифратор. Шифратор – схема, имеющая 2n входов и n выходов, функции которой во многом противоположны функции дешифратора (рис. 1.23). Эта комбинационная схема в соответствии с унитарным кодом на своих входах формирует позиционный код на выходе (табл. 1.6).

0CD

10

21

3

Рис. 1.23. Условно-графическое обозначение шифратора на четыре входа

22

|

|

|

|

|

|

|

Таблица 1.6 |

|

Таблица истинности шифратора на четыре входа |

||||||

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выходы |

||

3 |

2 |

|

1 |

0 |

1 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

0 |

0 |

|

1 |

– |

0 |

|

1 |

0 |

1 |

|

– |

– |

1 |

|

0 |

1 |

– |

|

– |

– |

1 |

|

1 |

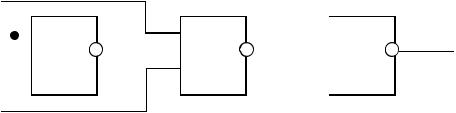

1.2.3. Сумматор по модулю 2. Сумматор по модулю 2 вырабатывает на своем входе сигнал логической единицы, если количество его входов с сигналом логической единицы нечетное. На рис. 1.24, а приведена схема сумматора по модулю 2 на два входа, а на рис. 1.24, б – его условное обозначение. На рис. 1.24, в приведен сумматор по модулю 2 с восьмью входами, построенный по принципу каскадирования из двухвходовых сумматоров по модулю 2.

Сигнал на выходе схемы (см. рис. 1.3, в) у определяется логическим выражением

y (y5y6 y5y6) (y1y2 y1y2)(y3y4 y3y4) (y1y2 y1y2)(y3y4 y3y4).

&

&

&

а

x1 x2

x3 x4

x5 x6

x7 x8

1 |

x1 |

|

y = x1x2 + x2 x1

x2

m2

m2

m2

m2

m2

m2

m2

в

Рис. 1.24. Сумматор по модулю 2:

m2 y

б

y

а– схема на логических элементах; б – условно-графическое изображение;

в– схема восьмивходового сумматора по модулю 2

23

1.2.4. Мультиплексор. Мультиплексор реализует функцию подключения одного из нескольких входов к единственному выходу. На рис. 1.25, а приведена схема мультиплексора, а на рис. 1.25, б – его условное обозначение.

|

|

|

|

|

|

|

Вход 1 |

& |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

y1 |

|

|

|

|

|

|

& |

|

|

|

|

1 |

DC |

1 |

|

Вход 2 |

|

|

|

||||

|

|

|

|

|

|

|

|||||

y2 |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|||||

|

|

2 |

|

|

|

|

Выход |

||||

2 |

|

|

|

|

|

|

|||||

|

|

|

|

|

& |

|

|

||||

|

|

|

|

3 |

|

Вход 3 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

|

|

с |

|

4 |

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Вход 4 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Вход |

|

|

|

|

|

|

|

|

y |

|

|

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Выход 1

б

Рис. 1.25. Мультиплексор:

а – схема мультиплексора; б – условное обозначение

Приведенная схема осуществляет коммутацию четырех одноразрядных входов на один одноразрядный выход. Входы управления у1, у2 определяют номер одного из четырех входов, который нужно логически соединить с выходом.

При необходимости построения мультиплексора, обеспечивающего коммутацию четырех п-разрядных входов на один п-разрядный выход, необходимо использовать параллельное подключение к выходу одного дешифратора n логических элементов И-ИЛИ.

1.2.5. Демультиплексор. Демультиплексор выполняет функцию логического подключения одного входного канала к одному из нескольких

24

выходных каналов, т. е. его функция является обратной по сравнению с функцией, реализуемой мультиплексором. На рис. 1.26, а приведена схема демультиплексора, реализованного на дешифраторе.

y1

y2

yn

Вход

Вход, 1p

1

23

.

n

c

1

2

3

.

n c

|

|

|

|

|

|

DC |

|

|

1 |

|

|

|

|

|

|

|

Выход 1 |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

Выход 2 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

m |

|

|

|

|

|

Выход m |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

DC |

|

|

|

|

1 |

|

|

Выход 1, np |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

Выход 2, np |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

DC |

. |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

n |

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3p |

|

|

|

|

||||||||||

|

|

DC |

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

m |

|

|

Выход m, np |

||||||||

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

. |

|

|

|

|

2p |

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

m |

|

|

|

|

|

|

Выход m, 2p |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

1p |

|

|

|

|

|

m |

|

|

|

|

|

|

|

|

Выход m, 1p |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б

Рис. 1.26. Схема демультиплексора:

а – реализация на основе дешифратора; б – демультиплексор на n разрядов

На входы y1…, yn подается код номера входа, к которому нужно логически подсоединить вход демультиплексора, которым является вход синхронизации дешифратора. Демультиплексор, приведенный на

25