- •Лекция 1. Элементы ЭВМ

- •1.1. Логические элементы

- •Лекция 2. ЗАПОМИНАЮЩИЕ ЭЛЕМЕНТЫ

- •1.2. Комбинационные узлы

- •Лекция 4. НАКАПЛИВАЮЩИЕ УЗЛЫ

- •1.2.6. Счетчики

- •Лекция 5. УСТРОЙСТВА ЦВМ

- •Лекция 6. УСТРОЙСТВО УПРАВЛЕНИЯ

- •1.3.6. Датчик сигналов на сдвиговом регистре

- •Лекция 7. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

- •Лекция 8. ОРГАНИЗАЦИЯ КОМПЬЮТЕРНЫХ СИСЕТЕМ

- •2.1. Основные понятия

- •2.2. Что такое микропроцессор

- •Лекция 9. ОБМЕН ДАННЫМИ В МИКРОПРОЦЕССОРНОЙ СИСТЕМЕ

- •2.3. Шинная структура связей

- •Лекция 10. АРХИТЕКТУРА 16-РАЗРЯДНОГО МИКРОПРОЦЕССОРА

- •2.5. Архитектура микропроцессора Intel 8086

- •2.6. Архитектура микропроцессора Intel 80286

- •Лекция 11. АРХИТЕКТУРА НАБОРА КОМАНД

- •3.1. Классификация команд

- •3.2. Режимы адресации

- •3.3. Адресация операндов

- •3.4. Регистры процессора

- •3.5. Система команд процессора

- •3.5.2. Арифметические команды

- •3.5.3. Логические команды

- •3.5.4. Команды переходов

- •Лекция 12. СИСТЕМА КОМАНД МИКРОПРОЦЕССОРА INTEL 8086

УРОВЕНЬ 3 АРХИТЕКТУРЫ НАБОРА

КОМАНД

Лекция 11. АРХИТЕКТУРА НАБОРА КОМАНД

3.1. Классификация команд

Проектирование системы команд оказывает влияние на структуру ЭВМ. Оптимальную систему команд иногда определяют как совокупность команд, которая удовлетворяет требованиям проблемноориентированных применений таким образом, что избыточность аппаратных и аппаратно-программных средств на реализацию редко используемых команд оказывается минимальной. В различных программах ЭВМ частота появления команд различна; например, по данным фирмы DEC в программах для ЭВМ семейства PDP-11 наиболее часто встречается команда передачи MOV(B), на ее долю приходится приблизительно 32% всех команд в типичных программах. Систему команд следует выбирать таким образом, чтобы затраты на редко используемые команды были минимальными.

При наличии статистических данных можно разработать (выбрать) ЭВМ с эффективной системой команд. Одним из подходов к достижению данной цели является разработка команд длиной в одно слово и кодирование их таким образом, чтобы разряды таких коротких команд использовать оптимально, что позволит сократить время реализации программы и ее длину.

Другим подходом к оптимизации системы команд является использование микроинструкций. В этом случае отдельные биты или группы бит команды используются для кодирования нескольких элементарных операций, которые выполняются в одном командном цикле. Эти элементарные операции не требуют обращения к памяти, а последовательность их реализации определяется аппаратной логикой.

Сокращение времени выполнения программ и емкости памяти достигается за счет увеличения сложности логики управления.

Важной характеристикой команды является ее формат, определяющий структурные элементы команды, каждый из которых интерпрети-

80

руется определенным образом при ее выполнении. Среди таких элементов (полей) команды выделяют следующие: код операции, определяющий выполняемое действие; адрес ячейки памяти, регистра процессора, внешнего устройства; режим адресации; операнд при использовании непосредственной адресации; код анализируемых признаков для команд условного перехода.

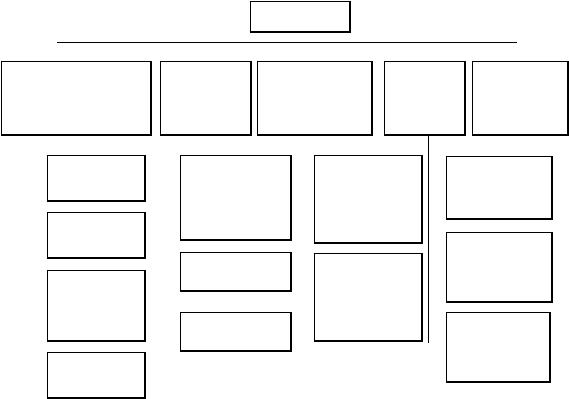

Классификация команд по основным признакам представлена на рис. 3.1. Важнейшим структурным элементом формата любой команды является код, определяющий операции (КОП), действие, которое должно быть выполнено. Большое число КОП в процессоре очень важно, так как аппаратная реализация команд экономит память и время. Но при выборе ЭВМ необходимо концентрировать внимание на полноте операций с конкретными типами данных, а не только на числе команд, на доступных режимах адресации. Число бит, отводимое под КОП, является функцией полного набора реализуемых команд.

|

|

|

|

|

|

|

Команды |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Пофункциональному |

По числу |

По способу |

По длине |

По способу |

|||||||||||||||

кодирования |

|||||||||||||||||||

|

|

числу |

адресов |

команды |

адресации |

||||||||||||||

|

|

|

команд |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Передача |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Безадресные |

|

|

С фиксиро- |

|

|

|

|

Длиной в |

|

||||||

|

|

|

данных |

|

|

|

|

|

одно слово |

|

|||||||||

|

|

|

|

|

(нуль |

|

|

|

ванным |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

(байт) |

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

Обработка |

|

|

адресные) |

|

|

полем КОП |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Длиной в |

|

|||

|

|

|

данных |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

Одноадресные |

|

|

С расширя- |

|

|

|

|

два слова |

|

|||||

|

|

|

Передача |

|

|

|

|

|

|

|

(байта) |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

ющимся |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

управления |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

Двухадресные |

|

|

полем КОП |

|

|

|

|

Длиной в |

||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

три слова |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Дополни- |

|

|

|

|

|

|

|

|

|

|

|

|

(байта) |

|||

тельные

Рис. 3.1. Классификация команд

При использовании фиксированного числа бит под КОП для кодирования всех m команд необходимо в поле КОП выделить двоичные

81

разряды, чтобы 2n = m. Однако, учитывая ограниченную длину слова мини- и микроЭВМ, различное функциональное назначение команд, источники и приемники результатов операций, а также то, что не все команды содержат адресную часть для обращения к памяти и периферийным устройствам, в малых ЭВМ для кодирования команд широко используется принцип кодирования с переменным числом бит под поле КОП для различных групп команд.

В некоторых командах необходим только один операнд и они называются однооперандными (или одноадресными) командами в отличие от двухоперандных (или двухадресных), в которых требуются два операнда. При наличии двух операндов командой обычно изменяется только один из них. Так как информация берется только из одной ячейки, эту ячейку называют источником; ячейку, содержимое которой изменяется, называют приемником.

По форматам команд можно судить о возможностях ЭВМ.

3.2. Режимы адресации

Для взаимодействия с различными модулями в ЭВМ должны быть средства идентификации ячеек внешней памяти, ячеек внутренней памяти, регистров МП и регистров устройств ввода/вывода. Поэтому каждой из запоминающих ячеек присваивается адрес, т. е. однозначная комбинация бит. Количество бит определяет число идентифицируемых ячеек. Обычно ЭВМ имеет различные адресные пространства памяти и регистров МП, а иногда – отдельные адресные пространства регистров устройств ввода/вывода и внутренней памяти. Кроме того, память хранит как данные, так и команды. Поэтому для ЭВМ разработано множество способов обращения к памяти, называемых режимами адресации.

Режим адресации памяти – это процедура или схема преобразования адресной информации об операнде в его исполнительный адрес.

Все способы адресации памяти можно разделить на:

1)прямой, когда исполнительный адрес берется непосредственно из команды или вычисляется с использованием значения, указанного

вкоманде, и содержимого какого-либо регистра (прямая адресация, регистровая, базовая, индексная и т. д.);

2)косвенный, который предполагает, что в команде содержится значение косвенного адреса, т. е. адреса ячейки памяти, в которой находится окончательный исполнительный адрес (косвенная адресация).

82

3.3. Адресация операндов

Большая часть команд процессора работает с кодами данных (операндами). Одни команды требуют входных операндов (одного или двух), другие выдают выходные операнды (чаще один операнд). Входные операнды называются еще операндами-источниками, а выходные называются операндами-приемниками. Все эти коды операндов (входные и выходные) должны где-то располагаться. Они могут находиться во внутренних регистрах процессора (наиболее удобный и быстрый вариант). Они могут располагаться в системной памяти (самый распространенный вариант). Наконец, они могут находиться в устройствах ввода/вывода (наиболее редкий случай). Определение места положения операндов производится кодом команды. Причем существуют разные методы, с помощью которых код команды может определить, откуда брать входной операнд и куда помещать выходной операнд. Эти методы называются методами адресации. Эффективность выбранных методов адресации во многом определяет эффективность работы всего процессора в целом.

3.3.1. Методы адресации. Количество методов адресации в раз-

личных процессорах может быть от 4 до 16. Рассмотрим несколько типичных методов адресации операндов, используемых сейчас в большинстве микропроцессоров.

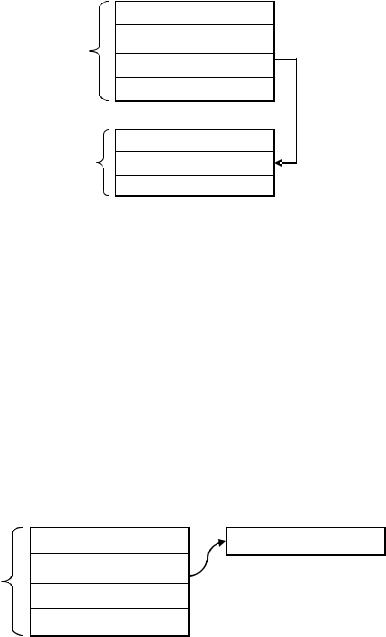

Непосредственная адресация (рис. 3.2) предполагает, что операнд

(входной) находится в памяти непосредственно за кодом команды. Операнд обычно представляет собой константу, которую надо куда-то переслать, к чему-то прибавить и т. д. Например, команда может состоять в том, чтобы прибавить число 6 к содержимому какого-то внутреннего регистра процессора. Это число 6 будет располагатьсяв памяти, внутри программы в адресе, следующем за кодом данной команды сложения.

|

Память |

|

|

|

|

Программа |

Команда |

|

Операнд |

Рис. 3.2. Непосредственная адресация

83

Прямая (она же абсолютная) адресация (рис. 3.3) предполагает,

что операнд (входной или выходной) находится в памяти по адресу, код которого находится внутри программы сразу же за кодом команды. Например, команда может состоять в том, чтобы очистить (сделать нулевым) содержимое ячейки памяти с адресом 1000000. Код этого адреса 1000000 будет располагаться в памяти, внутри программы в следующем адресе за кодом данной команды очистки.

Память

Программа

Команда

Операнд

Данные Операнд

Рис. 3.3. Прямая адресация

Регистровая адресация (рис. 3.4) предполагает, что операнд

(входной или выходной) находится во внутреннем регистре процессора. Например, команда может состоять в том, чтобы переслать число из нулевого регистра в первый. Номера обоих регистров (0 и 1) будут определяться кодом команды пересылки.

Косвенно-регистровая (она же косвенная) адресация предполагает, что во внутреннем регистре процессора находится не сам операнд, а его адрес в памяти (рис. 2.5). Например, команда может состоять в том, чтобы очистить ячейку памяти с адресом, находящимся в нулевом регистре. Номер этого регистра (0) будет определяться кодом команды очистки.

Память Регистр

Операнд

Программа Команда

Рис. 3.4. Регистровая адресация

84

Память Регистр

Операнд

Программа Команда

Данные Операнд

Рис. 3.5. Косвенная адресация

Реже встречаются еще два метода адресации. Автоинкрементная адресация очень близка к косвенной адреса-

ции, но отличается от нее тем, что после выполнения команды содержимое используемого регистра увеличивается на единицу или на два. Этот метод адресации очень удобен, например, при последовательной обработке кодов из массива данных, находящегося в памяти. После обработки какого-то кода адрес в регистре будет указывать уже на следующий код из массива. При использовании косвенной адресации в данном случае пришлось бы увеличивать содержимое этого регистра отдельной командой.

Автодекрементная адресация работает похоже на автоинкре-

ментную, но только содержимое выбранного регистра уменьшается на единицу или на два перед выполнением команды. Эта адресация также удобна при обработке массивов данных. Совместное использование автоинкрементной и автодекрементной адресаций позволяет организовать память стекового типа.

Из других распространенных методов адресации можно упомянуть об индексных методах, которые предполагают для вычисления адреса операнда прибавление к содержимому регистра заданной константы (индекса). Код этой константы располагается в памяти непосредственно за кодом команды.

Отметим, что выбор того или иного метода адресации в значительной степени определяет время выполнения команды. Самая быстрая адресация – это регистровая, так как она не требует дополнительных циклов обмена по магистрали. Если же адресация требует обращения к памяти, то время выполнения команды будет увеличиваться за счет длительности необходимых циклов обращения к памяти. Понятно, что чем больше внутренних регистров у процессора, тем

85

чаще и свободнее можно применять регистровую адресацию, и тем быстрее будет работать система в целом.

3.3.2. Сегментирование памяти. Говоря об адресации, нельзя обойти вопрос о сегментировании памяти, применяемой в некоторых процессорах, например в процессорах IBM PC-совместимых персональных компьютеров.

В процессоре Intel 8086 сегментирование памяти организовано следующим образом.

Вся память системы представляется не в виде непрерывного пространства, а в виде нескольких кусков – сегментов заданного размера (по 64 Кбайта), положение которых в пространстве памяти можно изменять программным путем.

Для хранения кодов адресов памяти используются не отдельные регистры, а пары регистров:

сегментный регистр определяет адрес начала сегмента (то есть положение сегмента в памяти);

регистр указателя (регистр смещения) определяет положение рабочего адреса внутри сегмента.

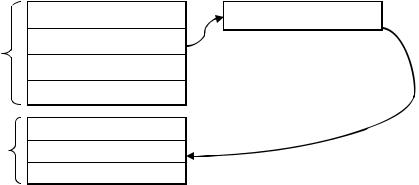

При этом физический 20-разрядный адрес памяти, выставляемый на внешнюю шину адреса, образуется так, как показано на рис. 3.6, то есть путем сложения смещения и адреса сегмента со сдвигом на 4 бита. Положение этого адреса в памяти показано на рис. 3.7.

Сегмент может начинаться только на 16-байтной границе памяти (так как адрес начала сегмента, по сути, имеет четыре младших нулевых разряда, как видно из рис. 3.6), то есть с адреса, кратного 16.

Эти допустимые границы сегментов называются границами параграфов.

Отметим, что введение сегментирования, прежде всего, связано

стем, что внутренние регистры процессора 16-разрядные, а физический адрес памяти 20-разрядный (16-разрядный адрес позволяет ис-

пользовать память только в 64 Кбайт, что явно недостаточно). В появившемся в то же время процессоре MC68000 фирмы Motorola внутренние регистры 32-разрядные, поэтому там проблемы сегментирования памяти не возникает.

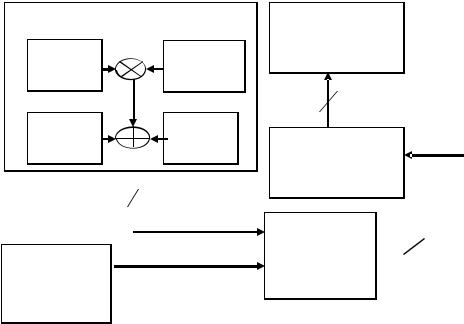

Применяются и более сложные методы сегментирования памяти. Например, в процессоре Intel 80286 в так называемом защищенном режиме адрес памяти вычисляется в соответствии с рис. 3.8.

В сегментном регистре в данном случае хранится не базовый (начальный) адрес сегментов, а коды селекторов, определяющие адреса

86

в памяти, по которым хранятся дескрипторы (то есть описатели) сегментов. Область памяти с дескрипторами называется таблицей дескрипторов. Каждый дескриптор сегмента содержит базовый адрес сегмента, размер сегмента (от 1 до 64 Кбайт) и его атрибуты. Базовый адрес сегмента имеет разрядность 24 бит, что обеспечивает адресацию 16 Мбайт физической памяти.

Исполнительный адрес |

|

16 бит |

|||||||

(смещение) |

|

||||||||

|

|

|

|

|

|

|

4 бита |

||

Адрес сегмента |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

16 бит |

|

|

|||||||

|

|

||||||||

|

|||||||||

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Физический адрес |

|

|

|

|

|

|

|

|

|

|

20 бит |

||||||||

памяти |

|

||||||||

|

|

|

|

|

|

|

|

||

Рис. 3.6. Формирование физического адреса памяти из адреса сегмента и смещения

Адреса Память

00000

.

.

12000 .

Смещение |

|

Адрес сегмента |

|

||

|

|

|

(ЗАВЕ) |

|

|

15АВЕ |

|

Размер сегмента |

|

(10000 байт = 64 Кбайт) |

|

|

|

|

|

|

Физический адрес |

21FFF |

|

|

|

|

. |

|

|

22000 |

|

|

|

|

|

. |

|

|

|

. |

|

|

|

|

|

|

Рис. 3.7. Физический адрес в сегменте |

||

|

|

(все коды – шестнадцатеричные) |

|

87

Процессор

Сегментный регистр

Селектор

150

Смещение

15 0

Сумматор

физического

адреса

Базовый адрес сегмента

23 |

0 |

Память

Операнд

Операнд Сегмент

Дескриптор Таблица сегмента дескрипторов

сегмента

Рис. 3.8. Адресация памяти в защищенном режиме процессора Intel 80286

Таким образом, на сумматор, вычисляющий физический адрес памяти, подается не содержимое сегментного регистра, как в предыдущем случае, а базовый адрес сегмента из таблицы дескрипторов.

Еще более сложный метод адресации памяти с сегментировани-

ем использован в процессоре Intel 80386 и в более поздних моделях процессоров фирмы Intel. Этот метод иллюстрируется рис. 3.9.

Адрес памяти (физический адрес) вычисляется в три этапа. Сначала вычисляется так называемый эффективный адрес (32-разрядный) путем суммирования трех компонентов: базы, индекса и смещения (Base, Index, Displacement), причем возможно умножение индекса на масштаб (Scale). Эти компоненты имеют следующий смысл:

1)смещение – это 8-, 16или 32-разрядное число, включенное

вкоманду;

2)база – это содержимое базового регистра процессора. Обычно оно используется для указания на начало некоторого массива;

88

3)индекс – это содержимое индексного регистра процессора. Обычно оно используется для выбора одного из элементов массива;

4)масштаб – это множитель (он может быть равен 1, 2, 4 или 8), указанный в коде команды, на который перед суммированием с другими компонентами умножается индекс. Он используется для указания размера элемента массива.

|

Вычисление эффективного |

|

|

|

|

|||||

|

|

адреса |

Память |

|

|

|

||||

|

INDEX |

|

|

SCALE |

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

(1,2,4,8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Физический |

|||

|

|

|

|

|

|

|

32 |

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

адрес |

||

|

|

|

|

|

|

|

|

|

||

|

BASE |

|

|

DISP |

|

|

Блок |

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

страничной |

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||||

32 |

Эффективный |

переадресации |

|

|||||||

|

|

Линейный |

|

|||||||

|

|

|

|

адрес |

|

|

|

|||

|

|

|

|

|

|

адрес |

|

|||

|

|

|

|

|

|

|

Блок |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

||

Сегментный |

|

|

|

|

сегментации |

|

||||

|

Индекс |

|

|

|

||||||

|

|

|

|

|

||||||

|

регистр |

|

|

|

|

|

||||

|

дескриптора |

|

|

|

|

|||||

|

|

|

|

|

|

|

||||

Рис. 3.9. Формирование физического адреса памяти процессора 80386 в защищенном режиме

Затем специальный блок сегментации вычисляет 32-разрядный линейный адрес, который представляет собой сумму базового адреса сегмента из сегментного регистра с эффективным адресом. Наконец, физический 32-битный адрес памяти образуется путем преобразования линейного адреса блоком страничной переадресации, который осуществляет перевод линейного адреса в физический страницами по

4Кбайта.

Влюбом случае сегментирование позволяет выделить в памяти один или несколько сегментов для данных и один или несколько сегментов для программ. Переход от одного сегмента к другому сводится всего лишь к изменению содержимого сегментного регистра. Иногда это бывает очень удобно. Но для программиста работать с сегментированной памятью обычно сложнее, чем с непрерывной, несегментированной памятью, так как приходится следить за границами сегментов, за их описанием, переключением и т. д.

89