- •Лекция 1. Элементы ЭВМ

- •1.1. Логические элементы

- •Лекция 2. ЗАПОМИНАЮЩИЕ ЭЛЕМЕНТЫ

- •1.2. Комбинационные узлы

- •Лекция 4. НАКАПЛИВАЮЩИЕ УЗЛЫ

- •1.2.6. Счетчики

- •Лекция 5. УСТРОЙСТВА ЦВМ

- •Лекция 6. УСТРОЙСТВО УПРАВЛЕНИЯ

- •1.3.6. Датчик сигналов на сдвиговом регистре

- •Лекция 7. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

- •Лекция 8. ОРГАНИЗАЦИЯ КОМПЬЮТЕРНЫХ СИСЕТЕМ

- •2.1. Основные понятия

- •2.2. Что такое микропроцессор

- •Лекция 9. ОБМЕН ДАННЫМИ В МИКРОПРОЦЕССОРНОЙ СИСТЕМЕ

- •2.3. Шинная структура связей

- •Лекция 10. АРХИТЕКТУРА 16-РАЗРЯДНОГО МИКРОПРОЦЕССОРА

- •2.5. Архитектура микропроцессора Intel 8086

- •2.6. Архитектура микропроцессора Intel 80286

- •Лекция 11. АРХИТЕКТУРА НАБОРА КОМАНД

- •3.1. Классификация команд

- •3.2. Режимы адресации

- •3.3. Адресация операндов

- •3.4. Регистры процессора

- •3.5. Система команд процессора

- •3.5.2. Арифметические команды

- •3.5.3. Логические команды

- •3.5.4. Команды переходов

- •Лекция 12. СИСТЕМА КОМАНД МИКРОПРОЦЕССОРА INTEL 8086

Учреждение образования «БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНОЛОГИЧЕСКИЙ УНИВЕРСИТЕТ»

А. С. Кобайло

АРИФМЕТИКО-ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН И АРХИТЕКТУРА КОМПЬЮТЕРОВ

Конспект лекций по одноименной дисциплине для студентов IT-специальностей

Минск 2015

1

УДК 004.2.031(075.8) ББК 32.97.я73

К55

Рассмотрено и рекомендовано к изданию редакционно-издательским советомБелорусскогогосударственноготехнологическогоуниверситета.

Рецензенты: кандидат технических наук, доцент,

доцент кафедры программного обеспечения информационных технологий УО «Белорусский государственный университет информатики и радиоэлектроники»

П. Ю. Бранцевич;

заведующий кафедрой информационных технологий

иэкологического менеджмента ГУО «Институт бизнеса

именеджмента технологий» БГУ

Б. В. Лесун

Кобайло, А. С.

К55 Арифметико-логические основы цифровых вычислительных машин и архитектура компьютеров : конспект лекций по одноименной дисциплине для студентов IT-специальностей / А. С. Кобайло. – Минск : БГТУ, 2015. – 112 с.

Конспект лекций содержит основные сведения в области схемотехники ЦВМ, архитектурной организации микропроцессоров, основ программирования на языках низкого уровня. Рассмотрены вопросы организации обмена данными в микропроцессорных системах, а также структуры конкретных микропроцессоров.

Издание предназначено для студентов, изучающих дисциплину «Ариф- метико-логические основы цифровых вычислительных машин и архитектура компьютеров». Пособие также может быть полезно аспирантам, изучающим избранные аспекты вышеуказанных проблем.

УДК 004.2.031(075.8) ББК 32.97.я73

©УО «Белорусский государственный технологический университет», 2015

©Кобайло А. С., 2015

2

СОДЕРЖАНИЕ

1. ЦИФРОВОЙ ЛОГИЧЕСКИЙ УРОВЕНЬ АРХИТЕКТУРЫ ЦВМ |

.... 5 |

Лекция 1. ЭЛЕМЕНТЫ ЭВМ........................................................... |

5 |

1.1. Логические элементы.......................................................... |

5 |

Лекция 2. ЗАПОМИНАЮЩИЕ ЭЛЕМЕНТЫ............................... |

9 |

Лекция 3. УЗЛЫ ЭВМ.................................................................... |

20 |

1.2. Комбинационные узлы...................................................... |

20 |

1.2.1. Дешифратор........................................................... |

20 |

1.2.2. Шифратор ............................................................. |

22 |

1.2.3. Сумматор по модулю 2 ........................................ |

23 |

1.2.4. Мультиплексор ..................................................... |

24 |

1.2.5. Демультиплексор.................................................. |

24 |

Лекция 4. НАКАПЛИВАЮЩИЕ УЗЛЫ...................................... |

26 |

1.2.6. Счетчики ................................................................ |

26 |

1.2.7. Регистры................................................................. |

29 |

1.2.8. Регистр сдвига...................................................... |

30 |

Лекция 5. УСТРОЙСТВА ЦВМ.................................................... |

33 |

1.3. Арифметико-логическое устройство............................... |

33 |

1.3.1. Обобщенная структура АЛУ .............................. |

33 |

1.3.2. Синтез АЛУ........................................................... |

36 |

Лекция 6. УСТРОЙСТВО УПРАВЛЕНИЯ.................................. |

41 |

1.3.3. Устройство управления........................................ |

41 |

1.3.4. Схемное устройство управления......................... |

44 |

1.3.5. Датчик сигналов на основе счетчика |

45 |

с дешифратором ............................................................. |

|

1.3.6. Датчик сигналов на сдвиговом регистре ........... |

46 |

1.3.7. Структурная схема микропрограммного |

|

устройства управления................................................... |

48 |

Лекция 7. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА......................... |

49 |

1.3.8. Классификация запоминающих устройств. ....... |

51 |

1.3.9. Построение ЗУ с заданной организацией .......... |

54 |

2. АРХИТЕКТУРА МИКРОПРОЦЕССОРНЫХ СИСТЕМ.................. |

59 |

Лекция 8. ОРГАНИЗАЦИЯ КОМПЬЮТЕРНЫХ СИСЕТЕМ ..... |

59 |

2.1. Основные понятия ............................................................. |

59 |

2.2. Что такое микропроцессор................................................ |

62 |

Лекция 9.ОБМЕН ДАННЫМИ |

|

В МИКРОПРОЦЕССОРНОЙ СИСТЕМЕ...................................... |

65 |

2.3. Шинная структура связей ................................................. |

65 |

3

Лекция 10. АРХИТЕКТУРА |

|

16-РАЗРЯДНОГО МИКРОПРОЦЕССОРА.................................... |

71 |

2.4. Структура микропроцессора Intel 8080 ........................... |

71 |

2.5. Архитектура микропроцессора 8086 ............................... |

73 |

2.6. Архитектура микропроцессора Intel 80286..................... |

76 |

3. УРОВЕНЬ АРХИТЕКТУРЫ НАБОРА КОМАНД............................ |

80 |

Лекция 11. АРХИТЕКТУРА НАБОРА КОМАНД......................... |

80 |

3.1. Классификация команд ..................................................... |

80 |

3.2. Режимы адресации............................................................. |

82 |

3.3. Адресация операндов ........................................................ |

83 |

3.3.1. Методы адресации................................................ |

83 |

3.3.2. Сегментирование памяти..................................... |

86 |

3.3.3. Адресация байтов и слов...................................... |

90 |

3.4. Регистры процессора......................................................... |

90 |

3.5. Система команд процессора............................................. |

94 |

3.5.1. Команды пересылки данных ............................... |

95 |

3.5.2. Арифметические команды.................................... |

96 |

3.5.3. Логические команды............................................ |

97 |

3.5.4. Команды переходов ............................................. |

99 |

Лекция 12 СИСТЕМА КОМАНД |

|

МИКРОПРОЦЕССОРА INTEL 8086 ............................................ |

103 |

3.6. Способы адресации |

|

и форматы команд микропроцессора I 8086 ........................ |

103 |

4

ЦИФРОВОЙ 1 ЛОГИЧЕСКИЙ УРОВЕНЬ

АРХИТЕКТУРЫ ЦВМ

Лекция 1. ЭЛЕМЕНТЫ ЭВМ

1.1. Логические элементы

Большинство современных ЦВМ состоят из двух и более архитектурных уровней (до шести).

Элементы ЭВМ, являющиеся представителями низшего иерархического уровня архитектуры компьютера – цифрового логического уровня (схемотехнического), реализованные на радиотехнических деталях, представляют собой мельчайшие компоненты, на основе которых строятся более крупные составляющие вычислительной машины.

Можно выделить три основные разновидности элементов – логические элементы, запоминающие, специальные.

Логические элементы, так же как и элементы алгебры логики, реализуют логические функции, но эти функции, оставаясь сравнительно простыми, все же сложней, чем базовые функции в алгебре логики. В одном логическом элементе может быть реализовано несколько простых функций. Кроме того, логические элементы характеризуются дополнительными параметрами, такими, как количество входов, нагрузочная способность (количество входов других элементов, к которым можно подключать выход данного элемента).

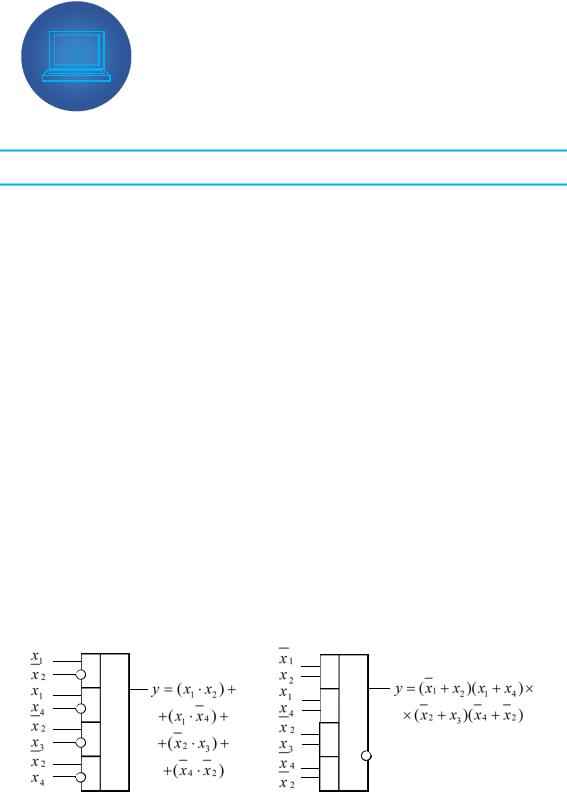

На рис. 1.1 приведены примеры некоторых логических элементов.

& |

1 |

|

1 |

|

|

|

|

|

& |

|

|

|

|||

|

|

|

|

|

|

|

|

& |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

& |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

б |

|

Рис. 1.1. Примеры логических элементов: а – И-ИЛИ; б – ИЛИ-И-НЕ

5

На выходах элементов указаны логические выражения для выходных сигналов в соответствии с приведенными входными сигналами. На рис. 1.1, б приведен логический элемент с инверсными входами (в логическом выражении сигнал по такому входу используется в обратном значении).

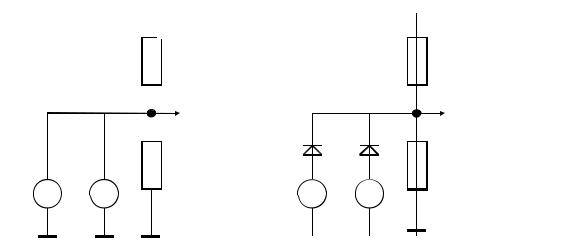

Примеры реализации простейших логических элементов с помощью диодно-резисторной схемы приведены на рис. 1.2.

Uвх1.––xx11 |

|

|

|

|

+ U |

UUвхвх1.1.––x1x1 |

|

|

+ U |

|

|||||||

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Uвх2.––xx22 |

R11 |

|

|

|

|

|

UUвхвх22. – x2 |

RR1 1 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвых |

|

|

|

|

|

|

|

|

Uвых |

|

|

|

|

||||||

D1 |

2 |

R |

|

|

|

|

(у=хх11хх22)) |

|

|

|

|

|

|

|

|

(у=хх11++хх2)2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

DD2 |

2R2 |

|

|

|

|

|

D1 |

D2 |

|

R2 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвх1 |

UвхU2вх1. |

U вх2 |

|

|

|

Uвх1 |

Uвх2 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

б |

||||||

Рис. 1.2. Электрические схемы реализации логических элементов:

a – реализация логических элементов «И»; б – реализация элемента «ИЛИ»

На рис. 1.2, а приведена реализация логических элементов И. Реализация элемента ИЛИ приведена на рис. 1.2, б. Схемы логических элементов построены с условием, что логическая «1» соответствует высокому уровню («+»), а логический ноль – низкому уровню напряжения, близкому «земле». Это соответствие используется и в других реализациях. На рис. 1.2, а соотношение сопротивления резисторов R1 и R2 при заданном напряжении «+U» выбирается таким образом, что без учета шунтирующего действия диодных цепочек напряжение на выходе имеет значение высокого уровня (уровня, соответствующего логической «1»). Источники входных сигналов Uвх1 и Uвх2 имеют малое внутреннее сопротивление. Поэтому, если один или оба источника подают низкий уровень (логический «0»), то из-за шунтирующего воздействия диодных цепочек на резисторе R2 на выходе будет иметь место низкий уровень напряжения, соответствующий логическому нулю. Высокий уровень на выходе (логическая «1») будет иметь место только тогда, когда на оба входа подаются единицы, так

6

как соответствующие им высокие уровни напряжения закрывают оба диода. Таким образом, единица на выходе будет иметь место только тогда, когда и x1, и x2 имеют единичные значения. Это означает, что рассматриваемая схема реализует логику И.

Для схемы на рис. 1.2, б соотношение сопротивления резисторов R1 и R2 при заданном напряжении «+U» выбирается таким образом, что без учета воздействия диодных цепочек напряжение на выходе имеет значение низкого уровня (уровня, соответствующего логическому «0»). Если хотя бы один или оба источника входных сигналов подают высокий уровень (логическая «1»), то этот высокий уровень проходит через открытый диод и появляется на выходе. Низкий уровень, т. е. логический «0», будет иметь место только тогда, когда оба входных сигнала имеют низкий уровень. Это означает, что рассматриваемая схема реализует логику ИЛИ.

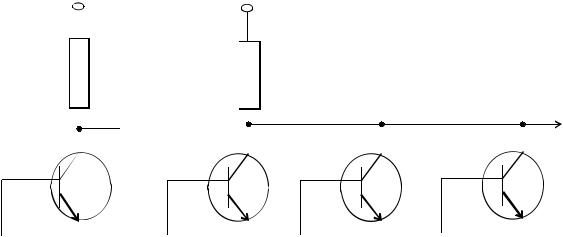

На рис. 1.3 приведены примеры реализации логических функций НЕ (рис. 1.3, а) и ИЛИ-НЕ (рис. 1.3, б) на транзисторах. Транзисторы обозначены символом «Т».

|

|

|

+U |

|

|

+U |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

R |

|

|

|

R |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

y = x1 |

|

|

|

|

|

|

|

y = x1 +x2 +x3 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

Т1 |

|

Т2 |

|

Т3 |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

x1 |

|

|

|

х2 |

|

|

|

х3 |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

а |

|

|

|

|

|

|

б |

|

||||||

Рис. 1.3. Примеры реализации логических элементов: а – элемент НЕ; б – элемент ИЛИ-НЕ

На рис. 1.3, а транзистор открыт, следовательно, на его коллекторе напряжение, близкое к нулевому уровню, будет иметься тогда, когда на его базе высокий уровень логической единицы, и, наоборот, транзистор закрыт, а следовательно на его коллекторе высокий уровень тогда, когда входной сигнал соответствует низкому уровню нуля. Выходом схемы является коллектор транзистора, поэтому выходной сигнал реализует функцию НЕ.

7

На рис. 1.3, б на выходе схемы «y» будет низкий уровень (логический нуль) тогда, когда открыт хотя бы один транзистор T1, T2, T3, т. е. тогда, когда хотя бы одна из входных переменных x1, x2, x3 имеет значение логической единицы. Это означает, что выходной сигнал «y» зависит от входных сигналов по логике ИЛИ-НЕ.

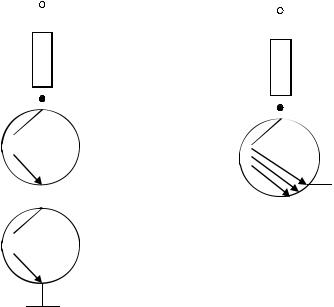

На рис. 1.4 приведены примеры реализации логических функций И-НЕ и функции И на транзисторах.

На рис. 1.4, а на выходе схемы «y» будет низкий уровень (логический нуль) только тогда, когда открыты оба транзистора T1, T2 , т. е. тогда, когда обе входные переменные x1, x2 имеют значение логической единицы. Это означает, что выходной сигнал «y» зависит от входных сигналов по логике И-НЕ.

На рис. 1.4, б приведена схема, использующая многоэмиттерный транзистор T3. Транзистор такого типа пропускает ток только тогда, когда имеет место высокий уровень на его базе и низкий уровень хотя бы на одном из его эмиттеров. В приведенной схеме на базу T3 подается постоянный высокий уровень (логическая константа, равная «1»). В этом случае на выходе схемы «y» будет низкий уровень (логический нуль) тогда, когда есть условия протекания тока хотя бы по одному из его эмиттеров, т. е. хотя бы одна из входных переменных x1, x2, x3 имеет значение логического нуля.

|

|

|

+U |

|

|

|

|

|

|

|

|

+U |

||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

R |

|

|

|

|

|

|

|

|

|

R |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y = |

|

|

|

|

|

|

|

|

|

|

|

T1 |

|

|

|

x1x2 |

|

|

T3 |

|

|

|

|

y = x1x2 x3 |

||||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+(1) |

|

|

|

|

|

|

x3 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

б |

Рис. 1.4. Примеры реализации логических функций:

а – на транзисторной логике; б – на транзисторно-транзисторной логике

8