Лекция 35

Типовые схемы включения ЦАП и АЦП

Цель лекции:

изучить типовые схемы включения ЦАП и АЦП, способы реализации на их основе некоторых часто встречающихся функций.

План лекции:

1.Схема ЦАП с суммированием токов.

2.ЦАП со взвешивающей резистивной матрицей.

3.ЦАП с матрицей R-2R.

4.АЦП последовательного счёта.

5.АЦП параллельного действия.

6.Применение ЦАП.

7.Применение АЦП.

Схема ЦАП с суммированием токов

При построении ЦАП чаще всего реализуется метод суммирования нескольких различных эталонов, в качестве таких эталонов можно использовать источники напряжения или тока.

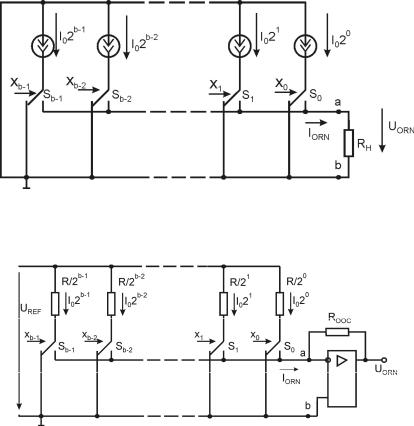

Принцип построения ЦАП, реализующих метод суммирования токов,

показан на рис. 5, а.

ЦАП в общем случае содержит b (по числу разрядов входного позиционного кода X) источников тока и b управляемых разрядами этого кода переключателей S. Если в i-м разряде входного кода X присутствует сигнал лог. 1 (xi = 1), соответствующий переключатель Si подключает эталонный источник тока I02i к сопротивлению нагрузки Rн (узел «а» схемы).

В противном случае (xi = 1) переключатель Si закорачивает соответствующий источник и ток I02i не протекает через нагрузку.

а)

б)

Рис. 1. Структурная схема ЦАП с суммированием токов (а) и её реализация с использованием матрицы взвешенных резисторов (б)

В результате ток резистора Rн равен

|

b 1 |

(1) |

|

IORN I |

0 2i Xi |

||

|

i 0

и пропорционален значению входного кода. При условии Rн = const выходное напряжение схемы UORN = IORN Rн также пропорционально входному коду.

На практике для получения напряжения, пропорционального входному коду, к выводам «a», «b» подключают операционный усилитель (ОУ) (рис. 1,

б) в режиме преобразователя тока в напряжение. Легко увидеть, что для рассматриваемой схемы

UORN = IORN RООС, |

(2) |

то есть выходное напряжение ОУ прямо пропорционально выходному току ЦАП и сопротивлению ROOC и не зависит от сопротивления выходной нагрузки ОУ.

ЦАП со взвешивающей резистивной матрицей

В простейшем случае для получения эталонных источников тока I02i

можно к источнику напряжения UREF подключить ряд резисторов,

сопротивления которых пропорциональны весовым коэффициентам входного кода (см. рис. 1, б). Такие резисторы называют взвешенными. Так как из логики работы ОУ вытекает равенство Ua = Uь = 0, то токи резисторов схемы будут обратно пропорциональны их сопротивлениям

Ii = UREF 2i/R=Ii 2i ,

где I0 =UREF /R ,

и для выходного напряжения устройства справедливо выражение (1).

Недостатком такого решения является широкий диапазон изменения сопротивлений взвешенных резисторов, используемых для формирования разрядных токов. К тому же для обеспечения точности преобразования абсолютные значения сопротивлений этих резисторов должны выдерживаться с прецизионной точностью.

ЦАП с матрицей R-2R

Для преодоления недостатков ЦАП с взвешивающей резистивной матрицей часто используют резистивные R-2R матрицы, выполненные только на резисторах двух номиналов R и 2R.

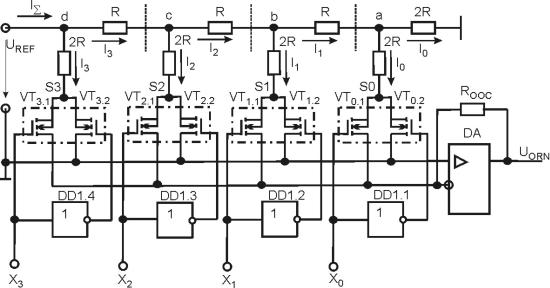

Рассмотрим (рис. 2) схему 4-разрядного ЦАП с матрицей R-2R. Схема включает R-2R матрицу, четыре переключателя S3, S2, S1, S0 на МДП-

транзисторы VT3,1, …, VT0,1 и VT3,2, … , VT0,2, четыре инвертора DD1.4, ... ,

DD1.1 и ОУ DA1 с цепью отрицательной обратной связи. На входы инвертора подаются сигналы разрядов входного кода X3, …, X0, а на вход матрицы R-2R – напряжение от эталонного источника UREF.

Рис. 2. Структурная схема 4-разрядного ЦАП с матрицей R-2R

Рассмотрим работу матрицы R-2R. Для удобства предположим, что на вход ЦАП подан нулевой код (0000).

Тогда выходными сигналами инверторов DD1.4,..., DD1.1 включены транзисторы VT3,2, …, VT0,2 переключателей S3,..., S0, и нижние выводы всех резисторов 2R матрицы подключены к общей шине.

Работа матрицы R-2R основана на том, что выходное сопротивление любой отсекаемой от нее правой части схемы (на рис. 2 возможные места отсечения показаны пунктирными линиями), содержащей целое число R-2R

звеньев определяется параллельным соединением двух цепей, сопротивления каждой из которых равно 2R. Поэтому выходное сопротивление матрицы относительно узла «a» равно R. Аналогично сопротивление матрицы относительно узла «b» также равно R.

Полное выходное сопротивление матрицы, измеренное относительно узла «d», равно R, и ток, отбираемый матрицей от источника UREF,

I UREF / R.

Так как сопротивления ветвей матрицы, подключенных к точке «d»

равны, то

|

I3 I / 2 |

UREF / 2R. |

|

Ток |

I3, втекающий в узел «с», |

также разделится пополам, |

то есть |

I2 I3 / 2 |

UREF / 4R и т.д. |

|

|

Через переключатели S3, ... , S0 протекают токи, значения которых |

|||

пропорциональны весовым коэффициентам двоичного кода. |

|

||

Если на входы некоторых инверторов поданы сигналы лог. 1, то в |

|||

соответствующих переключателях Si |

включены транзисторы VTi1 |

и токи, |

|

пропорциональные весовым коэффициентам данных разрядов, попадают на инвертирующий вход ОУ. В этом случае, согласно принципу суперпозиции,

для входного тока ОУ справедливо выражение (1), а для выходного напряжения усилителя – выражение (2).

В общем случае для b-разрядного кода можно записать

|

|

|

|

|

|

|

|

|

|

b 1 |

|

|

|

|

||

UORN IORN ROOC ROOC I0 |

2i Xi |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

i 0 |

|

|

|

|

|

|

ROOC |

I |

|

b |

b 1 |

|

Xi |

UREF |

R |

|

|

1 |

b 1 |

|

Xi. |

(3) |

|

|

|

2 |

i |

OOC |

|

b |

2 |

i |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

2 |

|

i 0 |

|

|

|

R |

|

|

2 |

|

i 0 |

|

|

|

|

Если на вход ЦАП подать максимально большое число (все разряды входного кода равны лог. 1), то из выражения (3) легко получить значение максимального напряжения на выходе ЦАП

U |

ORNMAX |

U |

REF |

ROOC |

(1 |

1 |

). |

(4) |

R |

2b |

|

||||||

|

|

|

|

|

На практике для получения простой функции преобразования обычно делают величины RООС и R равными. В результате выражения (3) и (4)

приобретают вид выражений (5) и (6) соответственно

|

|

UORN UREF 1b |

2i Xi, |

|

|

(5) |

||||||||

|

|

|

|

|

|

|

|

b 1 |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

i 0 |

|

|

|

|

|

||

U |

ORNMAX |

U |

REF |

(1 |

1 |

) U |

REF |

|

UREF |

U |

REF |

. |

(6) |

|

2b |

2b |

|

||||||||||||

|

|

|

|

|

|

|

|

|

||||||

Полученные выражения показывают, что в ЦАП рассматриваемого типа максимальное выходное напряжение всегда на 1ЕМР меньше опорного напряжения UREF.

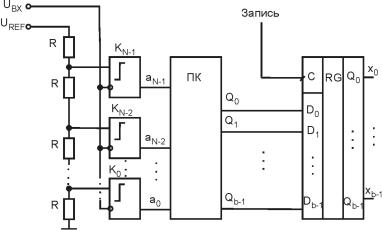

АЦП последовательного счёта

Принцип работы АЦП последовательного счета со счетчиком рассмотрим с использованием структурной схемы, рис. 3. Устройство содержит генератор тактовых импульсов (ГТИ), выход которого подключен к верхнему входу элемента 2И DD1. Выход элемента 2И соединен со счетным входом счетчика DD2, выходы которого соединены со входами ЦАП. Выход ЦАП подключен к инвертирующему входу безгистерезисного компаратора

DA, к неинвертирующему входу которого подключается источник входного напряжения, преобразуемого в код. Выход компаратора соединен с нижним входом элемента 2И DD1.

Рис. 3 Структурная схема АЦП последовательного счёта

В исходном состоянии на вход установки в нуль счетчика DD2 подан активный логический сигнал. Счетчик сброшен. Его выходной код равен нулю. Равно нулю и выходное напряжение ЦАП. Поэтому, если Uвх > 0, то на выходе компаратора присутствует сигнал лог. 1 и тактовые импульсы с выхода ГТИ через элемент 2И DD1 поступают на вход С счетчика. Однако так как сигнал на входе R = 0, выходной код счетчика Х 0.

Преобразование начинается в момент снятия со входа R активного логического сигнала (импульс «Пуск»). В этом случае с приходом каждого тактового импульса с выхода ГТИ счетчик выполняет операцию инкремента.

Его выходной код начинает увеличиваться. Соответственно увеличивается и выходное напряжение ЦАП (рис. 4).

Рис. 4 Напряжения на входах компаратора DA

Этот процесс продолжается до тех пор, пока выходное напряжение ЦАП не превысит величину Uвх. В этот момент компаратор DA сформирует на выходе сигнал лог. 0. В результате на выходе элемента 2И DD1 также будет сформирован сигнал лог. 0 и увеличение выходного кода счетчика прекратится.

При этом значение выходного кода счетчика будет прямо пропор-

ционально входному напряжению UВХ и обратно пропорционально абсолютной разрешающей способности используемого ЦАП

NВЫХ UВХ / .

Так как выходное напряжение ЦАП имеет форму ступенчатой функции,

то напряжение NВЫХ , найденное по формуле, должно быть округлено до ближайшего целого числа, соответствующего номеру первого уровня UN* ,

превышающего значение UВХ (рис. 4). Для повторения цикла преобразования необходимо импульсом «Пуск» счетчик установить в нуль.

Время преобразования в рассмотренном АЦП прямо пропорционально его выходному коду и периоду следования импульсов ГТИ (ТГТИ)

tc NВЫХTГТИ TГТИUВХ / .

Рассмотренный режим работы называется циклическим, так как каждый раз импульс «Пуск» сбрасывает счетчик DD2, и поэтому счет

(преобразование) всегда начинается с нуля.

АЦП параллельного действия

Данный тип АЦП реализует метод непосредственного считывания и является самым быстродействующим (рис. 5).

Устройство содержит 2b – 1 компараторов К, на объединенные инверти-

рующие входы которых подается входной преобразуемый сигнал. На неинвертирующие входы компараторов подаются напряжения, численно равные уровням квантования Un*. В результате с выходов компаратора снимается параллельный N-разрядный единичный код. Число единиц в нем равно числу уровней квантования по величине меньших значений UВХ.

Полученный единичный код подается на вход преобразователя кода

(ПК), в котором он преобразуется в двоичный с числом разрядов b = lоg2N. С

выхода ПК двоичный код подается на вход регистра, с выхода которого он и считывается. Перезапись кода ПК в регистр происходит по сигналу «Запись».

Этот сигнал подается в схему после того, как все переходные процессы,

связанные со срабатыванием компараторов и получением двоичного кода,

завершены.

Рис. 5. Структурная схема ЦАП параллельного действия

Для получения напряжений, равных уровням квантования в схеме,

использован делитель напряжения на N одинаковых резисторах,

подключенный к выходу источника эталонного напряжения UREF.

Формирование в данном АЦП выходного кода одновременно по всем разрядам предполагает получение максимально возможного быстродействия.

Повышение точности работы АЦП данного типа связано со значительными аппаратными затратами. Так, для построения 8-разрядного АЦП необходимо 255 компараторов.

На практике компромисс между быстродействием и сложностью схемы разрешается в так называемых параллельно-последовательных схемах АЦП.

Применение ЦАП

В общем случае микросхему ЦАП можно представить в виде блока

(рис. 6), имеющего несколько цифровых входов и один аналоговый вход, а

также аналоговый выход.

Рис. 6. Микросхема ЦАП

На цифровые входы ЦАП подается n-разрядный код N, на аналоговый вход — опорное напряжение Uоп (другое распространенное обозначение —

UREF). Выходным сигналом является напряжение Uвых (другое обозначение —

UO) или ток Iвых (другое обозначение — IO). При этом выходной ток или выходное напряжение пропорциональны входному коду и опорному напряжению.

Кроме информационных сигналов, микросхемы ЦАП требуют также подключения одного или двух источников питания и общего провода.

Обычно цифровые входы ЦАП обеспечивают совместимость со стандартными выходами микросхем ТТЛ.

Чаще всего в случае, если ЦАП имеет токовый выход, его выходной ток преобразуется в выходное напряжение с помощью внешнего