Лекция30

Сумматорыи цифровые компараторы

Цель лекции:

изучение комбинационных микросхем: сумматоров и компараторов кодов; их алгоритмов работы; типовых схем включения.

План лекции:

1.Полусумматор.

2.Полный сумматор.

3.Последовательный многоразрядный сумматор.

4.Цифровые компараторы.

Все многообразие математических операций (вычитание, умножение,

деление, вычисление тригонометрических функций, извлечение корня и т.д.)

можно свести к единственной операции сложения прямых и обратных сдвинутых влево или вправо на то или иное число разрядов кодов чисел.

Поэтому одним из узлов арифметических ЭВМ является сумматор. Сумматоры многоразрядных чисел, которыми оперирует машина, составляются из одноразрядных сумматоров, представляющих логические схемы,

выполняющие операцию сложениядвухили трех одноразрядных чисел.

Сумматор "по модулю два представляет собой устройство с двумя входами (X и Y), на выходе у которого сигнал 1 появляется только в том случае, когда на входах действуют противоположные (неравнозначные)

сигналы, т.е. 0 и 1. Это устройство называют также схемой неравнозначности или схемой "исключающее ИЛИ".

Название "по модулю два" этот сумматор получил потому, что соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел X и Y.

Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел X и Y, значение результата суммирования S и

значение переноса в старший разряд P (таблица 1). Работа устройства,

реализующего таблицу истинности, описывается следующими уравнениями:

S X Y X Y; P X Y .

Очевидно, что по отношению к столбцу S реализуется логическая функция «исключающее ИЛИ», т.е.

|

S=X Y. |

|

(6.5) |

|

|

|

|

|

|

Таблица 1 |

|

Таблица истинности полусумматора |

|

|

|

||

|

|

|

|

|

|

|

X |

Y |

P |

S |

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

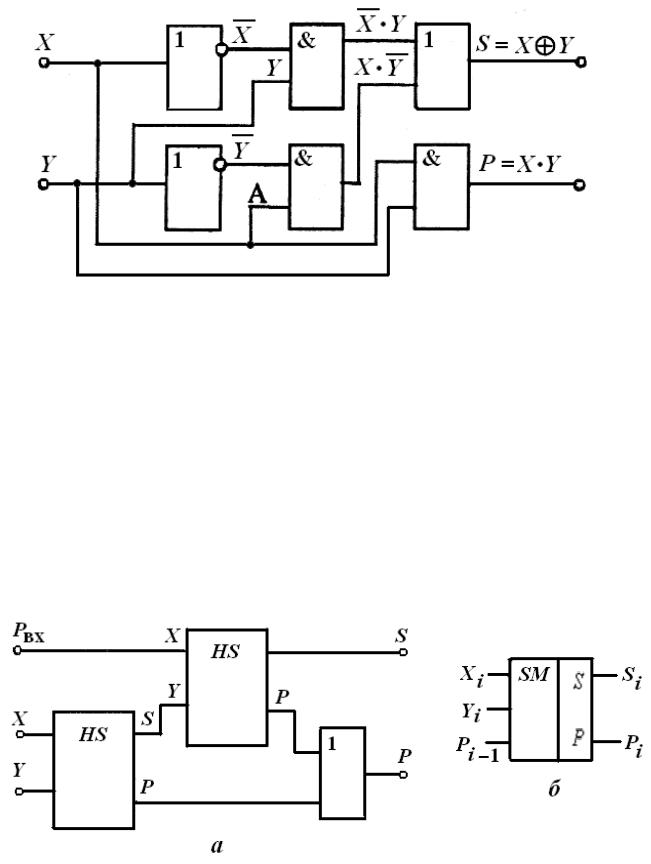

Устройство, реализующее таблицу 1, называют полусумматором, и

оно имеет логическую структуру, изображенную на рис. 1. Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде. На схемах полусумматор обозначается HS.

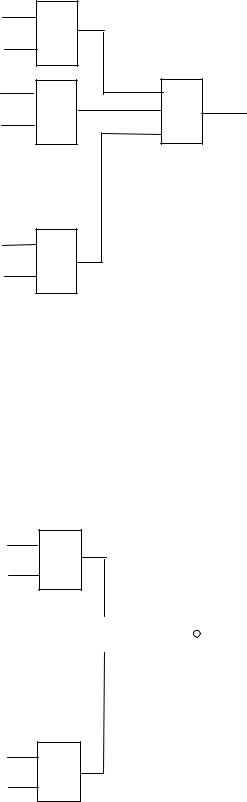

Рис. 1. Схема полусумматора

При суммировании двух многоразрядных чисел для каждого разряда

(кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса.

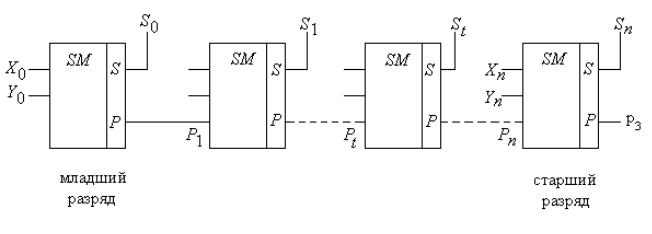

Полный сумматор – это устройство для сложения трех одноразрядных двоичных чисел Xi, Yi и Pi, где Pi - сигнал переноса из предыдущего младшего разряда. Подобно полусумматору, полный одноразрядный сумматор должен также иметь два выхода Si (сумма) и Рi (перенос) (рис. 2).

Рис. 2. Схема полного сумматора (а) его условное графическое обозначение (б)

Работу сумматора описывает таблица истинности. В табл. 2 связаны все возможные варианты значений i-го разряда, возникающие при сложении двух двоичныхчиселXиY, ирезультатсложения (функции Si и Рi).

|

|

|

|

|

|

Таблица2 |

Таблица истинностисумматора |

|

|

|

|

||

|

|

|

|

|

|

|

|

Входы |

|

|

Выходы |

||

|

|

|

|

|

|

|

Xi |

Yi |

|

Pi-1 |

Pi |

|

Si |

|

|

|

|

|

|

|

0 |

0 |

|

0 |

0 |

|

0 |

0 |

0 |

|

1 |

0 |

|

1 |

0 |

1 |

|

0 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

|

0 |

1 |

0 |

|

0 |

0 |

|

1 |

1 |

0 |

|

1 |

1 |

|

0 |

1 |

1 |

|

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

|

1 |

|

|

|

|

|

|

|

Многоразрядные сумматоры. Используя полный сумматор, можно построить суммирующее устройство для сложения многоразрядных двоичных чисел Xi и Yi. Различают многоразрядные последовательные и параллельные

сумматоры.

Последовательный многоразрядный сумматор состоит (рис. 3) из одноразрядного полного сумматора, на входы Xi и Yi которого из сдвигающих регистров, хранящих числа X и Y, подаются по тактам разряд за разрядом коды этих чисел, начиная с младшего разряда.

Цепь задержки обеспечивает хранение импульса переноса Рi+1 на время одного такта, т.е. до перехода пары слагаемых следующего разряда, с которым он будет просуммирован. Задержку обеспечиваетD-триггер.

Рис. 3. Структурная cхема последовательного многоразрядного сумматора

Если время элемента задержки равно одному такту (например,

использован D-триггер), то сигнал переноса от предыдущего разряда,

сформированный в предыдущем такте, поступит на нижний вход сумматора только в следующем такте, когда на входы Xi и Yi поданы значения

следующего разряда чисел Xi и Yi. В результате на выходе S разряд за разрядом в виде последовательного кода будет формироваться двоичное число,

равное сумме чисел Xi и Yi, которое воспринимается сдвигающим регистром суммы.

Достоинством последовательного сумматора является простота схемы,

недостатком – низкое быстродействие, так как для сложения кодов n-разрядных чисел требуется (учитывая возможность переполнения) n+1 такт работы устройства.

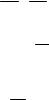

Параллельный многоразрядный сумматор имеет меньшее время выполнения операции. В этом устройстве операция сложения производится одновременно (за один такт) во всех n-разрядах чисел Xi и Yi, поступающих в параллельном коде. Для этого параллельный сумматор (рис. 4) составляют из n

одноразрядных сумматоров, соединяя выход переноса i-го разряда со входом переноса соседнего (i+1)-го разряда (в младшем разряде можно использовать полусумматор).

После того как сформируется результат сложения на выходах одноразрядных сумматоров, он обычно запоминается в параллельном регистре.

Длительность формирования результата определяется временем установления выходных сигналов (как суммы, так и переноса) в каждом из одноразрядных сумматоров после установления сигналов на его входах.

Рис. 4. Схема параллельного многоразрядного сумматора

При этом если на входы Xi и Yi всех разрядов сигналы поступают в момент начала такта (например, с выходов регистров памяти, хранивших параллельные коды чисел Xi и Yi), то на вход Pi сигнал переноса поступит с некоторой задержкой, определяемой длительностью переходных процессов в сумматоре предыдущегоразряда.

Цифровые компараторы

Цифровые компараторы (от английского compare — сравнивать)

выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А=В или неравенства

А<В, А>В. Результат сравнения отображается в виде логического сигнала на одноименных выходах.

Функционирование компаратора описывается следующими уравнениями:

1при А В

Y1( A,B)

0 при А В

1при А В

Y2( A,B)

0 при А В

1при А В

Y3( A,B)

0 при А В

По полученным выражениям составим таблицу истинности (таблица 3).

Таблица 3.

Таблица истинности компаратора

а |

b |

y1(a=b) |

y2(a>b) |

y3(a<b) |

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

Из таблицы 3 получаем функции y1, y2, y3: y1i Ai Bi Ai Bi - функция равнозначности.

y2i Аi Bi

y3i Ai Bi

Функция y1 носит название функции равнозначности

(эквивалентности).

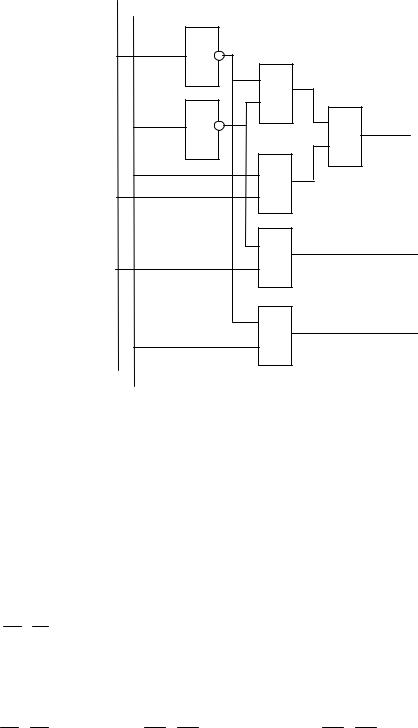

Построим компаратор на логических элементах. Схема одноразрядного компаратора приведена на рис. 5.

a

b

1 |

|

|

|

& |

|

1 |

1 |

y1 |

|

||

|

& |

|

& y2

& y3

Рис.5 – Логическая схема одноразрядного компаратора

Компаратор состоит из двух элементов НЕ, четырех элементов И, и

одного элемента ИЛИ-НЕ.

Чаще всего задача состоит в определении равнозначности двух многоразрядных чисел A и В. Такое сравнение реализуется переключательными функциями. Для каждого разряда i можно записать:

Z1i Ai Bi Ai Bi.

Это равенство должно выполняться для всех n разрядов, т.е. выходной сигнал

Z ( A1 B1 A1 B1 ) ( A2 B2 A2 B2 ) ... ( An Bn An Bn ).

Схемы компаратора приведены на рис. 6 и 7.

А1 В1

А2 В2

Аn Вn

=

=

.

.

.

=

А1~В1

& Z

Аn~Вn

Рис. 6. Многоразрядный компаратор на элементах «равнозначность»

При сравнении многоразрядных чисел алгоритм такой — сначала сравнивают значения старших разрядов; если они различны, то эти разряды и определяют результат сравнения. Если же они равны, то необходимо сравнивать следующие за ним более младшие разряды и т.д.

А1 =1

В1

А2 |

|

|

=1 |

|

|

1 |

|

|

|

|

|

|

|||

В2 |

|

|

|

|

|

||

|

|

|

|

|

|||

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

.

.

.

Аn =1

Вn

Рис. 7. Многоразрядный компаратор на элементах

«неравнозначность» (исключающее ИЛИ)

Условное графическое обозначение цифрового компаратора приведено на рис. 8.

A1 |

|

A |

= = |

|

|

|

|||||

|

|

|

|||||||||

A2 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

||||||

A3 |

|

|

|

|

A< |

|

|

||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B1 |

|

|

|

|

|

A= |

|

|

|||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|||||

|

B |

|

|

A> |

|

|

|||||

B2 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

B3 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A< |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A= |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A> |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 8.Условное обозначение цифрового компаратора.

Цифровые компараторы применяются для выявления нужного числа

(слова) в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, а также в адресных селекторах.