mpusu_avr_p2

.pdf

20.12.2017

Микропроцессорные устройства систем управления

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» Факультет электротехники и автоматики

Кафедра систем автоматического управления

к.т.н., доцент

Голик Станислав Евсеевич

E-mail: segolik@gmail.com

Тел: +7 (921) 321-0875

2

Голик С.Е.

1

20.12.2017

Архитектура микроконтроллеров AVR

1995 – студенты Norwegian University of Science and Technology в г. Тронхейм Alf-Egil Bogen и

Vegard Wollen предложили фирме Atmel новую RISC архитектуру микроконтроллеров AVR

1996 – фирма Atmel открыла исследовательский центр Atmel в г. Тронхейм, где был разработан первый микроконтроллер семейства AT90S1200

1997 – начат серийный выпуск микроконтроллеров семейства AVR

3

Голик С.Е.

Архитектура микроконтроллеров AVR

Общие сведения

Основные характеристики микроконтроллера ATmega16A

•AVR RISC-архитектура высокой производительности;

•система команд из 130 инструкций, большая часть которых выполняется за один машинный цикл;

•единый 16-разрядный формат команд;

•производительность 16 MIPS на частоте 16 Мгц;

•16 Кбайт Flash ПЗУ программ;

•512 байт EEPROM данных;

•1 Кбайт оперативной памяти (SRAM);

•возможность программирования непосредственно в целевой системе через последовательные интерфейсы SPI и JTAG;

•возможность внутрисхемной отладки с использованием JTAG;

•различные способы синхронизации;

•6 режимов пониженного энергопотребления;

•детектор снижения напряжения питания (BOD);

•21 источник прерываний (внутренних и внешних);

•многоуровневая система прерываний, поддержка очереди прерываний;

•возможность защиты от несанкционированного чтения и модификации памяти программ.

4

Голик С.Е.

2

20.12.2017

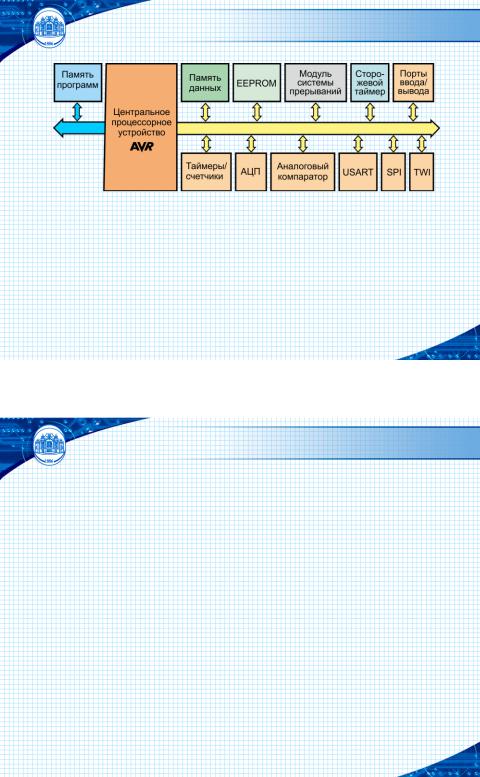

Архитектура микроконтроллеров AVR

Общие сведения

Периферийные модули микроконтроллера ATmega16A

•32 программируемые линии ввода/вывода;

•модуль прерываний с 20 источниками прерываний;

•два 8-разрядных таймера/счетчика с предварительным делителем частоты и режимом сравнения;

•16-разрядный таймер/счетчик с предварительным делителем частоты, режимами сравнения и захвата;

•четыре канала генерации выходных ШИМ-сигналов;

•сторожевой таймер WDT;

•аналоговый компаратор;

•8-канальный 10-разрядный АЦП;

•полнодуплексный универсальный синхронно/асинхронный приемопередатчик USART;

•последовательный синхронный интерфейс SPI, используемый также для программирования Flashпамяти программ;

•последовательный двухпроводный интерфейс TWI (аналог I2C).

5

Голик С.Е.

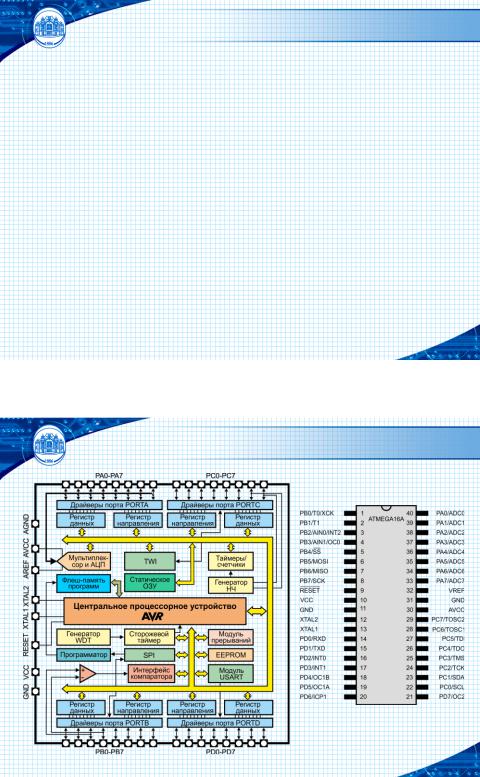

Архитектура микроконтроллеров AVR

Структура микроконтроллера ATmega16A

6

Голик С.Е.

3

20.12.2017

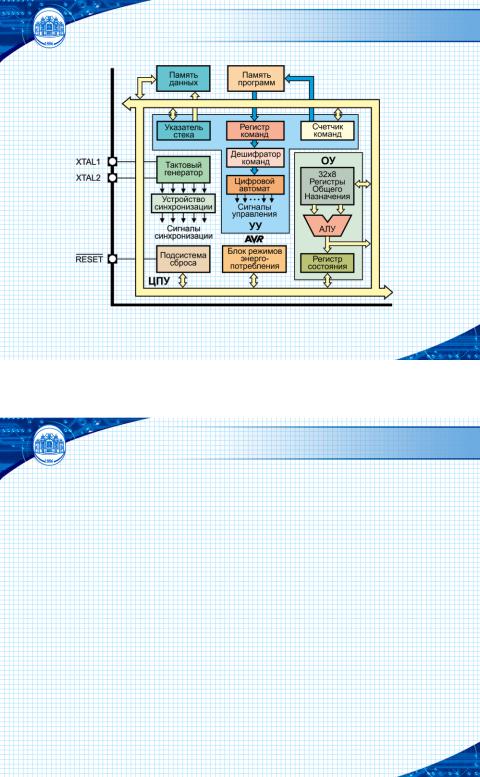

Центральное процессорное устройство AVR

Структура ЦПУ микроконтроллера Atmega16A

7

Голик С.Е.

Центральное процессорное устройство AVR

Регистр состояния SREG (Status Register)

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

Чтение/запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Бит 7 – I: Общее разрешение прерываний. При установке в 1 разрешает все прерывания, в противном случае все прерывания запрещены вне зависимости от индивидуальных разрешений.

Бит 6 – T: Хранение копируемого бита. Разряд регистра используется для временного хранения источника или приемника команд копирования битов BLD и BST.

Бит 5 – H: Флаг половинного переноса. Флаг устанавливается в 1, если произошел перенос или заем из младшей половины байта в старшую при выполнении некоторых арифметических операций.

Бит 4 – S: Флаг знака. Флаг устанавливается в 1, если результат выполнения арифметической операции меньше нуля. Равен результату (N XOR V).

Бит 3 – V: Флаг переполнения дополнительного кода. Флаг устанавливается в 1 при переполнении разрядной сетки результата при использовании знаковой арифметики.

Бит 2 – N: Флаг отрицательного значения. Этот флаг устанавливается в 1, если старший разряд результата операции равен 1 (отрицательное число).

Бит 1 – Z: Флаг нулевого значения. Этот флаг устанавливается в 1, если результат выполнения операции равен нулю.

Бит 0 – C: Флаг переноса. Этот флаг устанавливается в 1, если в результате выполнения операции произошел выход за границы байта.

8

Голик С.Е.

4

20.12.2017

Центральное процессорное устройство AVR

Процедура выборки и дешифрации команд

9

Голик С.Е.

Центральное процессорное устройство AVR

Конвейерная архитектура

R (Read) – чтение операндов

P (Process) – выполнение команды в АЛУ

W (Write) – запись результата

10

Голик С.Е.

5

20.12.2017

Центральное процессорное устройство AVR

|

|

|

|

Тактовый генератор |

|||

|

|

|

|

|

|

|

|

|

Биты конфигурации |

|

|||||

Режим работы тактового |

CKSEL3 |

CKSEL2 |

CKSEL1 |

CKSEL0 |

CKOPT |

Диапазон частот |

|

генератора |

|||||||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Внешний сигнал синхронизации |

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 / 0 |

0 ÷ 16 MHz |

|

|

0pF/36pF |

||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Внутренняя RC-цепочка |

0 |

0 |

0 |

1 |

1 |

1 MHz |

|

|

0 |

0 |

1 |

0 |

1 |

2 MHz |

|

|

0 |

0 |

1 |

1 |

1 |

4 MHz |

|

|

0 |

1 |

0 |

0 |

1 |

8 MHz |

|

Внешняя RC-цепочка |

0 |

1 |

0 |

1 |

1 / 0 |

0.1 ÷ 0.9 MHz |

|

|

|||||||

|

0pF/36pF |

||||||

|

|

|

|

|

|

||

|

0 |

1 |

1 |

0 |

1 / 0 |

0.9 ÷ 3 MHz |

|

|

0pF/36pF |

||||||

|

|

|

|

|

|

||

|

0 |

1 |

1 |

1 |

1 / 0 |

3 ÷ 8 MHz |

|

|

0pF/36pF |

||||||

|

|

|

|

|

|

||

|

1 |

0 |

0 |

0 |

1 / 0 |

8 ÷ 12 MHz |

|

|

0pF/36pF |

||||||

|

|

|

|

|

|

||

11

Голик С.Е.

Центральное процессорное устройство AVR

|

|

|

|

Тактовый генератор |

|||

|

|

|

|

|

|

|

|

|

Биты конфигурации |

|

|||||

Режим работы тактового |

CKSEL3 |

CKSEL2 |

CKSEL1 |

CKSEL0 |

CKOPT |

Диапазон частот |

|

генератора |

|||||||

|

|

|

|

|

|||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Внешний НЧ кварцевый резонатор |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

1 / 0 |

32768 Hz |

|

|

0pF/36pF |

||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Внешний резонатор |

1 |

0 |

1 |

X |

1* |

0.4 ÷ 0.9 MHz |

|

|

1 |

1 |

0 |

X |

1 |

0.9 ÷ 3 MHz |

|

|

1 |

1 |

1 |

X |

1 |

3 ÷ 8 MHz |

|

|

1 |

0 |

1 |

X |

0 (R-to-R) |

1 ÷ 16 MHz |

|

|

1 |

1 |

0 |

X |

0 (R-to-R) |

1 ÷ 16 MHz |

|

|

1 |

1 |

1 |

X |

0 (R-to-R) |

1 ÷ 16 MHz |

|

|

|

|

|

|

|

|

|

Примечания: * − в этом режиме используется только керамический резонатор; R-to-R – максимальный размах колебаний на выходе генератора.

12

Голик С.Е.

6

20.12.2017

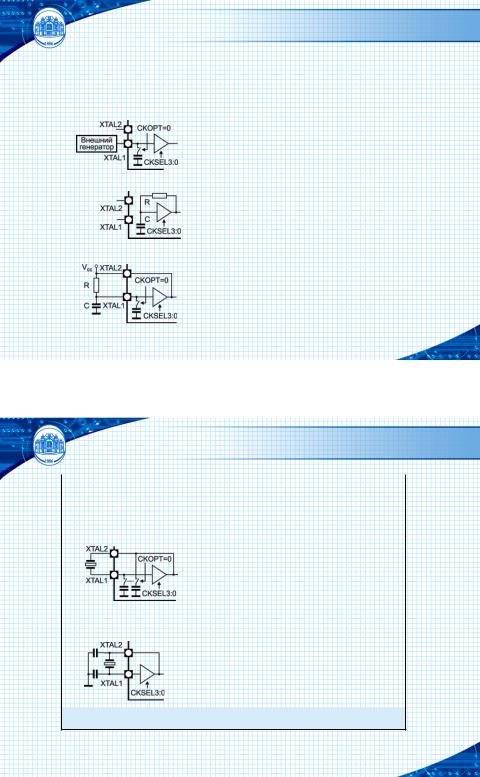

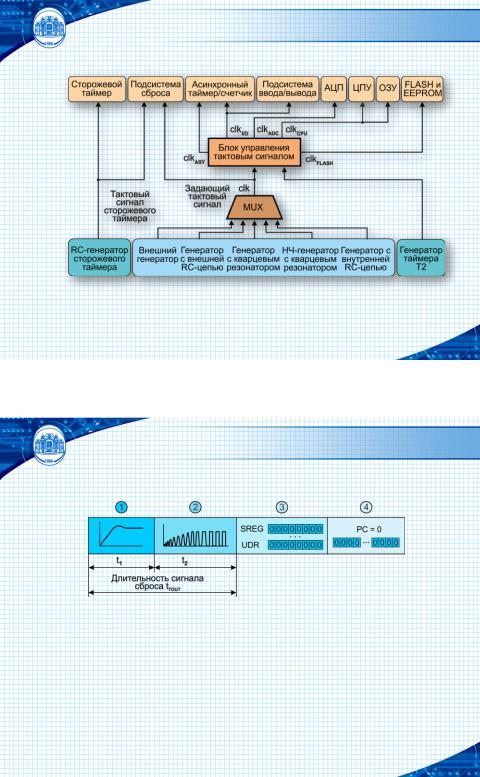

Центральное процессорное устройство AVR

Устройство синхронизации

13

Голик С.Е.

Центральное процессорное устройство AVR

Подсистема сброса

Сброс может быть вызван следующими событиями:

•включение напряжения питания микроконтроллера;

•аппаратный сброс подачей сигнала низкого уровня на вывод RESET;

•тайм-аут (переполнение) сторожевого таймера;

•падение напряжения питания ниже допустимой величины;

•сброс по интерфейсу JTAG.

14

Голик С.Е.

7

20.12.2017

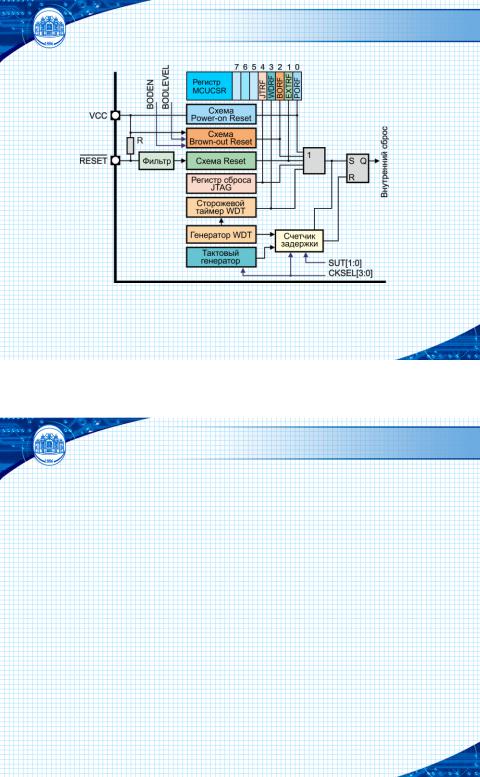

Центральное процессорное устройство AVR

Структура подсистемы сброса

15

Голик С.Е.

Центральное процессорное устройство AVR

Подсистема сброса: флаги сброса

Регистр управления и состояния МК MCUCSR (MCU Control and Status Register)

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

MCUCSR |

JTD |

ISC2 |

− |

JTRF |

WDRF |

BORF |

EXTRF |

PORF |

Чтение/запись |

R/W |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

|

См. описание битов |

|

||

Бит 4 – JTRF: Флаг JTAG-сброса. Устанавливается в 1 при сбросе по команде блока JTAG.

Бит 3 – WDRF: Флаг сброса от сторожевого таймера. Устанавливается в 1, если источником сброса был сторожевой таймер.

Бит 2 – BORF: Флаг сброса по снижению питания. Устанавливается в 1, если источником сброса была подсистема BOD.

Бит 1 – EXTRF: Флаг аппаратного сброса. Устанавливается в 1, если сброс произошел при подаче на вывод сброса сигнала низкого уровня.

Бит 0 – PORF: Флаг сброса по включению питания. Устанавливается в 1, после подачи напряжения питания на микроконтроллер.

Примечание: все флаги, кроме PORF сбрасываются при сбросе по включению питания, либо прямой записью в них 0

16

Голик С.Е.

8

20.12.2017

|

Центральное процессорное устройство AVR |

||

|

Подсистема сброса: диаграммы формирования задержки |

||

|

|

|

|

№ |

Схема |

Диаграмма формирования сигнала сброса |

|

|

Сброс по включению питания |

|

|

1 |

|

|

|

|

|

|

|

|

Сброс по включению с |

|

|

|

управлением от внешней схемы |

|

|

2 |

|

|

|

|

|

|

|

|

Аппаратный сброс |

|

|

3 |

|

|

|

|

|

|

|

|

|

17 |

|

|

|

Голик С.Е. |

|

|

|

Центральное процессорное устройство AVR |

||

|

|

Подсистема сброса: диаграммы формирования задержки |

||

|

|

|

|

|

№ |

Схема |

|

Диаграмма формирования сигнала сброса |

|

|

Сброс от сторожевого таймера |

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

Сброс при снижении напряжения |

|

|

|

|

питания |

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

18 |

||

|

|

|

Голик С.Е. |

|

9

20.12.2017

|

Центральное процессорное устройство AVR |

||||||

|

|

|

Подсистема сброса: задание режима |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

) |

|

|

Режим работы тактового |

CKSEL0 |

SUT1 |

SUT0 |

Ts, такты |

Tr, мс (5В |

Рекомендуемое использование |

|

генератора |

|

||||||

|

|

||||||

|

|

|

|||||

|

|

|

|

|

|

|

|

Внешний генератор |

− |

0 |

0 |

6 |

− |

Схема BOD включена |

|

− |

1 |

0 |

6 |

65 |

Большое время нарастания Vcc |

|

|

|

|

||||||

Генератор с внешней |

− |

0 |

0 |

18 |

− |

Схема BOD включена |

|

RC-цепочкой |

− |

1 |

0 |

18 |

65 |

Большое время нарастания Vcc |

|

|

|

||||||

Встроенный генератор |

− |

0 |

0 |

6 |

− |

Схема BOD включена |

|

с RC-цепочкой |

− |

1 |

0 |

6 |

65 |

Большое время нарастания Vcc |

|

|

|

||||||

НЧ кварцевый резонатор |

− |

0 |

1 |

1K |

65 |

Большое время нарастания Vcc |

|

− |

1 |

0 |

32K |

65 |

Стабильная частота при старте |

|

|

|

|

||||||

|

0 |

0 |

1 |

258 |

65 |

Большое время нарастания Vcc |

|

Керамический резонатор |

0 |

1 |

0 |

1K |

− |

Схема BOD включена |

|

|

1 |

0 |

0 |

1K |

65 |

Большое время нарастания Vcc |

|

Кварцевый резонатор |

1 |

0 |

1 |

16K |

− |

Схема BOD включена |

|

1 |

1 |

1 |

16K |

65 |

Большое время нарастания Vcc |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

19

Голик С.Е.

|

|

Центральное процессорное устройство AVR |

||||||||||||||

|

|

|

|

|

Блок режимов энергопотребления |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Активные |

|

|

Генера- |

Источники «пробуждения» |

|

|||||||||

|

|

внутренние |

|

|||||||||||||

|

|

торы |

|

микроконтроллера |

|

|

||||||||||

|

тактовые сигналы |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

Режим |

|

|

|

|

|

|

|

Генератор T2 |

Внешнее прерывание INT0-2 |

Модуль TWI |

Асинхронный T2 |

Готовность SPM/EEPROM |

|

|

Другие модули I/O |

|

|

CPU |

FLASH |

I/O |

ADC |

|

ASY |

|

|

АЦП |

|

||||||

|

clk |

сlk |

сlk |

сlk |

|

сlk |

clk |

|

|

|||||||

Idle |

|

|

● |

● |

|

● |

● |

■ |

● |

● |

● |

● |

|

● |

● |

|

ADC Noise Reduction |

|

|

|

● |

|

● |

● |

■ |

♦ |

● |

● |

● |

|

● |

|

|

Power Down |

|

|

|

|

|

|

|

|

♦ |

● |

|

|

|

|

|

|

Power Save |

|

|

|

|

|

■ |

|

■ |

♦ |

● |

● |

|

|

|

|

|

Standby |

|

|

|

|

|

|

● |

|

♦ |

● |

|

|

|

|

|

|

Extended Standby |

|

|

|

|

|

■ |

● |

■ |

♦ |

● |

● |

|

|

|

|

|

■ – только при работе таймера/счетчика T2 в асинхронном режиме (бит AS2=1). |

|

|

|

|||||||||||||

♦ – для любого прерывания INT2 или прерываний INT0, INT1 только по уровню |

|

|

|

|||||||||||||

В режимах Standby и Extended Standby источником тактового сигнала может быть только |

|

|||||||||||||||

генератор с кварцевым резонатором |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Голик С.Е. |

|

10