mpusu_avr_p2

.pdf

20.12.2017

Последовательный периферийный интерфейс SPI

|

|

|

Управление модулем SPI |

|

||||

Регистр управления SPI SPCR (продолжение) |

|

|

|

|

|

|||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

SPCR |

SPIE |

SPE |

DORD |

MSTR |

CPOL |

CPHA |

SPR1 |

SPR0 |

Чтение/запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 2 – CPHA: Фаза тактового сигнала. Задает фазу сигнала SCK.

•Биты 1,0 – SPR1, SPR0: Выбор частоты тактового сигнала. Задает частоту тактового сигнала SCK в соответствии с таблицей

SPR1 |

SPR0 |

Частота SCK |

0 |

0 |

fosc/4 |

0 |

1 |

fosc/16 |

1 |

0 |

fosc/64 |

1 |

1 |

fosc/128 |

101

Голик С.Е.

Последовательный периферийный интерфейс SPI

|

|

|

|

Управление модулем SPI |

|

|

|||

Регистр состояния SPI SPSR |

|

|

|

|

|

|

|

|

|

|

7 |

6 |

5 |

4 |

3 |

2 |

|

1 |

0 |

SPSR |

SPIF |

WCOL |

− |

− |

− |

− |

|

− |

SPI2X |

Чтение/запись |

R |

R |

R |

R |

R |

R |

R |

R/W |

|

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

•Бит 7 – SPIF: Флаг прерывания по SPI. По завершении обмена устанавливается в состояние 1 и, если бит SPIE в регистре SPCR установлен и разрешено глобальное прерывание, генерируется сигнал прерывания. Флаг также устанавливается, если микроконтроллер переводится из режима ведущего в режим ведомого с использованием SS. Бит SPIF очищается аппаратно при выполнении подпрограммы обработки соответствующего вектора прерывания. Бит SPIF может быть очищен также при первом считывании состояния регистра статуса SPI с установленным битом SPIF, с последующим обращением к регистру данных SPDR.

•Бит 6 – WCOL: Флаг конфликта записи. Флаг устанавливается в состояние 1, если во время передачи очередного байта была попытка записи в регистр данных SPDR. Флаг сбрасывается аппаратно после чтения регистра состояния SPI с последующим обращением к регистру данных SPDR.

•Биты 5…1 – Res: Зарезервированные биты.

•Бит 0 – SPI2X: Удвоение скорости обмена. При установленном разряде и работе в режиме ведущего частота сигнала SCK удваивается.

102

Голик С.Е.

51

20.12.2017

Последовательный периферийный интерфейс SPI

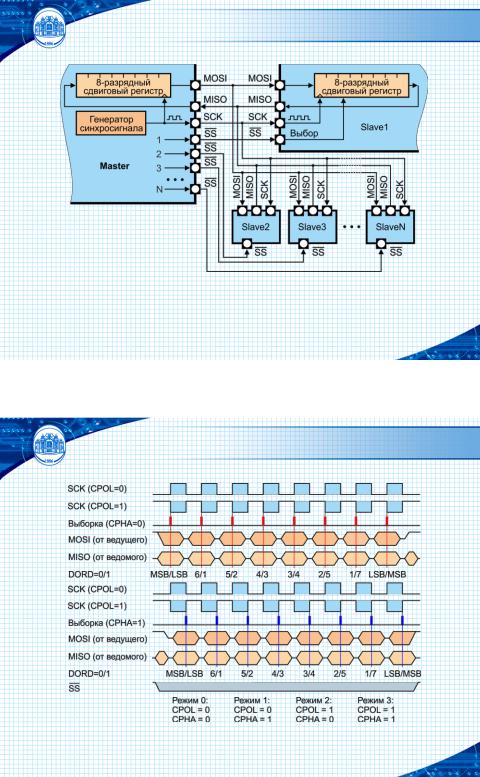

Соединение устройств с SPI-интерфейсом

Выбор ведомого устройства для обмена производится ведущим подачей на его вход SS сигнала низкого логического уровня

103

Голик С.Е.

Последовательный периферийный интерфейс SPI

Режимы передачи данных SPI

104

Голик С.Е.

52

20.12.2017

Аналоговый компаратор микроконтроллеров AVR

Управляющие регистры аналогового компаратора

Аналоговый компаратор предназначен для сравнения напряжений на выводах микроконтроллера с выдачей логического значения о результате сравнения.

Работа и управление аналоговым компаратором обеспечивается следующим набором регистров ввода-вывода

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ACSR |

ACD |

ACBG |

ACO |

ASI |

ACIE |

ACIC |

ACIS1 |

ACIS0 |

ADMUX |

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

ADCSRA |

ADEN |

ADSC |

ADATE |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

SFIOR |

ADTS2 |

ADTS1 |

ADTS0 |

− |

ACME |

PUD |

PSR2 |

PSR10 |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

•ACSR (Analog Comparator Control and Status Register) − регистр управления и состояния аналогового компаратора

•ADMUX (ADC Multiplexer) − регистр мультиплексора АЦП

•ADCSRA (ADC Control and Status Register A) − регистр состояния АЦП

•SFIOR (Special Function Input Output Register) − регистр специальных функций ввода-вывода

•SREG (Status Register) − регистр состояния

105

Голик С.Е.

Аналоговый компаратор микроконтроллеров AVR

Структура аналогового компаратора

ACME – подключение мультиплексора АЦП (регистр SFIOR)

ADEN – включение АЦП (регистр ADCSRA)

106

Голик С.Е.

53

20.12.2017

Аналоговый компаратор микроконтроллеров AVR

Управление аналоговым компаратором

Регистр управления ACSR

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ACSR |

ACD |

ACBG |

ACO |

ACI |

ACIE |

ACIC |

ACIS1 |

ACIS0 |

Чтение/запись |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

N/A |

0 |

0 |

0 |

0 |

0 |

•Бит 7 – ACD: Запрет аналогового компаратора. При установленном бите ACD аналоговый компаратор выключен. При изменении состояния бита ACD необходимо запрещать прерывание очисткой бита ACIE в регистре ACSR.

•Бит 6 – ACBG: Подключение источника опорного напряжения. При установленном бите вместо входа AIN0 подключается источник опорного напряжения.

•Бит 5 – ACO: Выход аналогового компаратора. Бит ACO связан непосредственно с выходом компаратора.

•Бит 4 – ACI: Флаг прерывания по аналоговому компаратору. Устанавливается в 1 при формировании компаратором прерывания, определяемого ACIS1 и ACIS0. Очищается аппаратно при обработке прерывания. Бит ACI можно очистить записью логической 1.

•Бит 3 – ACIE: Разрешение прерывания по аналоговому компаратору. При установленном бите

ACIE разрешается прерывание. При сброшенном бите прерывание запрещено.

•Бит 2 – ACIC: Разрешение входа захвата аналогового компаратора. Установленный в 1 бит

ACIC разрешает срабатывание функции захвата входа таймера/счетчика TС1 по переключению аналогового компаратора. В этом случае выход аналогового компаратора подсоединяется ко входной цепи канала захвата TС1.

•Биты 1,0 – ACIS1, ACIS0: Выбор режима прерывания по аналоговому компаратору. Эти биты определяют событие компаратора, при котором запускается прерывание.

107

Голик С.Е.

Аналоговый компаратор микроконтроллеров AVR

Управление аналоговым компаратором

Условия генерации запроса на прерывание от аналогового компаратора

|

ACIS1 |

ACIS0 |

|

|

|

|

Условие |

|

|

0 |

0 |

|

|

Любое изменение состояния выхода компаратора |

|

||||

0 |

1 |

|

|

Зарезервировано |

|

|

|||

1 |

0 |

|

|

Изменение состояния выхода компаратора с 1 на 0 |

|

||||

1 |

1 |

|

|

Изменение состояния выхода компаратора с 0 на 1 |

|

||||

Управление инвертирующим входом аналогового компаратора |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

ACME |

ADEN |

|

MUX2 |

MUX1 |

MUX0 |

Инвертирующий вход компаратора |

|

|

|

0 |

X |

|

|

X |

X |

X |

AIN1 |

|

|

1 |

1 |

|

|

X |

X |

X |

AIN1 |

|

|

1 |

0 |

|

0 |

0 |

0 |

ADC0 |

|

|

|

1 |

0 |

|

0 |

0 |

1 |

ADC1 |

|

|

|

1 |

0 |

|

0 |

1 |

0 |

ADC2 |

|

|

|

1 |

0 |

|

0 |

1 |

1 |

ADC3 |

|

|

|

1 |

0 |

|

1 |

0 |

0 |

ADC4 |

|

|

|

1 |

0 |

|

1 |

0 |

1 |

ADC5 |

|

|

|

1 |

0 |

|

1 |

1 |

0 |

ADC6 |

|

|

|

1 |

0 |

|

1 |

1 |

1 |

ADC7 |

|

|

ACME – разряд регистра SFIOR ADEN – разряд регистра ADCSRA

MUX2…0 – разряды регистра ADMUX

108

Голик С.Е.

54

20.12.2017

Аналого-цифровой преобразователь AVR

Назначение и основные характеристики модуля АЦП

Предназначен для преобразования аналогового напряжения на входе микроконтроллера в цифровой код.

Основные характеристики АЦП:

•10-разрядное разрешение

•интегральная нелинейность 0.5 LSB

•абсолютная погрешность ±2 LSB

•время преобразования 65 - 260 мкс.

•до 15000 выборок в секунду при максимальном разрешении

•8 мультиплексированных однополярных каналов (входов)

•7 дифференциальных входных каналов

2 дифференциальных входных канала с предварительным усилением

•встроенный ИОН на 2.56 В

•режимы одиночного и непрерывного преобразования

•режим запуска по прерыванию

•прерывание по завершении преобразования

•режим подавления шумов

109

Голик С.Е.

Аналого-цифровой преобразователь AVR

Управляющие регистры АЦП

Работа и управление аналого-цифровым преобразователем обеспечивается следующим набором регистров ввода-вывода

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ADCH |

MSB |

|

|

|

|

|

|

LSB |

ADCL |

MSB |

|

|

|

|

|

|

LSB |

ADCSRA |

ADEN |

ADSC |

ADFR |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

ADMUX |

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

SFIOR |

ADTS2 |

ADTS1 |

ADTS0 |

− |

ASME |

PUD |

PSR2 |

PSR10 |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

•ADCH (ADC High) и ADCL (ADC Low) – старший и младший байты регистра данных АЦП

•ADCSRA (ADC Control and Status Register A) − регистр управления и состояния АЦП

•ADMUX (ADC Multiplexer) − регистр мультиплексора АЦП

•SFIOR (Special Function Input Output Register) − регистр специальных функций ввода-вывода

•SREG (Status Register) − регистр состояния

110

Голик С.Е.

55

20.12.2017

Аналого-цифровой преобразователь AVR

Структура аналого-цифрового преобразователя

111

Голик С.Е.

Аналого-цифровой преобразователь AVR

Структура предделителя и схемы запуска АЦП

112

Голик С.Е.

56

20.12.2017

|

|

Аналого-цифровой преобразователь AVR |

||||||

|

|

|

|

Управление АЦП |

|

|

||

Регистр управления и состояния АЦП ADCSRA |

|

|

|

|

||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ADCSRA |

ADEN |

ADSC |

ADATE |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

Чтение/запись |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 7 – ADEN: Разрешение работы АЦП. Запись в бит 1 разрешает работу АЦП. При записи в него 0 АЦП отключается, даже если он находился в процессе преобразования.

•Бит 6 – ADSC: Запуск преобразования АЦП. В режиме одиночного преобразования установка бита инициирует старт каждого преобразования. В циклическом режиме установкой этого бита задается только первое преобразование, а все остальные выполняются автоматически. В процессе преобразования при опросе бита ADSC возвращается 1, а по его завершении – 0. Запись 0 в данный бит не оказывает никакого действия.

•Бит 5 – ADATE: Выбор циклического режима АЦП. При записи в этот бит 1 АЦП переходит в режим автоматического перезапуска, в котором АЦП автоматически выполняет преобразования и модифицирует регистры результата преобразования через фиксированные промежутки времени. Запись 0 в этот бит прекращает работу в данном режиме.

•Бит 4 – ADIF: Флаг прерывания АЦП. Флаг устанавливается после завершения преобразования АЦП и обновления регистров данных. Если установлены биты ADIE и I (регистр SREG), то происходит прерывание по завершении преобразования. Флаг ADIF сбрасывается аппаратно при переходе на соответствующий вектор прерывания. Программно флаг ADIF сбрасывается записью в него 1.

113

Голик С.Е.

|

|

Аналого-цифровой преобразователь AVR |

||||||

|

|

|

|

Управление АЦП |

|

|

||

Регистр управления и состояния АЦП ADCSRA (продолжение) |

|

|

|

|||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ADCSRA |

ADEN |

ADSC |

ADATE |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

Чтение/запись |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 3 – ADIE: Разрешение прерывания АЦП. Запись 1 в этот бит, при условии, что установлен бит I в регистре SREG, разрешает прерывание по завершении преобразования АЦП.

•Биты 2:0 – ADPS2, ADPS1, ADPS0: Биты управления предделителем АЦП. Данные биты определяют частоту синхронизации АЦП в виде коэффициента деления тактовой частоты микроконтроллера в соответствии с таблицей.

ADPS2 |

ADPS1 |

ADPS0 |

Коэффициент |

|

деления |

||||

|

|

|

||

0 |

0 |

0 |

2 |

|

0 |

0 |

1 |

2 |

|

0 |

1 |

0 |

4 |

|

0 |

1 |

1 |

8 |

|

1 |

0 |

0 |

16 |

|

1 |

0 |

1 |

32 |

|

1 |

1 |

0 |

64 |

|

1 |

1 |

1 |

128 |

114

Голик С.Е.

57

20.12.2017

|

|

Аналого-цифровой преобразователь AVR |

||||||

|

|

|

|

Управление АЦП |

|

|

||

Регистр управления мультиплексором АЦП ADMUX |

|

|

|

|

||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

ADMUX |

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

Чтение/запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Исх. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Биты 7,6 – REFS1, REFS0: Биты выбора источника опорного напряжения. Биты определяют,

какое напряжение будет использоваться в качестве опорного для АЦП. Доступны следующие источники опорного напряжения.

REFS1 |

REFS0 |

Источник опорного напряжения |

0 |

0 |

AREF, внутренний ИОН отключен |

0 |

1 |

AVCC с внешним конденсатором на выводе AREF |

1 |

0 |

Зарезервировано |

1 |

1 |

Внутренний ИОН 2.56В с внешним конденсатором на выводе AREF |

Бит 5 – ADLAR: Бит управления представлением результата преобразования. Бит задает представление результата преобразования в паре регистров результата преобразования АЦП. Если ADLAR = 1, то результат преобразования будет иметь левосторонний формат, в противном случае – правосторонний.

Биты 4:0 – MUX4-MUX0: Биты выбора аналогового канала и коэффициента усиления.

Определяют, какие из аналоговых входов подключаются к АЦП. Кроме того, с их помощью выбирается коэффициент усиления для дифференциальных каналов.

115

Голик С.Е.

Аналого-цифровой преобразователь AVR

Выбор аналогового канала и коэффициента усиления

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

Дифференциальный вход |

||

Прямой |

Инверсный |

Ку |

|||||

|

|

|

|||||

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

ADC0 |

ADC0 |

10 |

0 |

1 |

0 |

0 |

1 |

ADC1 |

ADC0 |

10 |

0 |

1 |

0 |

1 |

0 |

ADC0 |

ADC0 |

200 |

0 |

1 |

0 |

1 |

1 |

ADC1 |

ADC0 |

200 |

0 |

1 |

1 |

0 |

0 |

ADC2 |

ADC2 |

10 |

0 |

1 |

1 |

0 |

1 |

ADC3 |

ADC2 |

10 |

0 |

1 |

1 |

1 |

0 |

ADC2 |

ADC2 |

200 |

0 |

1 |

1 |

1 |

1 |

ADC3 |

ADC2 |

200 |

1 |

0 |

0 |

0 |

0 |

ADC0 |

ADC1 |

1 |

1 |

0 |

0 |

0 |

1 |

ADC1 |

ADC1 |

1 |

1 |

0 |

0 |

1 |

0 |

ADC2 |

ADC1 |

1 |

1 |

0 |

0 |

1 |

1 |

ADC3 |

ADC1 |

1 |

1 |

0 |

1 |

0 |

0 |

ADC4 |

ADC1 |

1 |

1 |

0 |

1 |

0 |

1 |

ADC5 |

ADC1 |

1 |

1 |

0 |

1 |

1 |

0 |

ADC6 |

ADC1 |

1 |

1 |

0 |

1 |

1 |

1 |

ADC7 |

ADC1 |

1 |

1 |

1 |

0 |

0 |

0 |

ADC0 |

ADC2 |

1 |

1 |

1 |

0 |

0 |

1 |

ADC1 |

ADC2 |

1 |

1 |

1 |

0 |

1 |

0 |

ADC2 |

ADC2 |

1 |

1 |

1 |

0 |

1 |

1 |

ADC3 |

ADC2 |

1 |

1 |

1 |

1 |

0 |

0 |

ADC4 |

ADC2 |

1 |

1 |

1 |

1 |

0 |

1 |

ADC5 |

ADC2 |

1 |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

Несимметричный |

вход |

|||||

|

|||||

0 |

0 |

0 |

0 |

0 |

ADC0 |

0 |

0 |

0 |

0 |

1 |

ADC1 |

0 |

0 |

0 |

1 |

0 |

ADC2 |

0 |

0 |

0 |

1 |

1 |

ADC3 |

0 |

0 |

1 |

0 |

0 |

ADC4 |

0 |

0 |

1 |

0 |

1 |

ADC5 |

0 |

0 |

1 |

1 |

0 |

ADC6 |

0 |

0 |

1 |

1 |

1 |

ADC7 |

1 |

1 |

1 |

1 |

0 |

1.22В (VBG) |

1 |

1 |

1 |

1 |

1 |

0В (GND) |

116

Голик С.Е.

58

20.12.2017

|

|

Аналого-цифровой преобразователь AVR |

||||||||

|

|

Задание источника стартового сигнала АЦП |

|

|||||||

Регистр специальных функций ввода-вывода SFIOR |

|

|

|

|

|

|

||||

|

7 |

6 |

5 |

|

4 |

3 |

2 |

1 |

|

0 |

SFIOR |

ADTS2 |

ADTS1 |

ADTS0 |

|

− |

ASME |

PUD |

PSR2 |

|

PSR10 |

Чтение/запись |

R/W |

R/W |

R/W |

R |

R/W |

R/W |

R/W |

R/W |

||

Нач. значение |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

|

0 |

Биты 7-5 – ADTS2-ADTS0: Выбор источника запуска АЦП. Если разряд ADATE регистра

ADCSRA установлен в 1, то значения, записанные в эти разряды, будут определять источник запуска АЦП. Преобразование будет запускаться при установке в 1 флага прерывания, выбранного в соответствии с таблицей.

ADTS2 |

ADTS1 |

ADTS0 |

Источник стартового сигнала |

|

|||

0 |

0 |

0 |

Режим непрерывного преобразования |

0 |

0 |

1 |

Прерывание от аналогового компаратора |

0 |

1 |

0 |

Внешнее прерывание INT0 |

0 |

1 |

1 |

Прерывание по событию "Совпадение" таймера/счетчика ТC0 |

1 |

0 |

0 |

Прерывание по переполнению таймера/счетчика ТC0 |

1 |

0 |

1 |

Прерывание по событию "Совпадение" таймера/счетчика ТC1 |

1 |

1 |

0 |

Прерывание по переполнению таймера/счетчика ТC1 |

1 |

1 |

1 |

Прерывание по событию "Захват" таймера/счетчика ТC1 |

117

Голик С.Е.

59