mpusu_avr_p2

.pdf

20.12.2017

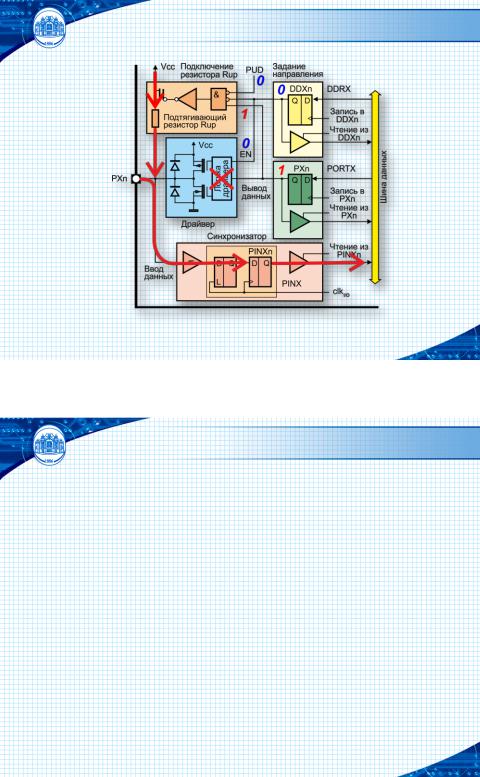

Модуль параллельных портов ввода-вывода

Настройка порта на вход с подтягивающим резистором

41

Голик С.Е.

Модуль параллельных портов ввода-вывода

Альтернативные функции портов МК ATmega16A

|

PORTA |

|

|

Вывод |

Альтернативная функция |

PA0 |

ADC0 – вход АЦП канал 0 |

PA1 |

ADC1 – вход АЦП канал 1 |

РA2 |

ADC2 – вход АЦП канал 2 |

РA3 |

ADC3 – вход АЦП канал 3 |

РA4 |

ADC4 – вход АЦП канал 4 |

РA5 |

ADC5 – вход АЦП канал 5 |

РA6 |

ADC6 – вход АЦП канал 6 |

РA7 |

ADC7 – вход АЦП канал 7 |

|

PORTC |

Вывод |

Альтернативная функция |

PС0 |

SCL – тактовый сигнал модуля TWI |

PС1 |

SCA – данные модуля TWI |

PС2 |

TCK – тактовый сигнал JTAG |

PС3 |

TMS – выбор режима JTAG |

PС4 |

TDO – выход данных JTAG |

PС5 |

TDI – вход данных JTAG |

PС6 |

TOSC1 – подключение кварца ТC2 |

PС7 |

TOSC2 – подключение кварца ТC2 |

|

PORTB |

|

|

Вывод |

Альтернативная функция |

PB0 |

Т0 – вход внешнего сигнала ТC0 |

PB1 |

Т1 – вход внешнего сигнала ТC1 |

РВ2 |

AIN0/INT2 – вход «+» аналогового компа- |

ратора/вход внешнего прерывания INT2 |

|

РВ3 |

AIN1/OC0 – вход «–» аналогового компа- |

ратора/выход совпадения таймера Т0 |

|

РВ4 |

SS – выбор Slave устройства в канале SPI |

РВ5 |

MOSI – вход данных канала SPI |

РВ6 |

MISO – выход данных канала SPI |

РВ7 |

SCK – вход тактовых импульсов SPI |

|

PORTD |

Вывод |

Альтернативная функция |

PD0 |

RXD – вход данных UART |

PD1 |

TXD – выход данных UART |

PD2 |

INTO – Вход внешнего прерывания 0 |

PD3 |

INT1 – Вход внешнего прерывания 1 |

PD4 |

OC1B – выход сравнения ТC1 |

PD5 |

OC1А – выход сравнения ТC1 |

PD6 |

ICP – вход захвата T1 |

PD7 |

OC2 – выход сравнения ТC2 |

42

Голик С.Е.

21

20.12.2017

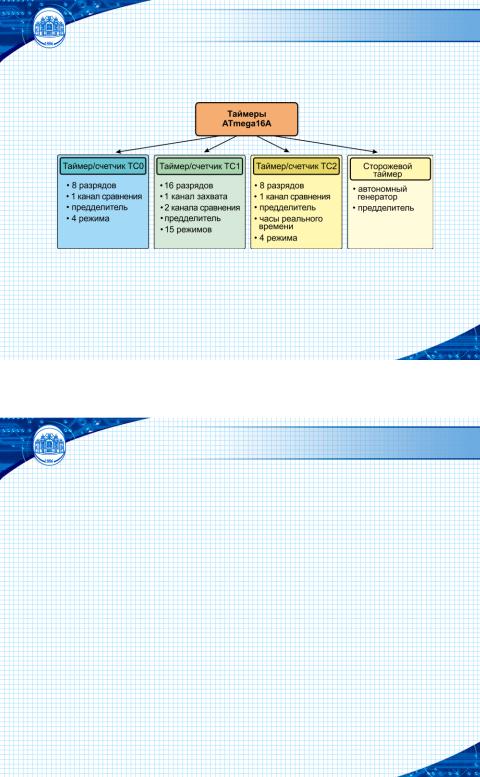

Таймеры/счетчики микроконтроллеров AVR

43

Голик С.Е.

Таймеры/счетчики микроконтроллеров AVR

Рабочие и управляющие регистры таймера/счетчика TC0

Работа и управление таймером/счетчиком TC0 обеспечивается следующим набором регистров ввода-вывода

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TCNT0 |

MSB |

|

|

|

|

|

|

LSB |

OCR0 |

MSB |

|

|

|

|

|

|

LSB |

TCCR0 |

FOC0 |

WGM00 |

COM01 |

COM00 |

WGM01 |

CS02 |

CS01 |

CS00 |

TIFR |

OCF2 |

TOV2 |

ICF1 |

OCF1A |

OCF1B |

TOV1 |

OCF0 |

TOV0 |

TIMSK |

OCIE2 |

TOIE2 |

TICIE1 |

OCIE1A |

OCIE1B |

TOIE1 |

OCIE0 |

TOIE0 |

SFIOR |

ADTS2 |

ADTS1 |

ADTS0 |

− |

ASME |

PUD |

PSR2 |

PSR10 |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

•TCNT0 (Timer/Counter0) − счетный регистр

•OCR0 (Timer/Counter0 Output Compare Register) − регистр сравнения

•TCCR0 (Timer/Counter0 Control Register) − регистр управления TC0

•TIFR (Timer/Counter Interrupt Flag Register) − регистр флагов прерываний таймеров

•TIMSK (Timer/Counter Interrupt Mask Register) − регистр разрешения прерываний таймеров

•SFIOR (Special Function Input Output Register) − регистр специальных функций ввода-вывода

•SREG (Status register) − регистр состояния

LSB, MSB − младший и старший значащие биты соответственно

44

Голик С.Е.

22

20.12.2017

Таймеры/счетчики микроконтроллеров AVR

Структура таймера/счетчика TC0

45

Голик С.Е.

Таймеры/счетчики микроконтроллеров AVR

Модули счетчика и сравнения таймера/счетчика TC0

Модуль счетчика

Модуль сравнения

TCNT0 – 8-разрядный счетный регистр Счет – инкремент или декремент TCNT0 Сброс – установка всех бит TCNT0 в 0 Направление – выбор между инкрементом и декрементом

BOTTOM – нижний предел счета TOP – верхний предел счета

46

Голик С.Е.

23

20.12.2017

Таймеры/счетчики микроконтроллеров AVR

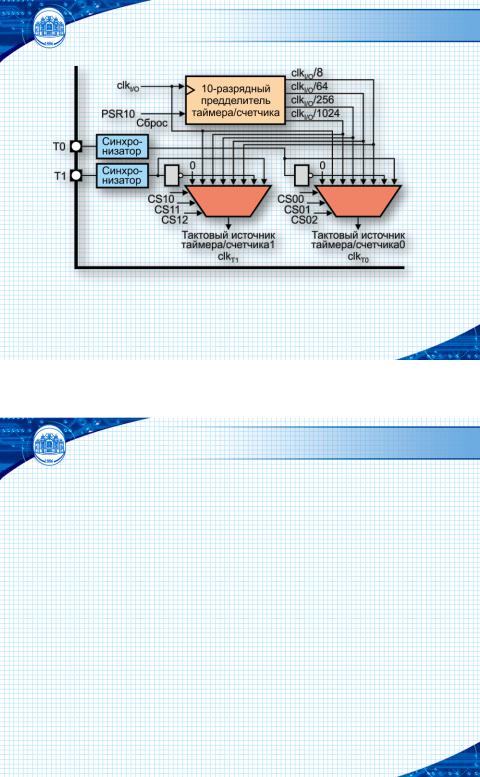

Предделитель таймеров/счетчиков TC0 и TC1

PSR10 – бит сброса предделителя (разряд 0 регистра SFIOR)

47

Голик С.Е.

|

|

Таймеры/счетчики микроконтроллеров AVR |

||||||

|

|

|

Управление таймером/счетчиком TC0 |

|

||||

Регистр управления таймером/счетчиком TCCR0 |

|

|

|

|

||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TCCR0 |

FOC0 |

WGM00 |

COM01 |

COM00 |

WGM01 |

CS02 |

CS01 |

CS00 |

Чтение/запись |

W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 7 – FOC0: Принудительное изменение состояния вывода OC0. Активен только в режимах Normal и CTC. Запись 1 в разряд FOC0 приводит к изменению состояния вывода OC0 в соответствии с установками разрядов COM01, COM00. Прерывание при этом не генерируется и сброс таймера (в режиме CTC) не производится. В режимах с PWM разряд должен быть сброшен в 0. При чтении FOC0 всегда считывается как 0.

•Биты 6, 3 – WGM00, WGM01: Режим работы таймера-счетчика TC0. Данные биты определяют алгоритм счета, источник задания верхнего предела счета и тип генерируемых прямоугольных импульсов на выводе OC0.

№ |

WGM01 |

WGM00 |

Название режима |

Модуль счета TOP |

Обновление OCR0 |

Установка флага TOV0 |

|

|

|||||

0 |

0 |

0 |

Normal |

0xFF |

Немедленно |

MAX |

1 |

0 |

1 |

Phase Correct PWM (ШИМ с точной фазой) |

0xFF |

TOP |

BOTTOM |

2 |

1 |

0 |

CTC (сброс при совпадении) |

OCR0 |

Немедленно |

MAX |

3 |

1 |

1 |

Fast PWM (быстрый ШИМ) |

0xFF |

BOTTOM |

MAX |

48

Голик С.Е.

24

20.12.2017

|

|

Таймеры/счетчики микроконтроллеров AVR |

||||||

|

|

|

Управление таймером/счетчиком TC0 |

|

||||

Регистр управления таймером/счетчиком TCCR0 (продолжение) |

|

|

|

|||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TCCR0 |

FOC0 |

WGM00 |

COM01 |

COM00 |

WGM01 |

CS02 |

CS01 |

CS00 |

Чтение/запись |

W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Биты 5, 4 – COM01, COM00: Режим формирования выходного сигнала. Данные биты определяют алгоритм изменения сигнала на выводе OC0 при совпадении содержимого счетного регистра и регистра сравнения. Установки, задаваемые этими разрядами, зависят от выбранного режима работы таймера.

•Биты 2:0 – CS02, CS01, CS00: Управление тактовым сигналом. Эти разряды определяют источник тактового сигнала таймера/счетчика.

CS02 |

CS01 |

CS00 |

Описание |

0 |

0 |

0 |

Таймер/счетчик 0 остановлен |

0 |

0 |

1 |

clkI/O |

0 |

1 |

0 |

clkI/O/8 |

0 |

1 |

1 |

clkI/O/64 |

1 |

0 |

0 |

clkI/O/256 |

1 |

0 |

1 |

clkI/O/1024 |

1 |

1 |

0 |

Внешний контакт TC0, инкрементирование TCNT0 по срезу сигнала |

1 |

1 |

1 |

Внешний контакт TC0, инкрементирование TCNT0 по фронту сигнала |

49

Голик С.Е.

Таймеры/счетчики микроконтроллеров AVR

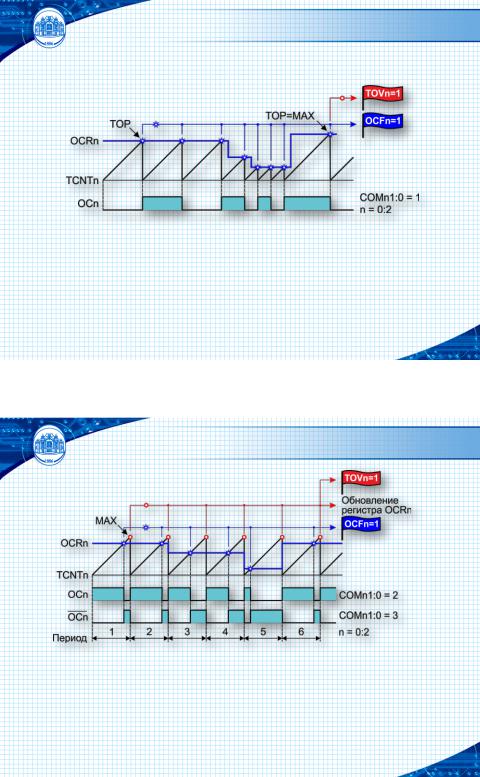

Режимы работы таймера/счетчика TC0

Режим Normal

COMn1 |

COMn0 |

Формирование сигнала на выводе OCn |

0 |

0 |

Таймер/счетчик отключен от вывода OCn |

0 |

1 |

Инверсия вывода OCn при совпадении TCNTn и OCRn |

1 |

0 |

Вывод сбрасывается в 0 при совпадении TCNTn и OCRn |

1 |

1 |

Вывод устанавливается в 1 при совпадении TCNTn и OCRn |

50

Голик С.Е.

25

20.12.2017

Таймеры/счетчики микроконтроллеров AVR

Режимы работы таймера/счетчика TC0

Режим CTC (сброс при совпадении)

COMn1 |

COMn0 |

Формирование сигнала на выводе OCn |

0 |

0 |

Таймер/счетчик отключен от вывода Ocn |

0 |

1 |

Инверсия вывода OCn при совпадении TCNTn и OCRn |

1 |

0 |

Вывод сбрасывается в 0 при совпадении TCNTn и OCRn |

1 |

1 |

Вывод устанавливается в 1 при совпадении TCNTn и OCRn |

51

Голик С.Е.

Таймеры/счетчики микроконтроллеров AVR

Режимы работы таймера/счетчика TC0

Режим Fast PWM (Быстрый ШИМ)

COMn1 |

COMn0 |

Формирование сигнала на выводе OCn |

|

0 |

0 |

Таймер/счетчик отключен от вывода OCn |

|

0 |

1 |

Зарезервировано |

|

1 |

0 |

Вывод OCn сбрасывается в 0 при совпадении содержимого TCNTn |

|

и OCRn. Устанавливается в 1 при TCNT0 = 0x00 |

|||

|

|

||

1 |

1 |

Вывод OCn устанавливается в 1 при совпадении содержимого |

|

TCNTn и OCRn. Сбрасывается в 0 при TCNTn = 0x00 |

|||

|

|

52

Голик С.Е.

26

20.12.2017

Таймеры/счетчики микроконтроллеров AVR

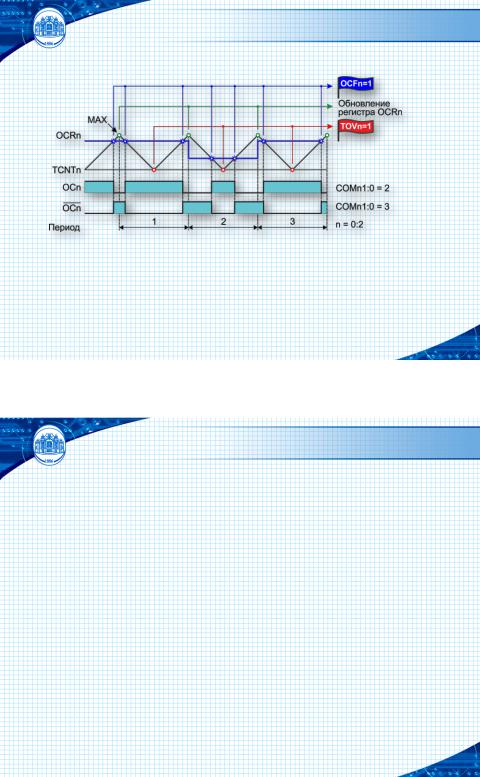

Режимы работы таймера/счетчика TC0

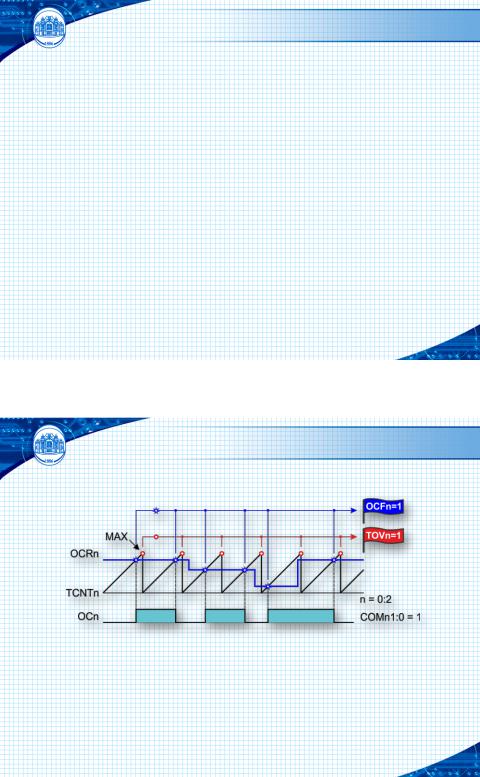

Режим Phase Correct PWM (ШИМ с точной фазой)

COMn1 |

COMn0 |

Формирование сигнала на выводе OCn |

|

0 |

0 |

Таймер/счетчик отключен от вывода OCn |

|

0 |

1 |

Зарезервировано |

|

1 |

0 |

Сбрасывается в 0 при совпадении на прямом счете и |

|

устанавливается в 1 при совпадении на обратном счете. |

|

||

|

|

|

|

1 |

1 |

Устанавливается в 1 при совпадении на прямом счете и |

|

сбрасывается в 0 при совпадении на обратном счете |

|

||

|

|

53 |

|

|

|

|

|

|

|

|

Голик С.Е. |

|

|

Таймеры/счетчики микроконтроллеров AVR |

||||||

|

|

|

Прерывания от таймера/счетчика TC0 |

|

||||

Регистр флагов прерываний таймеров TIFR |

|

|

|

|

|

|||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TIFR |

OCF2 |

TOV2 |

ICF1 |

OCF1A |

OCF1B |

TOV1 |

OCF0 |

TOV0 |

Чтение/запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 1 – OCF0: Флаг совпадения выхода TC0. Бит OCF0 устанавливается при совпадении содержимого счетного регистра TCNT0 и регистра сравнения OCR0. Сбрасывается аппаратно при обработке прерывания. Очистка бита производится записью логической 1.

•Бит 0 – TOV0: Флаг переполнения TC0. Устанавливается при переполнении T0. Сбрасывается аппаратно при обработке прерывания. Очистка бита производится записью логической 1.

Регистр разрешения прерываний TIMSK

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TIMSK |

OCIE2 |

TOIE2 |

TICIE1 |

OCIE1A |

OCIE1B |

TOIE1 |

OCIE0 |

TOIE0 |

Чтение/запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 0 – TOIE0: Разрешение прерывания по переполнению TC0. Установка в 1

разрешает прерывание по переполнению T0.

•Бит 1 – OCIE0: Разрешение прерывания по совпадению TC0. Установка в 1 разрешает прерывание по совпадению содержимого счетного регистра и регистра сравнения T0.

54

Голик С.Е.

27

20.12.2017

Таймеры/счетчики микроконтроллеров AVR

Рабочие и управляющие регистры таймера/счетчика TC2

Работа и управление таймером/счетчиком T2 обеспечивается следующим набором регистров ввода-вывода

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TCNT2 |

MSB |

|

|

|

|

|

|

LSB |

OCR2 |

MSB |

|

|

|

|

|

|

LSB |

TCCR2 |

FOC2 |

WGM20 |

COM21 |

COM20 |

WGM21 |

CS22 |

CS21 |

CS20 |

TIFR |

OCF2 |

TOV2 |

ICF1 |

OCF1A |

OCF1B |

TOV1 |

OCF0 |

TOV0 |

TIMSK |

OCIE2 |

TOIE2 |

TICIE1 |

OCIE1A |

OCIE1B |

TOIE1 |

OCIE0 |

TOIE0 |

ASSR |

− |

− |

− |

− |

AS2 |

TCN2UB |

OCR2UB |

TDR2UB |

SFIOR |

ADTS2 |

ADTS1 |

ADTS0 |

− |

ASME |

PUD |

PSR2 |

PSR10 |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

•TCNT2 (Timer/Counter 2) − счетный регистр

•OCR2 (Timer/Counter2 Output Compare Register) − регистр выхода сравнения

•TCCR2 (Timer/Counter Control Register 2) − регистр управления

•TIFR (Timer/Counter Interrupt Flag Register) − регистр флагов прерываний таймеров

•TIMSK (Timer/Counter Interrupt Mask Register) − регистр разрешения прерываний таймеров

•ASSR (Asynchronous Status Register) − асинхронный регистр состояния

•SFIOR (Special Function Input Output Register) − регистр специальных функций ввода-вывода

•SREG (Status register) − регистр состояния

LSB, MSB − младший и старший значащие биты соответственно

55

Голик С.Е.

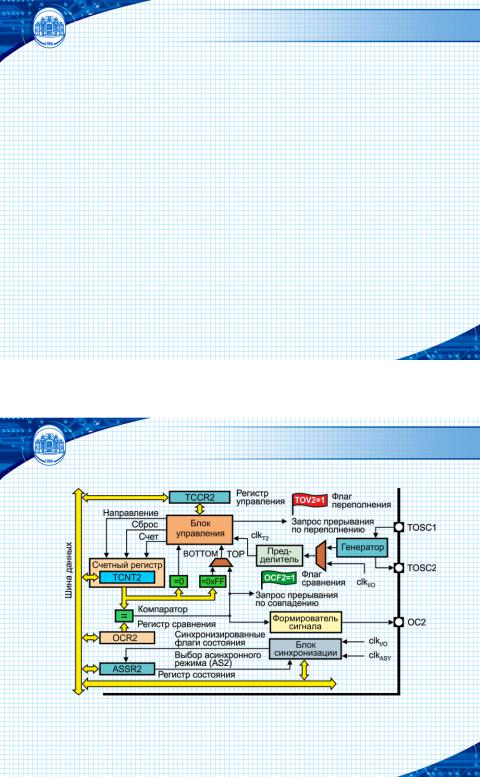

Таймеры/счетчики микроконтроллеров AVR

Структура таймера/счетчика TC2

56

Голик С.Е.

28

20.12.2017

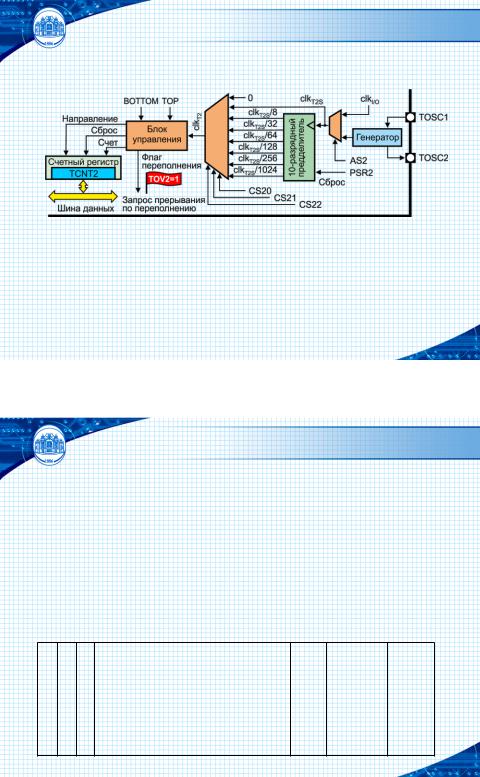

Таймеры/счетчики микроконтроллеров AVR

Модуль счетчика таймера/счетчика T2

TCNT2 – 8-разрядный счетный регистр

Счет – инкремент или декремент TCNT2 Сброс – установка всех бит TCNT2 в 0

Направление – выбор между инкрементом и декрементом BOTTOM – нижний предел счета

TOP – верхний предел счета

PSR2 – бит сброса предделителя (разряд 1 регистра SFIOR) AS2 – пререключение в асинхронный режим

57

Голик С.Е.

|

|

Таймеры/счетчики микроконтроллеров AVR |

||||||

|

|

|

Управление таймером/счетчиком TC2 |

|

||||

Регистр управления таймером/счетчиком TCCR2 |

|

|

|

|

||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TCCR2 |

FOC2 |

WGM20 |

COM21 |

COM20 |

WGM21 |

CS22 |

CS21 |

CS20 |

Чтение/запись |

W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Бит 7 – FOC2: Принудительное изменение состояния вывода OC2. Активен только в режимах Normal и CTC. Запись 1 в разряд FOC2 приводит к изменению состояния вывода OC2 в соответствии с установками разрядов COM21, COM20. Прерывание при этом не генерируется и сброс таймера (в режиме CTC) не производится. В режимах с PWM разряд должен быть сброшен в 0. При чтении FOC2 всегда считывается как 0.

•Биты 6, 3 – WGM20, WGM21: Режим работы таймера-счетчика TC2. Данные биты определяют алгоритм счета, источник задания верхнего предела счета и тип генерируемых прямоугольных импульсов на выводе OC0.

№ |

WGM21 |

WGM20 |

Название режима |

Модуль счета TOP |

Обновление OCR2 |

Установка Флага TOV2 |

|

|

|||||

0 |

0 |

0 |

Normal |

0xFF |

Немедленно |

MAX |

1 |

0 |

1 |

Phase Correct PWM (ШИМ с точной фазой) |

0xFF |

TOP |

BOTTOM |

2 |

1 |

0 |

CTC (сброс при совпадении) |

OCR2 |

Немедленно |

MAX |

3 |

1 |

1 |

Fast PWM (быстрый ШИМ) |

0xFF |

BOTTOM |

MAX |

58

Голик С.Е.

29

20.12.2017

|

|

Таймеры/счетчики микроконтроллеров AVR |

||||||

|

|

|

Управление таймером/счетчиком TC2 |

|

||||

Регистр управления таймером/счетчиком TCCR2 (продолжение) |

|

|

|

|||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

TCCR2 |

FOC2 |

WGM20 |

COM21 |

COM20 |

WGM21 |

CS22 |

CS21 |

CS20 |

Чтение/запись |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

•Биты 5, 4 – COM21, COM20: Режим формирования выходного сигнала. Данные биты определяют алгоритм изменения сигнала на выводе OC2 при совпадении содержимого счетного регистра и регистра сравнения. Установки, задаваемые этими разрядами, зависят от выбранного режима работы таймера.

•Биты 2:0 – CS22, CS21, CS20: Управление тактовым сигналом. Эти разряды определяют источник тактового сигнала таймера/счетчика.

CS22 |

CS21 |

CS20 |

Описание |

0 |

0 |

0 |

Таймер/счетчик TС2 остановлен |

0 |

0 |

1 |

clkT2S |

0 |

1 |

0 |

clkT2S/8 |

0 |

1 |

1 |

clkT2S/32 |

1 |

0 |

0 |

clkT2S/64 |

1 |

0 |

1 |

clkT2S/128 |

1 |

1 |

0 |

clkT2S/256 |

1 |

1 |

1 |

clkT2S/1024 |

59

Голик С.Е.

|

|

Таймеры/счетчики микроконтроллеров AVR |

|||||||

|

|

Управление асинхронным режимом таймера/счетчика TC2 |

|||||||

Регистр статуса асинхронного режима ASSR2 |

|

|

|

|

|

||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

ASSR |

− |

− |

− |

− |

AS2 |

TCN2UB |

OCR2UB |

TDR2UB |

|

Чтение/запись |

R |

R |

R |

R |

R/W |

R |

R |

R |

|

Нач. значение |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

•Биты 7…4 – Зарезервированные биты

•Бит 3 – AS2: Асинхронный режим таймера/счетчика2. При установленном состоянии бита TC2 тактируется сигналом вывода TOSC1, при сброшенном бите – внутренним тактовым сигналом CK. При изменении состояния этого бита содержимое TCNT2 может быть повреждено

•Бит 2 – TCN2UB: Счетный регистрTCNT2 занят для обновления. При работе TC2 в

асинхронном режиме бит устанавливается в 1 при записанном TCNT2. При обновлении TCNT2 содержимым регистра временного хранения бит аппаратно очищается. Обновление TCNT2 можно производить только при сброшенном бите

•Бит 1 – OCR2UB: Регистр сравнения выхода OCR2 занят для обновления. При работе TC2 в

асинхронном режиме бит устанавливается в 1 при записанном OCR2. При обновлении OCR2 содержимым регистра временного хранения бит аппаратно очищается. Обновление OCR2 можно производить только при сброшенном бите

•Бит 0 – TCR2UB: Регистр управления TCCR занят для обновления. При работе TC2 в

асинхронном режиме бит устанавливается в 1 при записанном TCCR2. При обновлении TCCR2 содержимым регистра временного хранения бит аппаратно очищается. Обновление TCCR2 можно производить только при сброшенном бите

60

Голик С.Е.

30