- •Курс лекций «Вычислительные машины, системы и сети»

- •Часть 1. Вычислительные машины. 3

- •Часть 2. Вычислительные системы. 203

- •Часть 3. Вычислительные сети. 254

- •Часть 1. Вычислительные машины.

- •Лекция 1. Структура вычислительной машины.

- •1.1 Общее устройство

- •1.2 Корпус pc

- •1.3 Материнская плата

- •1.4 Процессор

- •1.5 Устройства хранения данных

- •Лекция 2. Эволюция микрокомпьютеров.

- •1.1.Основные направления эволюции микрокомпьютеров.

- •Лекция 3. Машинная организация процессора 80286

- •1.1. Введение.

- •2.2. Структура памяти.

- •2.3. Сегментация памяти.

- •2.4. Структура ввода-вывода.

- •2.5. Регистры.

- •Лекция 4. Операнды и режимы адресации операндов.

- •Лекция 5. Общая организация памяти.

- •Лекция 6. Прерывание микропроцессора в эвм.

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Лекция 7. Последовательный интерфейс rs–232c.

- •Общие сведения о интерфейсе rs–232c

- •Виды сигналов

- •Тестовое оборудование для интерфейса rs–232c

- •Лекция 8. Последовательный интерфейс сом-порт.

- •Использование сом-портов

- •Функции bios для сом-портов

- •Лекция 9. Программируемый связной интерфейс.

- •Лекция 10. Передача данных между эвм с помощью модемов. Типы и характеристики модемов.Набор ат-команд.

- •Лекция 11. Программируемый периферийный интерфейс.

- •Лекция 12. Параллельный интерфейс:lpt-порт.

- •Интерфейс Centronics

- •Сигналы интерфейса Centronics

- •Традиционный lpt-порт

- •Функции bios для lpt-порта

- •Расширения параллельного порта

- •Физический и электрический интерфейс

- •Режимы передачи данных

- •Полубайтный режим ввода — Nibble Mode

- •Конфигурирование lpt-портов

- •Использование параллельных портов

- •Неисправности и тестирование параллельных портов

- •Лекция 13. Программируемые таймеры и счетчики событий.

- •Лекция 14. Универсальная последовательная шина usb.

- •2.Шина usb.Общая характеристика.

- •Структура usb

- •3.Физический интерфейс

- •Протокол

- •Устройства usb - функции и хабы

- •Хост-контроллер

- •Лекция 15. Протокол работы usb-шины.

- •Описание протоколов используемых при передаче данных Структура usb пакета

- •Поля usb пакета

- •Типы usb пакетов

- •Приоритеты передач по usb-шине

- •Источники информации

- •Лекция 16. Интерфейс ieee-1394 (FireWire).

- •Технические характеристики

- •Топология шины

- •Пример топологии ieee-1394

- •Совместимость

- •Кабели и разъемы

- •Список литературы

- •Лекция 17. Организация прямого доступа к памяти.

- •Лекция 18. Устройства ввода эвм. Клавиатура. Введение

- •1. Основные части клавиатуры

- •1.1. Клавиши пишущей машинки (алфавитно-цифровая клавиатура)

- •Режимы ввода символов

- •Названия специальных знаков

- •1.2. Служебные клавиши

- •Индикаторы режимов

- •Клавиши управления курсором

- •1.3. Функциональные клавиши

- •1.4. Малая цифровая клавиатура

- •2. Принципы работы клавиатуры

- •Лекция 19. Интерфейс эвм с видеотерминалом. Видеоадаптер. Режимы изображений: текстовый и графический режимы. Видеопамять. Анимация изображений. Интерфейс эвм с видеотерминалом.

- •Видеоадаптер.

- •Лекция 20. Накопитель магнитных дисков: гибкий и жесткий. Структура дисков: дорожки, сектора, блоки. Обмен информации между эвм и магнитными дисками.

- •Лекция 21. Сканер. Считывание изображения. Типы обрабатываемых изображений. Качество изображения.

- •Лекция 22. Назначение и функции операционной системы.

- •Часть 2. Вычислительные системы.

- •Лекция 23. Классификация систем параллельной обработки данных.

- •Сеть с топологией кольцо

- •Литература

- •Лекция 24. Классификация мультипроцессорных систем по способу организации основной памяти.

- •Лекция 25. Обзор архитектур многопроцессорных вычислительных систем.

- •Лекция 26. Направление развития в высокопроизводительных вычислительных системах.

- •Универсальные системы с фиксированной структурой

- •Направления развития микропроцессоров

- •Системы с фиксированной структурой из серийных микропроцессоров

- •Специализированные системы с фиксированной структурой

- •Специализированные системы с программируемой структурой

- •Технологическая база развития современных архитектур

- •Архитектуры многопотоковых процессоров

- •Кластер Green Destiny

- •Программируемый микропроцессор

- •Однородные вычислительные среды

- •Литература

- •Однокристальный ассоциативный процессор сам2000

- •Литература

- •Однокристальный векторно-конвейерный процессор sx-6

- •Литература

- •Лекция 27. Принципы построения телекоммуникационных вычислительных систем.

- •2.Компоненты телекоммуникационной системы

- •3. Типы телекоммуникационных сетей.

- •4. Топологии вычислительной сети.

- •5. Модем

- •Часть 3. Вычислительные сети.

- •Лекция 28. Эталонная модель взаимодействия открытых систем.

- •Лекция 29. Локальные вычислительные сети.

- •10Base-2 или тонкий Ethenet

- •10Base-5 или толстый Ethenet

- •2.2.2. Компоненты сети

- •2.2.3. Проводная сеть в умном доме(LexCom Home)

- •Лекция 30. Беспроводные сети на основе службы gprs.

- •Чем привлекательна эта технология?

- •Передача данных: gprs и gsm

- •Что дает абоненту технология gprs?

- •Принципы построения системы gprs

- •Терминальное оборудование gprs

- •Скорости передачи в системе gprs

- •Перспективы развития услуг на базе gprs

- •Перспективы пакетной передачи данных

- •Gprs модемы существуют в нескольких исполнениях:

- •Лекция 31. Беспроводные сети Radio-Ethernet.

- •Заключение

- •Лекция 32. Беспроводные локальные сети на основе Wi-Fi - технологии. Введение.

- •Архитектура, компоненты сети и стандарты

- •Организация сети

- •Физический уровень ieee 802.11

- •Канальный уровень ieee 802.11

- •Типы и разновидности соединений

- •2. Инфраструктурное соединение.

- •4. Клиентская точка.

- •5. Соединение мост.

- •Список использованной литературы:

Лекция 13. Программируемые таймеры и счетчики событий.

Довольно часто требуется устройство формирования временных интервалов для процессора и внешних устройств, подсчета внешних событий и ввода показаний в процессор, а также генерирования внешней синхронизации, которую может программировать процессор. Такое устройство называется программируемым интервальным таймером/счетчиком событий. Некоторыми областями применение такого устройства являются:

прерывание операционной системы с разделением времени через равномерные интервалы, чтобы она осуществляла переключение программ;

вывод точных временных сигналов с программируемыми периодами в устройство ввода-вывода (например, в аналого-цифровой преобразователь);

программируемая генерация скорости передачи в бодах;

измерение временной задержки между внешними событиями;

подсчет числа появлений событий во внешнем эксперименте и ввод показания в компьютер;

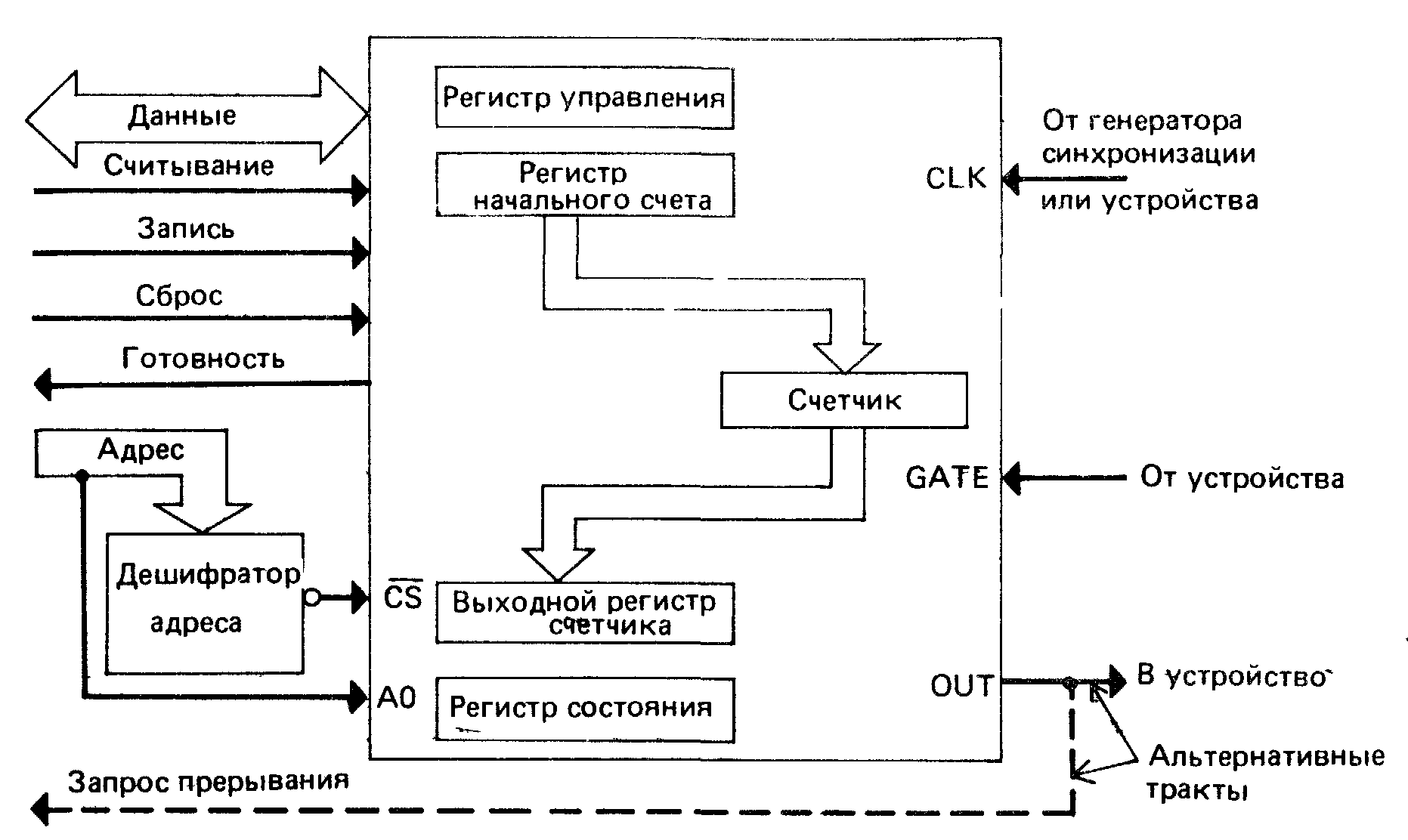

Рис. 9.25. Типичный интервальный таймер/счетчик событий

прерывание процессора после появления запрограммированного числа внешних событий.

Типичная организация интервального таймера/счетчика событий показана на рис. 9.25. Слева находятся четыре доступных компьютеру регистра: два верхних являются выходними портами, а два нижних - входными. Сам счетчик прямо процессору не доступен, но может инициализироваться из регистра начального счета и считывается посредством передачи его содержимого в выходной регистр счетчика. Счетчик запускается с начального значения и отсчитывает до 0. Вход CLK определяет скорость счета, сигнал GATE разрешает и запрещает вход CLK и, возможно, выполняет другие функции, а выход OUT-становится активным при достижении счетчиком 0 или, возможно, при подаче сиг-нала АТЕ. Выход OUT подключается к линии запроса прерывания в системной шине, поэтому прерывание возникает при достижении счетчиком 0; его же можно подключить к устройству ввода-вывода для инициирования необходимых действий.

Устройство вводит значение в регистр начального счета, передает его в счетчик и выполняет счет "назад" (т. е. вычитание) импульсами со входа CLK. Текущее содержимое счетчика в любой момент можно ввести в процессор, не нарушая работы счетчика, посредством передачи его в выходной регистр счетчика с последующим считыванием из этого регистра. При буферировании содержимого счетчика не требуется вводить его в процессор немедленно. Индикация нуля в счетчике обычно фиксируется на выходе OUT и в одном бите регистра состояния. Поэтому для обнаружения нуля допускается применять Программный ввод-вывод и ввод-вывод по прерываниям.

Регистр управления определяет режим работы и выполняет другие функции. Режим точно определяет, что происходит при достижении счетчиком 0 и (или) при подаче сигнала на вход GATE. Возможными действиями являются:

вход GATE применяется для разрешения и запрещения входа CLK;

вход GATE вызывает реинициализацию счетчика;

[ i. вход GATE прекращает счет и формирует высокий уровень на выходе OUT;

- при достижении 0 счетчик выдает сигнал OUT и останавливается;

при достижении 0 счетчик выдает сигнал OUT и автоматически реинициализируется из регистра начального счета.

Режимы могут также определяться комбинациями перечисленных возможностей. Рассмотрим, например, применение интервального таймера в операционной системе разделением времени. В этом случае на вход CLK подаются сигналы синхронизации, ) выход OUT подключается к линии запроса прерывания, возможно, немаскируемой прерывания. Вход GATE здесь не требуется. При включении системы в регистр начального счета загружается значение

начальный счет == частота синхронизации Х Т,

где Т - продолжительность каждого временного кванта в секундах. Задается такой режим, что при достижении счетчиком 0 содержимое регистра начального счета вновь загружается в счетчик, а выход OUT становится активным. Поскольку сигнал OUT используется как запрос прерывания, процедура прерывания для переключения программ будет выполняться с интервалом Т секунд.

9.3.1 Программируемый интервальный таймер

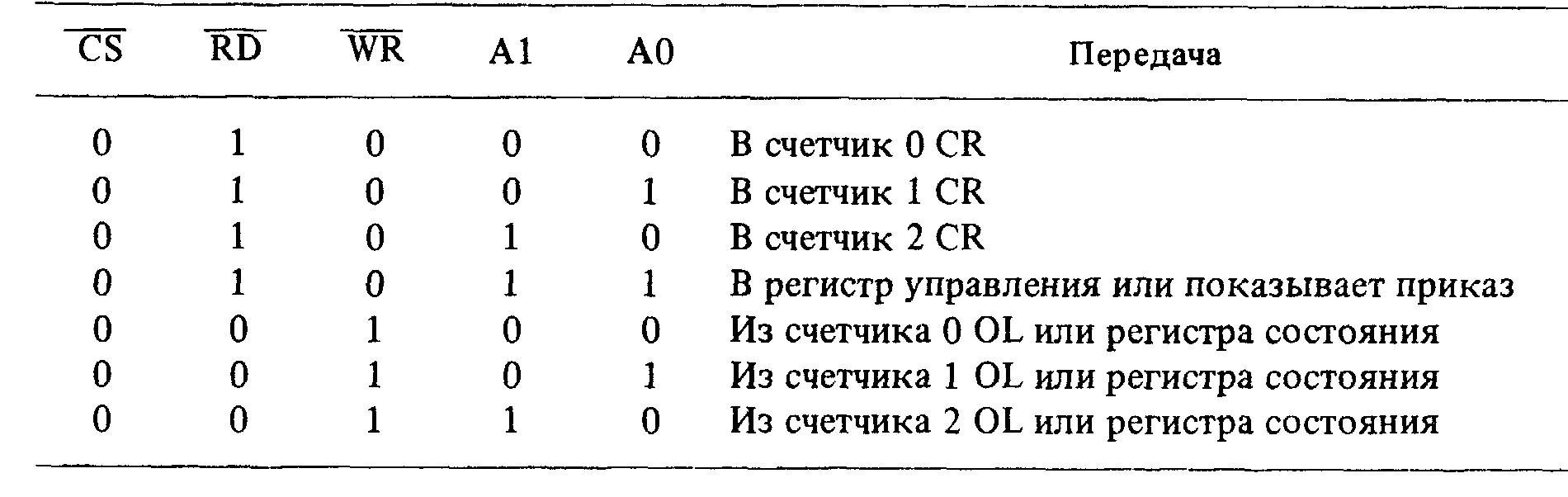

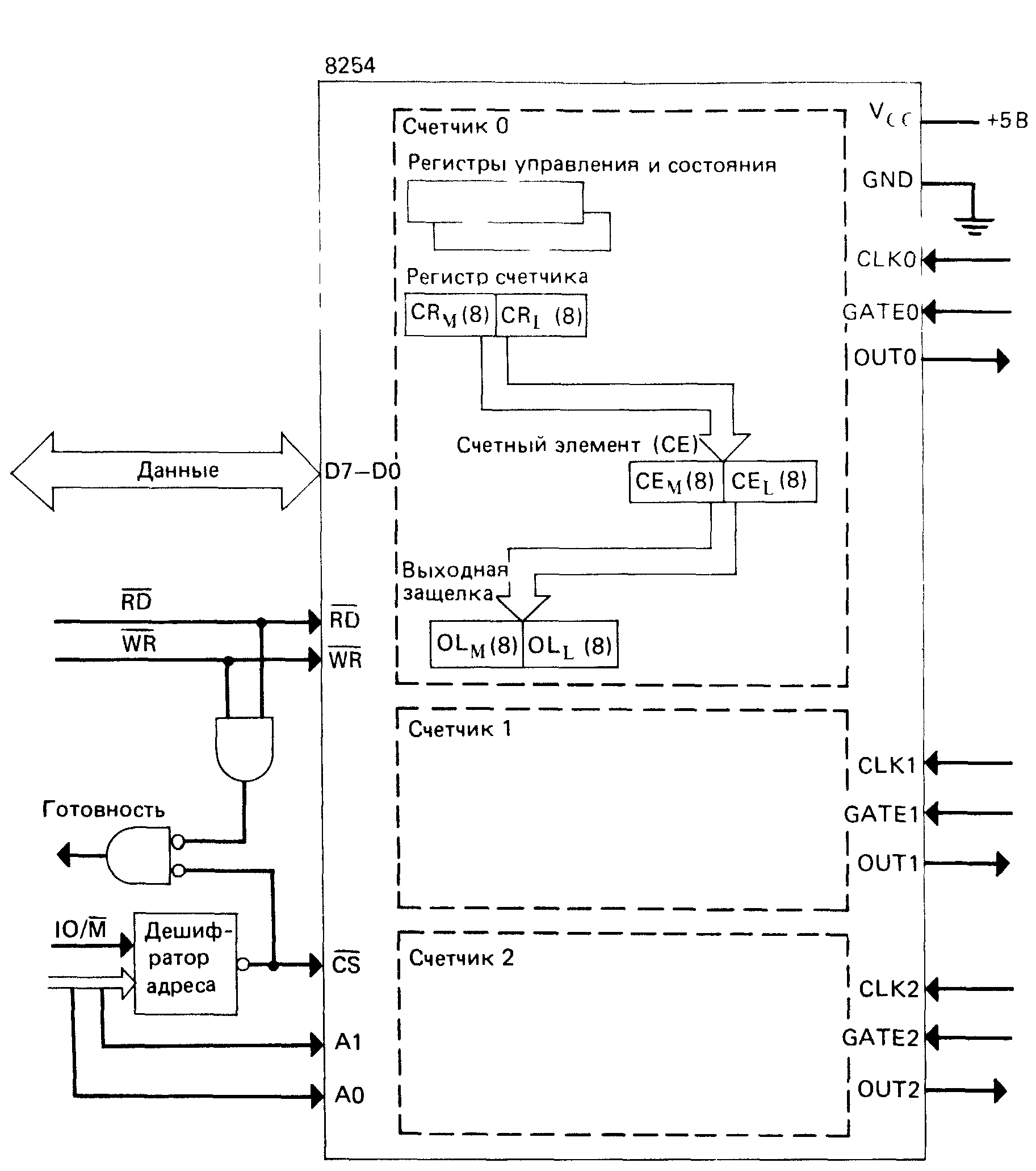

На рис. 9.26 представлена схема интервального таймера/счетчика событий 8254 фирмы Intel. В нем имеются три одинаковые счетные схемы со своими входами CLK и GATE и выходом OUT. Каждая схема имеет регистр управления и состояния, регистр счетчика (CR) для приема начального счета, счетного элемента (СЕ) , который выполняет счет, но непосредственно процессору недоступен, и выходного регистра-защелки (OL) для фиксации содержимого СЕ, так что его может считать процессор. Полагается, что CR, СЕ и OL представляют собой пары 8-битных регистров. (Реальные схемы несколько отличаются от приведенных, но для программиста рисунок абсолютно точен.)

Обращения к регистрам производятся в соответствии с табл. 9.3.

Таблица 9.3

Обращения к регистрам таймера/счетчика 8254

Все остальные комбинации приводят к тому, что линии данных переводятся в высокоимпедансное состояние. Когда А1 = АО = 1, выполнение записи в регистр управления или выдачи приказа зависит от старшего бита выводимого байта. В последних трех комбинациях считывание OL или регистра состояния определяет предыдущий приказ.

Имеются два вида приказов. Приказ фиксации счетчика заставляет соответствующий OL зафиксировать содержимое СЕ счетчика, определяемого двумя старшими битами приказа. Приказ обратного считывания фиксирует комбинацию СЕ или "готовит" комбинацию регистров состояния для считывания. Подготовка регистра состояния означает

Рис. 9.26. Схема таймера/счетчика 8254

его считывание, когда в следующей операции считывания осуществляется ввод из счетчика. Состояния 00, 01 и 10 двух старших бит показывают приказ фиксации счетчика, а состояние 11 - приказ обратного считывания. В приказе фиксации биты 5 и 4 должны быть нулевыми, а остальные биты не используются. Приказ обратного считывания имеет следующий формат:

![]()

Если бит COUNT = 0, фиксируются СЕ всех счетчиков, биты CNT которых содержат 1. если, например, CNTO = CNT2 = 1 и CNT1 = 0, то СЕ в счетчиках 0 и 2 фиксируются, "»в счетчике 1 не фиксируется. Аналогично STAT = 0 вызывает подготовку регистров

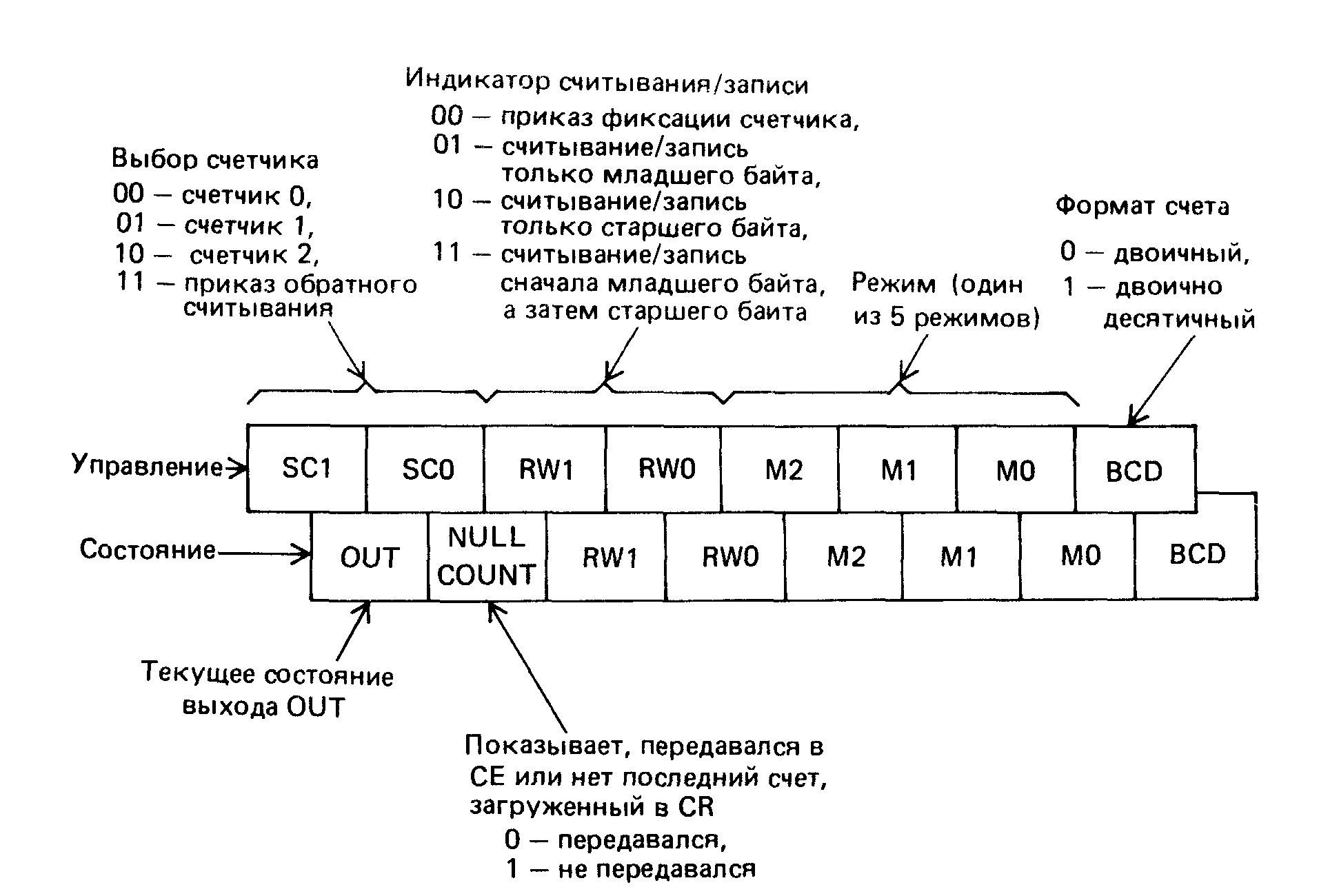

Рис 9 27 Регистры управления и состояния счетчиков

состояний счетчиков для ввода. Действия по фиксации и подготовке допускается указывать в одном приказе.

Форматы регистров управления и состояния показаны на рис. 9.27. Если два старших бита равны 1, они задают приказ обратного считывания; в противном случае они определяют счетчик. Если указан счетчик и биты 5-4 содержат нули, то имеет место приказ фиксации, который направляется в регистр управления выбираемого старшими битами счетчика. Когда же комбинация в битах 5-4 отличается от 00, она указывает тип ввода из OL или вывода в CR. Комбинация 01 идентифицирует операции считывания/записи из (в) OL^/CR, комбинация 10 - из (в) OLix/CRv» и комбинация 11 - выполнение операций парами (первый байт из (в) OLi /CRi и второй из (в) OLn/CR^i) Запись одного байта в CR вызывает сброс другого байта Биты 1, 2 и 3 определяют режим, а бит 0 определяет формат счета.

Таймер/счетчик имеет следующие режимы работы (через N обозначен начальный счет)

Режим 0 (прерывания по концу счета) . Сигнал GATE = 1 разрешает счет, a GATE = О запрещает счет, причем GATE не влияет на выход OUT. Содержимое CR передается в СЕ по первому импульсу CLK после того, как процессор осуществил запись в CR, независимо от сигнала на входе GATE Импульс, который загружает СЕ, не учитывается при счете На выходе OUT формируется низкий уровень при записи в регистр управления, который сохраняется до достижения счетчиком 0. Режим 0 предназначен в основном для счета событий.

Режим 1 (аппаратно перезапускаемый одновибратор). После загрузки значения N в CR переход 0 -* 1 на входе GATE вызывает загрузку СЕ, переход 1 -»0 на выходе OUT и запускает счет. Когда счетчик достигает 0, на выходе OUT формируется высокий уровень; таким образом, результатом является отрицательный импульс на выходе OUT с продолжительностью N периодов синхронизации

Режим 2 (гчрч' v-и^й nil ерьиышй таймер) После загрузки значения N в CR следующий импульс синхронизации осуществляет передачу из CR в СЕ. На выходе OUT возникает переход 1 -^ 0. когда счетчик достигает 0 низкий уровень сохраняется в течение одною импульса CJ-K Згпсм на выходе OUT. появляется высокий уровень, производится повторная загрузка СЕ из CR, в результате на выходе 01Л появляется отрицательный импульс через N тактов синхронизации Сигнал GAU --- 1 разрешает счет, а GATi U запрещаег Переход 0 " 1 на входе GAJ 1 вызывает реинициализацию счета следующим импульсом синхронизации. Данный pt-л.л vi применяется для реализации периодического интервального таймера

Режим 3 (генератор прямоугольного сигнала). Аналогичен режиму 2, но на выходе От формируется низкий уровень при достижении половины начального счета; этот уровень сохраняется до достижения счетчиком 0. Как и прежде, сигнал GATE разрешает и запрещает счет, а его переход 0 -* 1 реинициализирует счет Этот режим применяется в генераторах, определяющих скорость передачи в бодах.

Режим 4 (программно-запускаемый строб) . Аналогичен режиму 0, но на выходе OUT в процессе счета действую высокий уровень, а при достижении счетчиком 0 появляется отрицательный импульс с продолжительностью в один такт синхронизации

Режим 5 (аппаратно-запускаемый строб с перезапуском) После загрузки CR переход 0 ^ 1 на входе GATF вызывает передачу из CR в СЕ следующим импульсом CLK. В процессе счета на выходе OUT действует высокий уровень, а при достижении счетчиком 0 формируется отрицательный импульс с продолжительностью в один период CLK Сигнал GATE может в любой момент времени реинициализировать счет.

Начальное значение счета 0 во всех режимах интерпретируется как 216 или Ю4 в зависимости от формата счета. Мы привели общие принципы работы микросхемы 8254, а подробное описание содержится в фирменных материалах.