- •Курс лекций «Вычислительные машины, системы и сети»

- •Часть 1. Вычислительные машины. 3

- •Часть 2. Вычислительные системы. 203

- •Часть 3. Вычислительные сети. 254

- •Часть 1. Вычислительные машины.

- •Лекция 1. Структура вычислительной машины.

- •1.1 Общее устройство

- •1.2 Корпус pc

- •1.3 Материнская плата

- •1.4 Процессор

- •1.5 Устройства хранения данных

- •Лекция 2. Эволюция микрокомпьютеров.

- •1.1.Основные направления эволюции микрокомпьютеров.

- •Лекция 3. Машинная организация процессора 80286

- •1.1. Введение.

- •2.2. Структура памяти.

- •2.3. Сегментация памяти.

- •2.4. Структура ввода-вывода.

- •2.5. Регистры.

- •Лекция 4. Операнды и режимы адресации операндов.

- •Лекция 5. Общая организация памяти.

- •Лекция 6. Прерывание микропроцессора в эвм.

- •Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •Обработка прерываний в персональной эвм

- •Лекция 7. Последовательный интерфейс rs–232c.

- •Общие сведения о интерфейсе rs–232c

- •Виды сигналов

- •Тестовое оборудование для интерфейса rs–232c

- •Лекция 8. Последовательный интерфейс сом-порт.

- •Использование сом-портов

- •Функции bios для сом-портов

- •Лекция 9. Программируемый связной интерфейс.

- •Лекция 10. Передача данных между эвм с помощью модемов. Типы и характеристики модемов.Набор ат-команд.

- •Лекция 11. Программируемый периферийный интерфейс.

- •Лекция 12. Параллельный интерфейс:lpt-порт.

- •Интерфейс Centronics

- •Сигналы интерфейса Centronics

- •Традиционный lpt-порт

- •Функции bios для lpt-порта

- •Расширения параллельного порта

- •Физический и электрический интерфейс

- •Режимы передачи данных

- •Полубайтный режим ввода — Nibble Mode

- •Конфигурирование lpt-портов

- •Использование параллельных портов

- •Неисправности и тестирование параллельных портов

- •Лекция 13. Программируемые таймеры и счетчики событий.

- •Лекция 14. Универсальная последовательная шина usb.

- •2.Шина usb.Общая характеристика.

- •Структура usb

- •3.Физический интерфейс

- •Протокол

- •Устройства usb - функции и хабы

- •Хост-контроллер

- •Лекция 15. Протокол работы usb-шины.

- •Описание протоколов используемых при передаче данных Структура usb пакета

- •Поля usb пакета

- •Типы usb пакетов

- •Приоритеты передач по usb-шине

- •Источники информации

- •Лекция 16. Интерфейс ieee-1394 (FireWire).

- •Технические характеристики

- •Топология шины

- •Пример топологии ieee-1394

- •Совместимость

- •Кабели и разъемы

- •Список литературы

- •Лекция 17. Организация прямого доступа к памяти.

- •Лекция 18. Устройства ввода эвм. Клавиатура. Введение

- •1. Основные части клавиатуры

- •1.1. Клавиши пишущей машинки (алфавитно-цифровая клавиатура)

- •Режимы ввода символов

- •Названия специальных знаков

- •1.2. Служебные клавиши

- •Индикаторы режимов

- •Клавиши управления курсором

- •1.3. Функциональные клавиши

- •1.4. Малая цифровая клавиатура

- •2. Принципы работы клавиатуры

- •Лекция 19. Интерфейс эвм с видеотерминалом. Видеоадаптер. Режимы изображений: текстовый и графический режимы. Видеопамять. Анимация изображений. Интерфейс эвм с видеотерминалом.

- •Видеоадаптер.

- •Лекция 20. Накопитель магнитных дисков: гибкий и жесткий. Структура дисков: дорожки, сектора, блоки. Обмен информации между эвм и магнитными дисками.

- •Лекция 21. Сканер. Считывание изображения. Типы обрабатываемых изображений. Качество изображения.

- •Лекция 22. Назначение и функции операционной системы.

- •Часть 2. Вычислительные системы.

- •Лекция 23. Классификация систем параллельной обработки данных.

- •Сеть с топологией кольцо

- •Литература

- •Лекция 24. Классификация мультипроцессорных систем по способу организации основной памяти.

- •Лекция 25. Обзор архитектур многопроцессорных вычислительных систем.

- •Лекция 26. Направление развития в высокопроизводительных вычислительных системах.

- •Универсальные системы с фиксированной структурой

- •Направления развития микропроцессоров

- •Системы с фиксированной структурой из серийных микропроцессоров

- •Специализированные системы с фиксированной структурой

- •Специализированные системы с программируемой структурой

- •Технологическая база развития современных архитектур

- •Архитектуры многопотоковых процессоров

- •Кластер Green Destiny

- •Программируемый микропроцессор

- •Однородные вычислительные среды

- •Литература

- •Однокристальный ассоциативный процессор сам2000

- •Литература

- •Однокристальный векторно-конвейерный процессор sx-6

- •Литература

- •Лекция 27. Принципы построения телекоммуникационных вычислительных систем.

- •2.Компоненты телекоммуникационной системы

- •3. Типы телекоммуникационных сетей.

- •4. Топологии вычислительной сети.

- •5. Модем

- •Часть 3. Вычислительные сети.

- •Лекция 28. Эталонная модель взаимодействия открытых систем.

- •Лекция 29. Локальные вычислительные сети.

- •10Base-2 или тонкий Ethenet

- •10Base-5 или толстый Ethenet

- •2.2.2. Компоненты сети

- •2.2.3. Проводная сеть в умном доме(LexCom Home)

- •Лекция 30. Беспроводные сети на основе службы gprs.

- •Чем привлекательна эта технология?

- •Передача данных: gprs и gsm

- •Что дает абоненту технология gprs?

- •Принципы построения системы gprs

- •Терминальное оборудование gprs

- •Скорости передачи в системе gprs

- •Перспективы развития услуг на базе gprs

- •Перспективы пакетной передачи данных

- •Gprs модемы существуют в нескольких исполнениях:

- •Лекция 31. Беспроводные сети Radio-Ethernet.

- •Заключение

- •Лекция 32. Беспроводные локальные сети на основе Wi-Fi - технологии. Введение.

- •Архитектура, компоненты сети и стандарты

- •Организация сети

- •Физический уровень ieee 802.11

- •Канальный уровень ieee 802.11

- •Типы и разновидности соединений

- •2. Инфраструктурное соединение.

- •4. Клиентская точка.

- •5. Соединение мост.

- •Список использованной литературы:

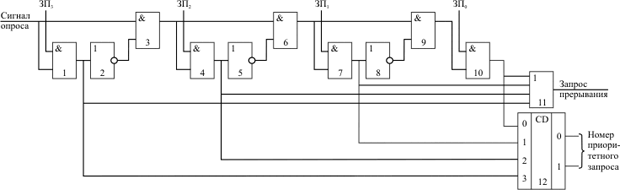

Цепочечная однотактная система определения приоритета запроса прерывания

На рис. 3 приведена схема, обеспечивающая получение номера наиболее приоритетного запроса прерывания из присутствующих в компьютере на момент подачи сигнала опроса ("дейзи-цепочка")

Данная схема используется для анализа запросов аппаратных прерываний. Приоритет запросов прерываний (ЗПi) уменьшается с уменьшением номера запроса. В тот момент, когда компьютер должен определить наличие и приоритет внешнего аппаратного прерывания (обычно после окончания выполнения каждой команды), процессор выдает сигнал опроса. Если на входе ЗП3присутствует сигнал высокого уровня (есть запрос), то на элементе 11 формируется общий сигнал наличия запроса прерывания и дальнейшее прохождение сигнала опроса блокируется. Если ЗП3=0, то анализируется сигнал ЗП2и так далее. На шифраторе (элемент 12) формируется номер поступившего запроса прерывания.

Этот номер передается в процессор лишь при наличии общего сигнала запроса прерывания.

Такая структура позволяет быстро анализировать наличие сигнала запроса прерывания и определять наиболее приоритетный запрос из нескольких присутствующих в данный момент. Распределение приоритетов запросов прерываний внешних устройств осуществляется путем их физической коммутации по отношению к процессору. Указание приоритетов - жесткое и не может быть программно изменено. Изменение приоритетов возможно только путем физической перекоммутации устройств.

Рис. 3. Схема определения номера наиболее приоритетного запроса прерывания

Обработка прерываний в персональной эвм

Микропроцессоры типа х86 имеют два входа запросов внешних аппаратных прерываний:

NMI - немаскируемое прерывание, используется обычно для запросов прерываний по нарушению питания;

INT - маскируемое прерывание, запрос от которого можно программным образом замаскировать путем сброса флага IF в регистре флагов.

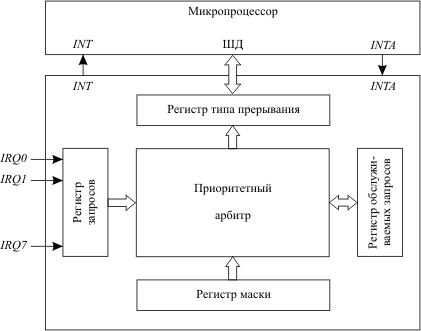

Рис. 4. Структура контроллера приоритетных прерываний

Единственный вход запроса маскируемых прерываний микропроцессора не позволяет подключить к нему напрямую сигналы запросов от большого числа различных внешних устройств, которые входят в состав современного компьютера: таймера, клавиатуры, "мыши", принтера, сетевой карты и т.д. Для их подключения к одному входу INT микропроцессора используется контроллер приоритетных прерываний (рис. 4). Его функции:

восприятие и фиксация запросов прерываний от внешних устройств;

определение незамаскированных запросов среди поступивших запросов;

проведение арбитража: выделение наиболее приоритетного запроса из незамаскированных запросов в соответствии с установленным механизмом назначения приоритетов;

сравнение приоритета выделенного запроса с приоритетом запроса, который в данный момент может обрабатываться в микропроцессоре, формирование сигнала запроса на вход INT микропроцессора в случае, если приоритет нового запроса выше;

передача в микропроцессор по шине данных типа прерывания, выбранного в процессе арбитража, для запуска соответствующей программы - обработчика прерывания; это действие выполняется по сигналу разрешения прерывания INTA от микропроцессора, который выдается в случае, если прерывания в регистре флагов микропроцессора не замаскированы (IF=1).

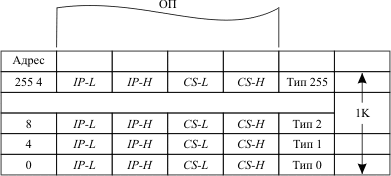

Переход к соответствующему обработчику прерывания осуществляется (в реальном режиме работы микропроцессора) посредством таблицы векторов прерываний. Эта таблица (рис. 5) располагается в самых младших адресах оперативной памяти, имеет объем 1 Кбайт и содержит значения сегментного регистра команд (CS) и указателя команд (IP) для 256 обработчиков прерываний.

Рис. 5. Структура таблицы векторов прерываний

Обращение к элементам таблицы осуществляется по 8-разрядному коду - типу

прерывания (таблица 1)

|

Таблица 14.1. | |

|

Тип прерывания |

Источник прерывания |

|

0 |

Деление на 0 |

|

1 |

Пошаговый режим выполнения программы |

|

2 |

Запрос по входу NMI |

|

· · · | |

|

8 |

Запрос по входу IRQ0 (системный таймер) |

|

9 |

Запрос по входу IRQ1 (контроллер клавиатуры) |

|

· · · | |

|

11 |

Отсутствие сегмента в оперативной памяти |

|

· · · | |

|

255 |

Пользовательское прерывание |

Различные источники задают тип прерывания по-разному:

программные прерывания вводят его изнутри процессора или содержат его в номере команды INT n;

аппаратные маскируемые прерывания вводят его от контроллера приоритетных прерываний по шине данных;

немаскируемому аппаратному прерыванию назначен тип 2.