- •Лекция 4. Дискретные устройства. Синхронизаторы, триггеры, регистры, счетчики

- •остранение сигналов. Быстродействие. Понятие о задер

- •остранение сигналов. Быстродействие. Понятие о задер

- •остранение сигналов. Быстродействие. Понятие о задер

- •остранение сигналов. Быстродействие. Понятие о задер

- •пространение сигналов. Быстродействие. нятие о задержке. Критические цепи

- •пространение сигналов. Быстродействие. нятие о задержке. Критические цепи.

- •пространение сигналов. Быстродействие. нятие о задержке. Критические цепи.

- •тические цепи. Критической является цепь с самой шой задержкой, например:

- •облемы, требующие синхронизации:

- •азовый принцип синхронизации:

- •амическая дисциплина:

- •табильность ронт сигнала тактовой частоты немного растянут во

- •Метастабильность

- •Простой синхронизатор и временная диаграмма его

- •Вероятность сбоя синхронизатора

- •етные устройства- триггеры етное (последовательное) цифровое устройство:

- •етные устройства- триггеры етное (последовательное) цифровое устройство:

- •риггер

- •триггер

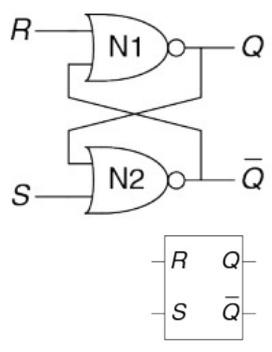

- •R-S триггер, УГО и таблица истинности

- •D триггер с синхронизацией по уровню

- •D триггер с синхронизацией по уровню

- •триггер работающий по фронту

- •триггер работающий по фронту ругой вариант реализации

- •D триггер работающий по фронту, VHDL описание и временная диаграмма

- •D триггер со сбросом

- •D триггер со сбросом и установкой

- •D триггер со сбросом, установкой и разрешением (вход CE-разрешение на запись)

- •Счетный триггер

- •JK- триггер.

- •JK- триггер.

- •Сдвиговый регистр

- •Сдвиговый регистр

- •Сдвиговый регистр с параллельной загрузкой

- •Сдвиговый регистр с параллельной загрузкой

- •Cчетчик

- •Cчетчик с промежуточным сбросом (из какого состояния?)

- •Cчетчик с пропуском состояний и внешней установкой в «0111»

- •Счетчик: Пример поведенческого описания и

- •Счетчик: Пример поведенческого описания схема-

- •Счетчик: поведенческое описание, переведенное САПР на элементы ПЛИС (фрагмент)

- •Реверсивный счетчик: пример поведенческого

- •Благодарю за внимание!

триггер

чай III: R=1, S=1

рещенная комбинация входных воздействий. на входе N1, так и на входе N2 как минимум одной единице (R и S), поэтому на выходе дой защелки – логический 0.

довательно, Q=0 и Q¯ =0.

21

чай IV: R=0, S=0

вход N1 поступает 0 и Q¯ . Так как мы еще не ем значения Q¯, мы не можем определить чение на выходе элемента N1.

вход N2 поступает 0 и Q. Так как мы еще не ем значения Q, мы не можем определить чение на выходе элемента N2.

т случай аналогичен случаю с двумя перекрестно юченными инверторами. Мы знаем, что Q должен ь равен либо 0, либо 1.

смотрим каждый из этих двух случаев.

22

чай IVa: Q=0

как S и Q равны 0, то на выходе N2 будет ческая 1, Q¯ =1. Теперь на входе N1

одна единица – Q¯, поэтому на его выходе Q=0. чай IVb: Q=1

как Q = 1, то на выходе N2 будет 0, Q¯ =0. ерь на обоих входах N1 нули (R и Q¯ ),

ому на его выходе логическая 1, Q=1. ойство остается в предыдущем состоянии.

23

R-S триггер, УГО и таблица истинности

ггер- бистабильный элементом с одним битом состояни щимся в Q.

нием можно управлять при помощи входов R и S.

на R поступает высокий уровень, выход сбрасывается в высокий уровень приходит на S, выход устанавливается и на один вход не пришла логическая единица, триггер яет свое предыдущее состояние, значение выходов еняется. 24

D триггер с синхронизацией по уровню

Сигнал D записывается в R-S триггер по разрешению от сигнала CLK

25

D триггер с синхронизацией по уровню

Сигнал D записывается в R-S триггер по разрешению от сигнала CLK

26

триггер работающий по фронту

ух D триггеров, работающих по уровню, можно

оить D триггер, работающий по фронту тактового сигна енное устройство будет переключаться по фронту тания сигнала.

27

триггер работающий по фронту ругой вариант реализации

28

D триггер работающий по фронту, VHDL описание и временная диаграмма

Process (clk) Begin

if (clk='0' and c'event) then

q<=d; End if;

End process;

29

D триггер со сбросом

В триггере с функцией сброса добавляется вход RESET (сброс). Когда на RESET подан 0, триггер ведет себя как обычный D-триггер.

Когда на RESET подана 1, такой триггер игнорирует вход D и сбрасывает выход в 0.

process (clk) begin |

|

if (clk'event and clk = '1') |

|

then |

|

if (reset = '1') then |

|

q <= '0'; |

|

else q <= data; |

|

end if; |

|

end if; |

|

end process; |

30 |