смехотехника

.docТранзистор в качестве элемента схемы. При обсуждении базовых логических схем И, ИЛИ, И-НЕ, ИЛИ-НЕ и инвертора для объяснения мы использовали логических функций механические переключатели. В цифровой технике в качестве активных элементов схем применяются только транзисторы, тиристоры и симисторы. Последние два элемента используются в основном для переключения постоянного и переменного токов в сильноточных цепях для привода моторов, управления работой нагревательных приборов и других мощных устройств для обработки данных. Эти элементы являются бесконтактными переключателями, которые имеют гораздо большие надежность и срок годности, чем механические переключатели, к которым мы относим также и реле. Кроме того, транзисторы, тиристоры и симисторы являются усилителями, т. е. они могут переключать относительно большие токи при небольших затратах энергии на управление. Из цифровых транзисторных схем легко компоновать более сложные логические схемы, и получаемые в результате ИС могут содержать от нескольких десятков до нескольких десятков тысяч транзисторов на одной кремниевой пластинке (чипе) площадью в несколько квадратных миллиметров. В этих случаях говорят о цифровых схемах типа МИС (малые ИС), СИС (средние ИС), БИС (большие ИС) и СБИС (сверхбольшие ИС). Примером СБИС является современный микропроцессор (МП), состоящий из миллионов транзисторов на одном кристалле. По сравнению с механическим переключателем транзистор имеет тот недостаток, что в короткозамкнутом (открытом) состоянии сопротивление между его выводами не равно нулю, а в разомкнутом (запертом) состоянии через него протекает небольшой ток утечки. Биполярный транзистор применяется в качестве переключающего элемента в схеме с общим эмиттером (рис. 1).

Рисунок 1. Биполярный транзистор в схеме с общим эмиттером в качестве бесконтактного переключателя (а) и его механический эквивалент (б)

Если нижний вывод резистора нагрузки RН заземлен через небольшое сопротивление, через него протекает максимальный ток. Это соответствует случаю, когда транзистор работает в режиме насыщения. При этом предполагается, что разность потенциалов между коллектором и эмиттером UKЭ становится меньше разности потенциалов между базой и эмиттером UБЭ (в кремниевых эпитаксиальных транзисторах UKЭ <100 мВ). Для работы в режиме насыщения требуется обеспечить ток базы, равный Iк макс / а'мин, где а'мин, или hэ мин, - минимальный коэффициент усиления по току, который можно ожидать для переключающих транзисторов данного типа. При запирании транзистора через резистор нагрузки Rн течет минимальный ток. Это имеет место при UKЭ<0,5В. В короткозамкнутом состоянии ток через нагрузку равен UB / RН а в разомкнутом состоянии ток и падение напряжения на нагрузке равны нулю. Напряжение же между выводами переключателя равно UB В режиме насыщения максимальный ток, равный UB/RS, не достигается. На транзисторе происходит небольшое падение напряжения, которое называется напряжением насыщения UКЭ (нас). В разомкнутом состоянии ток не равен нулю и через транзистор протекает небольшой ток утечки. Если в цифровых схемах используются полевые транзисторы, то высокое "прямое" сопротивление в статическом режиме не создает особых проблем, потому что при управлении полевым транзистором в отличие от биполярного практически не потребляется мощность (рис. 2).

Рисунок 2. Полевой транзистор в качестве переключающего элемента (а) и его механический эквивалент (б).

Это дает возможность применять высокоомные схемы, которые, однако, обеспечивают меньшую скорость переключения по сравнению с биполярным транзистором. Причина заключается в том, что собственные емкости полевого транзистора и емкости соединительных элементов замедляют процесс изменения напряжений и токов в соответствующих переключающих схемах. Таким образом, при рассмотрении обоих типов транзисторов мы исходим из того, что переключающий элемент должен включаться и выключаться в точности так, как механический переключатель. С этой же целью мы можем использовать и другой критерий, например два уровня напряжения, которые соответствуют двум состояниям транзисторного переключателя. Один уровень напряжения будет соответствовать "замыканию", а другой - "размыканию". Такой подход обеспечивает определенные преимущества в отношении скорости переключения, потому что при переключении режим насыщения можно исключить. В результате логические схемы можно разделить на две большие группы:

-

а) схемы, в которых транзистор управляется в режиме насыщения (насыщенные логические схемы);

-

б) схемы, в которых транзистор управляется в ненасыщенном режиме (ненасыщенные логические схемы).

Логические схемы из первой группы, как уже сказано, являются более медленными, так как при работе в режиме насыщения на транзистор оказывает воздействие эффект накопления заряда. Быстродействие таких схем можно увеличить, применяя в них транзисторы с высокой граничной частотой. Одним из достоинств насыщенных логических схем при низкой частоте переключения является малое рассеяние мощности в транзисторе в режиме переключения. В запертом состоянии через транзистор протекает малый ток и рассеяние мощности близко к нулю. То же наблюдается и в открытом состоянии, так как напряжение насыщения эпитаксиального транзистора настолько мало, что его произведение на ток через коллектор оказывается незначительным. Другим достоинством этих схем является более низкая чувствительность к помехам. К ненасыщенным логическим схемам относится ЭСЛ - семейство. Ниже рассматриваются наиболее часто используемые семейства практических логических схем.

Содержание.

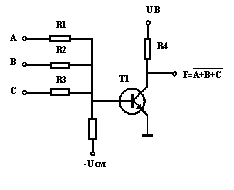

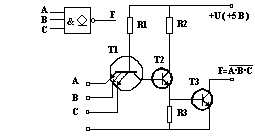

Резисторно-транзисторная логика (РТЛ). На начальной стадии развития техники цифровых ИС прежде всего использовались схемы, которые легко можно было реализовать и свойства которых уже были известны (на основе аналогии с обычными схемами, собранными из дискретных компонентов). Простейшими из этих схем являются схемы резисторно-транзисторной логики (РТЛ), которые под разными названиями выпускались несколькими фирмами. На рис. 3 показана базовая РТЛ-схема, в которой транзистор находится в режиме насыщения, если на одном или нескольких входах имеется напряжение высокого уровня (H). При этом выходное напряжение схемы равно 0 В (L). Таким образом, в рамках положительной логики эта РТЛ-схема является схемой ИЛИ-НЕ с функцией F=A+B+C. Выходное напряжение схемы имеет высокий уровень (H), если все три входных напряжения равны нулю (L).

|

|

Рисунок 3. Базовая РТЛ-схема с таблицей истинности. В таблице применяются обозначения МЭК для уровней напряжения.

В режиме с низким уровнем на входе (О В, отрицательная логика), схема ведет себя как схема И-НЕ с функцией F=A•B•C.

Содержание.

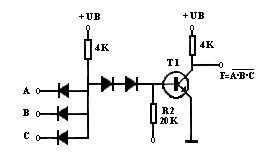

Диодная логика (ДЛ) и диодно-транзисторная логика (ДТЛ) с дискретными компонентами. На рис. 4 приведены две схемы, в которых логические функции реализуются с помощью полупроводниковых диодов. В схеме, показанной на рис. 4 а, выходное напряжение поло-жительно, если положительны А или В или С. Выходное напряжение отрицательно, если отрицательны А и В и С. Таким образом, эта схема ведет себя как схема ИЛИ при положительных и как схема И при отрицательных входных сигналах. В диодной схеме, показанной на рис. 4. б, наоборот, реализуется функция ИЛИ для отрицательных входных сигналов и функция И для положительных.

Рисунок 4. Диодная логика.

Выходной сигнал диодных схем можно использовать для управления другими логическими диодными схемами. За счет неизбежных потерь уровни напряжения для различных состояний рассматриваемых схем сближаются между собой. По истечении некоторого времени высокий уровень (H) нельзя будет отличить от низкого уровня (L). В логических схемах, где требуется высокая надежность, за диодным вентилем обычно включают транзистор, который фиксирует уровень логического напряжения. Подобные логические схемы обозначаются как ДТЛ-схемы На рис. 5 приведена ДТЛ - схема, которая в течение ряда лет использовалась в качестве стандартной. Эта схема является схемой И-НЕ для единиц (Н) при положительной логике и ИЛИ-НЕ для нулей (L). Комбинация И-ИЛИ при положительной логике получается путем соединения ДТЛ - элементов В случае схемы И-НЕ (рис. 5) выходное напряжение равно 0 В (L), если все входные напряжения положительны (H). При этом входные диоды запираются и транзистор управляется через входной резистор с сопротивлением 4 кОм. Выходное напряжение этой схемы имеет высокий уровень (Н), если на один или несколько входов подается напряжение низкого уровня (L).

|

|

Рисунок 5. Базовая схема ДТЛ с таблицей истинности (уровни по системе МЭК).

Содержание.

Транзисторно-транзисторная логика (ТТЛ). Совершенно новое направление, которое возникло в ходе эволюции ИС, применяемых в цифровой электронике, связано с ТТЛ-семейством. Оно состоит из логических схем, быстрое развитие которых связано с их более высоким быстродействием по сравнению с РТЛ-и ДТЛ-схемами и, кроме того, с более простой технологией изготовления. Последнее обстоятельство имеет важное значение с точки зрения затрат и организации производства. Хорошие характеристики ТТЛ-схем и существенное снижение их стоимости в последние годы привели к тому, что в настоящее время это семейство нашло широкое распространение.

Содержание.

Серия 7400. Серия 7400 разработана фирмой Texas Instruments, которая выполнила много новаторских разработок в области логических схем. В настоящее время эта серия производится другими фирмами, в том числе и европейскими, такими, как фирма Siemens, которая выпускает ее как серию FL. Серия 7400 является теперь стандартным разделом каталогов многих фирм. С течением времени в рамках этой серии возникли и другие варианты, такие, как серия 74Н и серия 74L, которые состоят из быстродействующих и маломощных ТТЛ-схем соответственно. Разработкой последних лет является маломощное ТТЛ-семейство логических схем с диодами Шоттки(ТТЛШ), характеристики которых аналогичны характеристикам ТТЛ-схем при более низкой (в 5 раз) потребляемой мощности. Серия 7400 (серия FL) состоит из ТТЛ-схем, которые работают с напряжением питания +5 В и применяются в температурном диапазоне 0-70 °С. Логический низкий уровень равен 0,2 В, а логический высокий уровень составляет 3,3 В. Помехоустойчивость в среднем превышает 1 В. Для применения в экстремальных условиях ряд фирм производит серию 5400 с теми же характеристиками, что и у схем серии 7400. Эти характеристики, однако, гарантированы для серии 5400 при изменении температуры окружающей среды от -55 до +125°С.

Содержание.

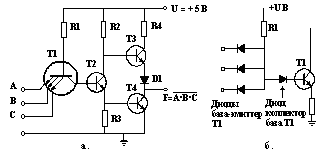

Базовая ТТЛ-схема. На рис. 6 приведена базовая схема из серии 7400. Входным элементом является многоэмиттерный транзистор, который на первый взгляд усложняет ТТЛ - схему, однако если представить эмиттеры с общей базой в виде нескольких диодов и переход коллектор - база в виде диода, то схема становится более удобной и простой для понимания (рис. 6, б). Отсюда сразу же видна взаимосвязь между ТТЛ- и ДТЛ - схемами.

|

|

Рисунок 6. ТТЛ-схема И-НЕ с каскадным выходом. а - схема И-НЕ с многоэмиттерным входом; б - диодный эквивалент входной цепи .

Если эмиттерные входы связаны с логическими выходами (предшествующих схем), которые обеспечивают высокий уровень (т. е. напряжение 3,3 В и выше), то диоды база - эмиттер окажутся запертыми и транзистор T2 будет управляться через R1. За счет контактной разности потенциалов на диодных переходах база - эмиттер транзисторов T2 и T4 и база - коллектор транзистора T1, база T1 будет находиться под напряжением 2,2 В по отношению к земле. При напряжении на эмиттерах 3,3 В и выше происходит запирание диодов база - эмиттер транзистора T1. При этом транзистор Т2 управляется через диод база-коллектор T1 и R1. Транзистор Т2 управляется в насыщенном режиме. В результате T4 также управляется по базе, а T3 запирается. Выходное напряжение этой ТТЛ-схемы при полностью проводящем T4 и запертом T3 составляет -0,2 В, и этот уровень мы определяем как логический низкий уровень. Итак, когда на все входы подано напряжение высокого уровня (А, В и С находятся под напряжением +3,3 В и выше), на выходе схемы появится напряжение низкого уровня. И наоборот, если мы соединим один из входов, например А, с L-выходом какой-то другой схемы (напряжение 0,2В), то диод база - эмиттер на входе А станет проводящим. Так как при этом база T1 находится под напряжением 2,2В, а эмиттер -под напряжением 0,2 В, то соответствующий входной диод включится в прямом направлении. Входное напряжение понизит напряжение на базе T1 до уровня ~ 0,9 В, т. е. T2 и T4 станут неуправляемыми. Оба транзистора запираются, и напряжение на коллекторе T2 повышается. Транзистор T3 становится проводящим, и выходное напряжение повышается до ~ 3,3В. Таким образом, на выходе этой ТТЛ-схемы появляется напряжение высокого уровня. То же происходит и с другими эмиттерными входами. Итак, если на один или несколько входов одновременно подается напряжение низкого уровня, на выходе схемы появляется напряжение высокого уровня. Таким образом, эта схема оказывается схемой И-НЕ для высоких уровней и ИЛИ-НЕ -для низких уровней. Таблица истинности для этой схемы нам уже известна. Преимущество применения многоэмиттерного входа по сравнению с однодиодным входом (как в случае ДТЛ-схем) заключается в том, что в случае входных сигналов низкого уровня входной элемент работает как транзистор. Напряжение на коллекторе транзистора T1 в момент подачи сигнала на вход приблизительно равно 2,2В, а напряжение на эмиттере - около +0,2 В относительно земли. Его база, связанная через R1 с UB, в нормальном режиме имеет положительный потенциал по отношению к эмиттеру. Заряд, возникающий при этом из-за эффекта накопления в базе транзистора T2, быстро рассасывается через транзистор T1, что существенно влияет на скорость переключения всей ТТЛ-схемы в целом. Оконечный элемент этой схемы, работающий в двухтактном режиме, называется в специальной литературе каскадным выходом. Достоинство его применения заключается в том, что рассматриваемая схема быстро переключается как на низкий, так и на высокий уровень. Сигналы каскадного выхода имеют хорошие передние и задние фронты (т. е. короткие времена нарастания и спада выходного сигнала). Его недостатком является то, что при реализации функции ИЛИ выходы этой схемы не удается переключать одновременно. Приходится снова применять функцию МОНТАЖНОЕ ИЛИ. Для этого в составе серии 7400 имеется специальная схема с ТТЛ-структурой, но без оконечного элемента типа каскадного выхода. Она имеет открытый коллектор, к которому можно присоединить снаружи соответствующий коллекторный резистор или же внешний транзистор для управления мощными схемами. ТТЛ-схема И-НЕ с открытым коллектором приведена на рис. 7.

Рисунок 7. ТТЛ-схема И-НЕ с разомкнутым коллектором. Коллекторный резистор подключается снаружи. Эта схема применяется для реализации МОНТАЖНОГО ИЛИ.

Содержание.

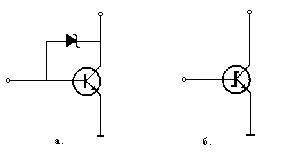

Маломощные ТТЛШ-схемы. В последние годы фирма Texas Instruments разработала технологию изготовления схем, известных под названием маломощные ТТЛ-схемы с диодами Шоттки(ТТЛШ). В настоящее время эти схемы выпускаются многими фирмами-изготовителями и среди них фирмой Signetics. Отличительными особенностями данных схем являются следующие: взаимозаменяемость со стандартными ТТЛ-схемами серии 7400, рассеиваемая мощность 2 мВт на вентиль, коэффициент разветвления по выходу 20 и время задержки 10 нс. Помехоустойчивость для низкого и высокого уровней равна 0,4 В (в этом отношении новые схемы не отличаются от стандартных ТТЛ-аналогов). Очевидным достоинством этих схем является низкая потребляемая мощность, которая приходится на один логический элемент, и составляет 1/5 соответствующего значения для стандартных ТТЛ-схем. В ТТЛШ-схемах вместо обычных диодов и транзисторов используются диоды и транзисторы Шоттки. Транзистор Шоттки отличается от обычного транзистора тем, что в нем коллектор соединен с базой с помощью диода Шоттки, который предотвращает работу транзистора в режиме насыщения. Благодаря этому соединению исключается эффект накопления электронов в области базы, т. е. в конечном счете уменьшаются задержки, зависящие от эффекта накопления. На рис. 8 показан транзистор с диодом Шоттки, включенным между коллектором и базой, и его схемное обозначение. Так как диоды Шоттки имеют высокое быстродействие, то транзисторы Шоттки обладают хорошим коммутационными параметрами. Кроме того, они легко объединяются на одном кристалле в сложные ТТЛШ-схемы.

Рисунок 8. Транзистор, в котором переход база-коллектор шунтируется диодом Шоттки. Такая комбинация называется транзистором Шоттки(а), который в логических схемах обозначается с помощью символа, приведенного на рис б.

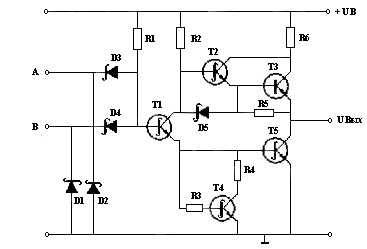

На рис. 9 приведена базовая маломощная ТТЛШ-схема И-НЕ.

Рисунок 9. Маломощная ТТЛШ-схема И-НЕ.

Видно, что многоэмиттерный вход, который нам уже знаком по ТТЛ-схемам, заменен здесь схемой И из диодов Шоттки (эти диоды называются также диодами с горячими носителями). В диодах Шоттки практически нет процесса накопления носителей заряда, в результате чего их быстродействие оказывается намного выше, чем быстродействие диодов с обычными р-n-переходами. Кроме того, контактная разность потенциалов оказывается для диодов Шоттки ниже (всего 0,2В), чем для обычных диодов, что позволяет реализовать указанную выше величину помехоустойчивости. Диоды с заземленным выводом, выполняющие функции ограничителя, широко используются на входе различных ИС, подавляя осцилляции и отражения во входных сигнальных линиях, что приводит к повышению их быстродействия. Кроме того, диоды Шоттки включаются между коллекторами и базами транзисторов, применяемых в логических схемах, в результате чего исключается режим их насыщения. Разумеется, здесь мы также выигрываем в быстродействии за счет ограничения накопления носителей заряда в базе. Новыми элементами этой схемы, по сравнению со стандартными ТТЛ - схемами, является конфигурация Т2/Т3, образующая схему Дарлингтона, и Т4 в режиме "активной нагрузки". Применение этих элементов приводит к дальнейшему уменьшению времени задержки распространения и увеличению помехоустойчивости. Благодаря применению транзисторов и диодов Шоттки можно, как уже говорилось выше, уменьшить рассеянную мощность ТТЛШ вентиля в 5 раз по сравнению со стандартным ТТЛ-вентилем, не увеличивая при этом время задержки. Различие в обозначениях между ТТЛ и ТТЛШ заключается в том, что после номера для ТТЛШ серии ставятся буквы LS, т. е., например, ТТЛШ-вентиль из серии 7400 обозначается как SN74LSOO. Коэффициент разветвления по выходу для маломощных ТТЛШ-схем можно вычислить, поделив выходной ток управляющего элемента на входной ток управляющего элемента. Для ТТЛШ-схем этот параметр при низком уровне напряжения равен 8/0,4=20 и при высоком уровне - 400/20=20. По сравнению со стандартными ТТЛ-схемами коэффициент разветвления по выходу для маломощных ТТЛШ-схем увеличился в 2 раза (20 вместо 10).

Содержание.

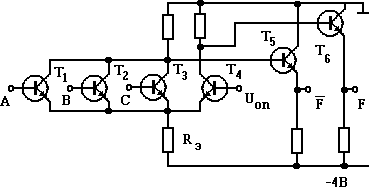

Эмиттерено-связанная логика(ЭСЛ). Включение транзисторов в входных каскадах интрегральных микросхем ЭСЛ позволяют им работать в ненасыщенном режиме. Как можно видеть на рисунке 10, транзисторы Т1-3 и Т4 образуют дифференциальный усилитель, работающий как преключатель токов. Опороное напряжение Uоп на транзисторе Т4обеспечивает постоянное смещение на эмиттере. На резисторе Rэ суммируются токи, протекающие через Т1-3 и Т4. При напряжении на любом из входов A, B или C, большем Uоп происходит изменение потенциалов и этот разбаланс передаются на выходные повторители Т5 и Т6.

Рисунок 10. Базовая ЭСЛ схема ИЛИ-НЕ.

Времена задержки на один вентиль в ЭСЛ схемах невелики ~3-5 нс. Логические уровни зависят от отношения сопротивлений, а не от их абсолютных величин. Разность логических уровней мала, обычно около вольта. ЭСЛ схемы весма быстродействующие, но имеют большие токи потребления. Ни по напряжению питания, ни по логическим уровням ЭСЛ схемы не совместимы с ТТЛ ИМС.

Содержание.

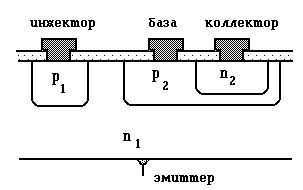

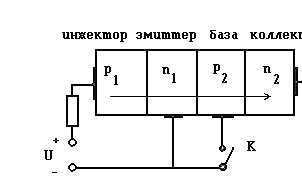

Инжекционно-интегральная логика(И2Л). Инжекционно-интегральная логика появилась в 1971 г. Преимущество таких ИМС - высокая степень интеграции, малое потребление энергии на одно переключение ~ 10-12Дж. Низкие напряжение питания: 1-3 В. Как видно на рисунках 11 и 12 такого рода транзисторы имеют четырех слойную структуру, как и тиристор.

Рисунок 11. Устройство транзистора с инжекционным питанием.

Рисунок 12. Конструкция траннзистора с инжекционным питанием.

Ключом К может служить такой же транзистор с инжекционным питанием.

Содержание.

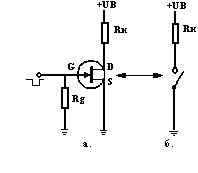

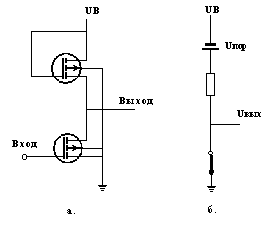

Логические схемы на МОП-транзисторах. Обычно МОП-транзистор нормально закрыт, т.е. существует пороговое напряжение Uпор на затворе для его открытия, что позволяет использовать его в цифровых схемах как ключевой элемент. Другим его свойством, особенно интересным для применений в ИС, является высокая плотность упаковки функциональных элементов. Она оказывается приблизительно в 10 раз выше, чем в ИС на основе биполярных транзисторов. Кроме того, высокий входной импеданс полевых МОП-транзисторов способствует тому, что логические схемы рассеивают небольшую мощность в области затвора (т. е. в области управляющего элемента), а это, в свою очередь, позволяет получить почти бесконечную нагрузочную способность в режиме постоянного тока. Наконец, сопротивлением полевого МОП-транзистора можно управлять, что позволяет размещать в небольшом объеме очень сложные схемы. Одним из базовых элементов цифровых схем является инвертор. На рис. 10 показан инвертор на основе МОП-транзистора с каналом р-типа и нагрузочным сопротивлением в виде такого же транзистора.

Рисунок 13. а. - Инвертор на двух полевых МОП-транзисторах с р-каналом; б. - эквивалентная схема инвертора во включенном состоянии.

Во включенном состоянии полевой МОП-транзистор ведет себя как резистор с малым сопротивлением, которое сравнимо с сопротивлением канала насыщенного полевого транзистора, соединенного последовательно с источником напряжения, равного пороговому напряжению МОП-транзистора. В выключенном состоянии нижний транзистор имеет очень высокое сопротивление и на выходе появляется сигнал высокого уровня. Нагрузочный (верхний) транзистор действует как истоковый повторитель, в результате чего выходное напряжение вентиля не превышает напряжения питания, уменьшенного на величину порогового напряжения Uпор МОП-транзистора. МОП-инвертор с МОП-резистором в качестве нагрузки потребляет небольшую мощность, которая, тем не менее, велика, чтобы осуществить реальную интеграцию в больших размерах. В широко применяемых системах памяти с произвольным доступом на базе МОП-элементов и в микропроцессорах потребляемую мощность необходимо ограничивать таким образом, чтобы на одном кристалле можно было разместить несколько тысяч транзисторов. В ЗУ потребляемая мощность ограничивается тем, что в качестве запоминающих ЗУ используются МОП-конденсаторы, что позволяет обойтись меньшим числом транзисторов в ячейке ЗУ, а это приводит к увеличению плотности упаковки. В таких динамических ЗУ, обеспечивающих объем памяти 64 000 бит на один кристалл, внутренние МОП-конденсаторы необходимо периодически подзаряжать, так как со временем они разряжаются. Мощность в таких ЗУ потребляется только во время подзарядки и во время считывания записи. В статических МОП-ЗУ, ячейками которых являются триггеры, необходимо использовать элементы с большой площадью, что связано как с большими размерами ячеек, так и с рассеянием мощности. Эти ЗУ не нуждаются в подзарядке, поэтому можно обойтись меньшим числом внешних схем, которые обычно требуются для подзарядки. Хотя площадь статической ячейки превышает площадь соответствующей динамической ячейки, в настоящее время удается благодаря усовершенствованной технологии получить ЗУ с объемом памяти 8000 бит на один кристалл. МОП-ЗУ относятся к разряду "энергозависимых", т. е. при выключении питания в них информация разрушается (в ЗУ на ферритах информация в этих же условиях сохраняется). Полупроводниковые ЗУ рассмотрены более подробно в Главе Устройства памяти Недостатком полевых МОП-транзисторов с алюминиевым затвором является довольно высокое пороговое напряжение, поэтому приходится использовать повышенное напряжение питания, которое влияет на быстродействие схем. Кроме того, возникают проблемы при объединении МОП-транзисторов с биполярными цифровыми схемами, такими, например, как ТТЛ. При более высоком напряжении питания возрастает также потребляемая мощность. Влияние величины напряжения питания на быстродействие схемы объясняется тем, что в процессе зарядки паразитных выходных емкостей напряжение достигает уровня переключения тем быстрее, чем ниже напряжение питания. Высокое пороговое напряжение определяется контактной разностью потенциалов между алюминиевым затвором и слоем кремния, расположенным под ним, причем эта разность потенциалов действует в обратном направлении. Контактную разность потенциалов можно уменьшить на 1 В и больше, заменив алюминиевый затвор на р+ -затвор из кремния и, кроме того, используя между затвором и каналом проводимости слой диэлектрика с большей диэлектрической постоянной (например, слой нитрида кремния).