смехотехника

.docСодержание.

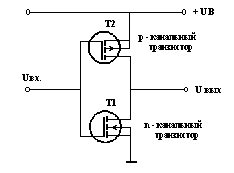

КМОП-схемы. Для существенного снижения потребляемой мощности в логических МОП-схемах и повышения их быстродействия была разработана новая модификация логических МОП-схем, известная под общим названием КМОП-схем, которые разрабатываются фирмами RCA, Motorola и Philips в виде серий COSMOS, McMOS и LOCMOS. На рис. 14. показана базовая схема КМОП-инвертора.

Рисунок 14. Базовая схема КМОП-инвертора.

Реализация как n-канального, так и p-канального транзистора на подложке одного типа показана на рисунке в разделе, посвященном ОЗУ. Если в этой схеме на вход подается напряжение высокого уровня, напряжение на затворе n-канального T1 превысит пороговое, а напряжение на затворе p-канального транзистора Т2 будет меньше порогового (т.к. его подложка соединена с шиной питания +5В). При этом T1 становится проводящим, а T2 запирается. Выход схемы замыкается на землю (низкий уровень) через T1 (~300 Ом). И наоборот, если на вход подается напряжение низкого уровня, проводящим оказывается Т2, а запирается T1. Выход схемы замыкается на шину Uв через сопротивление Т2, равное 500 Ом. Ток запирания в канале обоих транзисторов не превышает 1 нА. Кроме того, нагрузка, образованная другими МОП-cxeмами, благодаря изолированному затвору будет мала. Входной ток определяется током утечки между затвором и каналом проводимости и составляет <1 нА. На рис. 15 и 16 приведены КМОП-схемы ИЛИ-НЕ и И-НЕ соответственно.

|

|

Рисунок 15. КМОП-схема ИЛИ-НЕ с таблицей истинности.

Если в схеме ИЛИ-НЕ на оба входа поданы напряжения низкого уровня, то ТЗ и T4 запираются. Входное напряжение обоих транзисторов не превышает пороговое. И наоборот, для верхних последовательно включенных р-канальных транзисторов пороговое напряжение будет превышено и оба транзистора будут открыты. Таким образом, на выходе схемы появится напряжение высокого уровня. Если на один или на оба входа подано напряжение высокого уровня, открытым всегда будет нижний транзистор, а запертым - верхний транзистор. В результате на выходе схемы появится напряжение низкого уровня. Поведение этой схемы определяется таблицей истинности, приведенной на рис. 15

|

|

Рисунок 16. КМОП-схема И-НЕ с таблицей истинности.

В отличие от схемы ИЛИ-НЕ в схеме И-НЕ верхние транзисторы с каналами р-типа включены параллельно, а нижние транзисторы с каналами n-типа - последовательно. Если на один или оба входа подано напряжение низкого уровня, один из нижних транзисторов всегда будет заперт, а один из верхних открыт. На выходе появляется напряжение высокого уровня. И только в том случае, когда на оба входа одновременно подано напряжение высокого уровня, открываются оба нижних транзистора и запираются оба верхних. В результате на выходе схемы появляется напряжение низкого уровня. Поведение этой схемы И-НЕ определяется таблицей истинности, приведенной на рис. 13. Из таблицы истинности для схемы ИЛИ-НЕ можно сделать вывод, что эта схема обеспечивает функцию ИЛИ-НЕ для сигналов высоких уровней и функцию И-НЕ - для сигналов низких уровней. В случае схемы И-НЕ мы получаем функцию И-НЕ для сигналов высокого уровня и ИЛИ-НЕ - для сигналов низкого уровня.