Шины.PCI,.USB.и.FireWire

.pdfпорог заполнения выбирается исходя из максимально допустимого расхождения частот и максимальной длины передаваемого пакета.

Питание от шины

Для питания узлов постоянным током в кабелях IEEE 1394 предусмотрена отдель$ ная пара проводов — VG (общий провод, GND) и VP (положительный полюс пита$ ния) с напряжением 8–40 В при токе до 1,5 А. В 1394a диапазон напряжений су$ жен до 8–33 В. Узлы могут быть источниками, потребителями питания или не пользоваться питанием от шины; их отношение к питанию сообщается в поле pwr пакета самоидентификации (см. главу 23). В узлах$повторителях линии питания всех портов объединены. Узлы$источники питания подают напряжения на линию питания через ограничитель тока и диод, так что мощность, подаваемая от несколь$ ких узлов, суммируется. При подключении узел сначала может потреблять от шины не более 1 Вт (1394a — 3 Вт), при этом обязательно должен быть включен уровень PHY. Уровни LINK и выше, как и прикладная часть устройства, могут потреблять дополнительную мощность, заявленную в поле pwr. Однако эти уровни будут вклю$ чаться только по команде от диспетчера шины или диспетчера изохронных ресур$ сов. Каждый узел контролирует питание от шины: при напряжении выше 7,5 В он устанавливает бит PS (power status), сообщаемый в пакете самоидентификации. При падении уровня напряжения ниже 7,5 В физический уровень должен обну$ лить бит PS и уведомить об этом событии управляющее ПО.

Понятие классов питания (Power Class) относится к питанию узлов от кабельной шины IEEE 1394. Класс питания узла сообщается им в поле pwr пакета самоиден$ тификации. В соответствии с классом питания возможны следующие конфигура$ ции узла:

узел с автономным питанием (Self$Power), для которого возможно несколько вариантов:

однопортовый узел не питается от шины и не подает питание сам (pwr = 0);

многопортовый узел не питается от шины, не транслирует питание с других портов и не подает питание сам (pwr = 0);

многопортовый узел не питается от шины, но транслирует питание с других портов (pwr = 4);

поставщик питания (Power Provider, pwr = 1, 2 или 3) — узел питается самосто$ ятельно и подает на шину питание с указанием минимальной мощности;

альтернативный поставщик питания (Alternate Power Provider, pwr = 4) — узел может питаться от шины, а также может поставлять питание;

потребитель (Power Consumer, pwr = 5, 6 или 7) — узел (только однопортовый) питается от шины. До завершения конфигурирования мощность потребляет только PHY (не более 1 или 3 Вт). Верхние уровни (LINK и выше), требующие дополнительной мощности, узел включает только по команде от диспетчера.

Характеристики классов питания приведены в табл. 22.6. В 1394a и 1394b пара$ метры потребления несколько отличаются от первоначальных определений 1394– 1995 и зарезервирован класс 5. Для класса 4 поставляемая мощность указывается в памяти конфигурации узла.

Таблица 22.6. Классы питания

Клас (pwr) |

Поставляет, Вт |

Потребляет, Вт (1394–1995) |

Потребляет, Вт (1394a, b) |

||

|

|

PHY |

LINK |

PHY |

LINK |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

15 |

0 |

0 |

0 |

0 |

2 |

30 |

0 |

0 |

0 |

0 |

3 |

45 |

0 |

0 |

0 |

0 |

4 |

01 |

1 |

0 |

3 |

0 |

5 |

0 |

1 |

2 |

Резерв |

Резерв |

6 |

0 |

1 |

5 |

3 |

3 |

7 |

0 |

1 |

9 |

3 |

7 |

|

|

|

|

|

|

1 Для класса 4 поставляемая мощность указывается в памяти конфигурации узла.

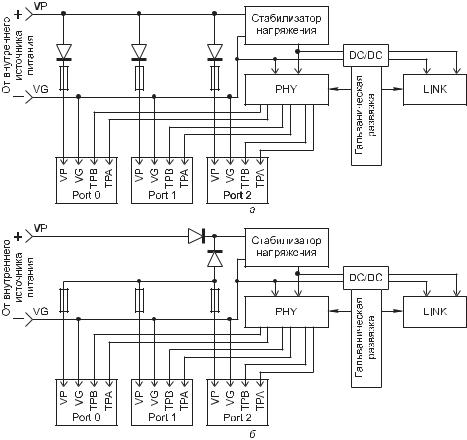

Каждой конфигурации соответствует своя схема соединения линий питания пор$ тов, собственного PHY и внутреннего (батарейного или сетевого) источника пита$ ния. Обобщенная схема питания узла приведена на рис. 22.9, для каждой из выше$ приведенных конфигураций на схеме будут отсутствовать те или иные элементы. Общие идеи следующие:

для многопортового узла следует предусмотреть питание PHY$уровня до по$ следней возможности — это обеспечивает целостность шины (отключение пи$ тания PHY сегментирует шину, поскольку узел не сможет транслировать сиг$ налы и трафик). Питание на PHY может подаваться и от кабеля, и от внутреннего источника (через диоды);

поставщик питания должен подавать питание на каждый порт через индивиду$ альные разделительные диоды и ограничители тока (рис. 22.9, а). При этом каж$ дый порт представляет отдельный домен питания (Power Domain);

альтернативный поставщик, обеспечивающий напряжение ниже 20 В, может и не обеспечивать разделения доменов (но индивидуальные ограничители тока обя$ зательны);

узел с автономным питанием, транслирующий питание, при числе портов бо$ лее двух должен иметь ограничители тока на каждый порт.

На рисунке в качестве ограничителей тока условно изображены плавкие предох$ ранители. Реально, конечно же, используются или электронные ограничители, или самовосстанавливающиеся полупроводниковые предохранители.

Рис. 22.9. Схема подачи питания от шины: а — узел поставщик питания; б — узел потребитель питания

Гальваническая развязка

Возможность гальванической развязки узлов шины IEEE 1394 позволяет решить ряд проблем, связанных с объединением «схемных земель» соединяемых устройств.

Ваудиотехнике из$за наводок в контуре заземления возникают помехи, неприем$ лемые для работы высококачественной аппаратуры, на которую и ориентирована шина.

Впервых спецификациях, в которых используется только DS$сигнализация, гальваническая развязка возможна только в интерфейсе PHY$LINK. Этот парал$ лельный интерфейс содержит значительное число сигнальных цепей, по которым передаются сигналы с уровнями логики КМОП или ТТЛ. Большая часть этих сиг$ налов имеет весьма высокую частоту переключения (около 50 МГц), что не позво$

ляет применить дешевую оптронную развязку1. Оптроны удобно применять толь$ ко для медленных сигналов LinkOn и LPS. Кроме того, ряд сигнальных цепей ис$ пользуется для двунаправленной передачи, что осложняет схему развязки. Самый простой и дешевый способ развязки — введение разделительных конденсаторов. Однако при этом развязка осуществляется только по постоянному току (типичное напряжение развязки до 60 В); высокочастотные помехи, вызывающие пульсации на общем проводе, будут воздействовать на интерфейс. Полную развязку обеспе$ чивают только импульсные трансформаторы (1:1), устанавливаемые в каждой цепи; при этом достижимо напряжение изоляции развязки до 500 В. Однако это слиш$ ком дорогой и громоздкий вариант, который используется редко. И конденсаторы, и трансформаторы фактически выполняют дифференцирование сигналов (пере$

Рис. 22.10. Гальваническая развязка цепей интерфейса PHY LINK: а — схема развязки по IEEE 1394; б — развязка сигнальных цепей по IEEE 1394b

1Обычные оптроны слишком инерционны, быстродействующие оптические приемники, применяемые, например, в сетях передачи данных, слишком дороги.

дают только перепады). Специально для этого и LINK, и PHY имеют конфигу$ рирующие сигналы Direct, по которым интерфейсные цепи настраиваются на прием непосредственных сигналов (без развязки) или дифференцированных (с развязкой).

В приложении стандарта IEEE 1394 и в основном тексте IEEE 1394a приводится довольно громоздкая схема конденсаторной развязки (рис. 22.10, а), содержащая большое число резисторов, «подтягивающих» уровни сигналов. В IEEE 1394b при$ ведена более элегантная схема установки привязки состояний входов, использую$ щая КМОП$вентили (повторители) с высокоомной обратной связью (рис. 22.10, б). На рисунках изображены цепи развязки для одной из десяти сигнальных ли$ ний.

Для портов, работающих в бета$режиме (IEEE 1394b), полная гальваническая раз$ вязка стала возможной в цепях сигналов внешнего электрического интерфейса. Параметры этой развязки приводятся в начале данной главы. Использование оп$ товолоконной связи позволяет обеспечить бескомпромиссную развязку с любым требуемым напряжением изоляции.

Гальваническая развязка сигнальных цепей подразумевает и развязку для кабель$ ного питания. Эта развязка осуществляется с помощью импульсных преобразова$ телей напряжения (DC/DC Converter).

Взаимодействие с физическим уровнем шины IEEE 1394

Физический уровень (PHY) обеспечивает LINK$уровню возможность обращения к шине для посылки и приема пакетов и исполнения некоторых служебных дей$ ствий. Физический уровень имеет свои регистры, служащие для управления вы$ полнением функций и определения состояния шины и узлов. К этим регистрам имеется возможность локального доступа — приложение узла через LINK$уровень может общаться с регистрами PHY. Содержимое некоторых регистров может из$ меняться по приему пакетов физического конфигурирования. В 1394a появилась возможность удаленного обращения к регистрам чужого узла на данной шине. Физический уровень не только обеспечивает передачу и прием пакетов для LINK$ уровня, но и сам является источником и получателем служебных пакетов.

Интерфейс с канальным уровнем

Физический и канальный уровни (PHY и LINK) в стандарте IEEE 1394 отделимы друг от друга. Это обеспечивает модульность построения устройств и возможность гальванической развязки основной (прикладной) части устройства от кабельного интерфейса. В устройствах физический и канальный уровни могут реализоваться раздельными микросхемами, причем даже разных производителей. Интерфейс между ними был описан в приложении к стандарту 1394, но в рекомендательной (необязательной) форме. В 1394a этот интерфейс (с небольшими изменениями) объявлен стандартом. Cвязь физического и канального уровней обеспечивается интерфейсом PHY$LINK. По этому интерфейсу канальный уровень получает сер$ висы доступа к шине для передачи и приема пакетов данных, а также доступ к внутренним регистрам PHY.

В IEEE 1394b в связи с особенностями бета$режима подход к организации интер$ фейса связи с физическими портами изменился. Здесь появился новый промежу$ точный интерфейс PIL$FOP, который позволяет соединять микросхему, в кото$

рой LINK интегрирован с однопортовым PHY, с многопортовым разветвителем. Таким образом, в 1394b имеются два варианта интерфейса:

параллельный интерфейс B PHY LINK, являющийся развитием своего традици$ онного предшественника и обеспечивающий работу с портами на скоростях от S100 до S800 как в традиционном, так и в бета$режиме;

последовательный интерфейс PIL FOP, по сигналам соответствующий электри$ ческому интерфейсу порта в бета$режиме, подключающий многопортовый PHY$ разветвитель (называемый FOP) к однопортовому PHY, интегрированному с LINK$уровнем (эта комбинация называется PIL). Последовательный интер$ фейс поддерживает все режимы и скорости (от S100 до S3200).

Интерфейс PHY LINK 1394 и 1394a

Интерфейс PHY–LINK изображен на рис. 23.1, назначение сигналов раскрыто в табл. 23.1. Интерфейс содержит небольшое количество сигналов, и именно для этих сигналов и возможно введение гальванической развязки (см. главу 22).

Рис. 23.1. Интерфейс PHY LINK 1394 и 1394a

На рисунке приведены сигналы для обоих вариантов шины — кабельной и кросс$ шины. Описание интерфейса, приведенное ниже, относится к самому распростра$ ненному варианту — кабельной шине. В этом варианте не используются (отсут$ ствуют) сигналы Clk25 и Bacкlplane.

Для кросс$шины в интерфейсе LINK$PHY сигнал SClk имеет пониженную частоту (24,756 или 12,288 МГц для S50 и S25 соответственно); для идентификации ис$ пользуемой частоты введен сигнал Clk25 (0 — 12,288 МГц, 1 — 24,576 МГц). При$ знаком подключения LINK$уровня к Backplane PHY является дополнительный сигнал Backplane (от PHY к LINK’у). Особенности PHY$уровня Backplane$вариан$ та рассмотрены в главе 22.

Таблица 23.1. Сигналы интерфейса LINK PHY

Сигнал |

Назначение |

D[0:7] |

Двунаправленная шина данных. На S100 используются только линии D[0:1], |

|

на S200 — D[0:3], на S400 — D[0:7] |

|

|

Сигнал |

Назначение |

Ctl[0:1] |

Состояние интерфейса (табл. 23.2) |

LReq |

Link Request, последовательный интерфейс, по которому LINK инициирует |

|

запрос к PHY (для передачи пакетов и обращения к регистрам) |

SClk |

Синхронизация (49,152 МГц) для вышеприведенных сигналов. Источник меняет |

|

состояние сигнала по спаду SClk, приемник фиксирует состояние по фронту SClk |

LPS |

Link Power Status, признак активности (включения) LINK уровня |

LinkOn |

Сигнал для включения LINK уровня |

Direct1 |

Признак непосредственного соединения LINK PHY (нет дифференцирования |

|

сигналов) |

|

|

1 В микросхемах этот вывод может называться «Iso» (изоляция).

Интерфейсом управляет PHY; LINK может посылать запросы только в определен$ ных состояниях интерфейса. Право передачи информации по двунаправленным ли$ ниям данных LINK получает от PHY. Текущее состояние интерфейса (использова$ ние шины данных) определяется сигналами Ctl[0:1] в соответствии с табл. 23.2.

Таблица 23.2. Состояние интерфейса LINK PHY

Ctl[0:1] |

Состояние интерфейса |

|

Линиями Ctl[0:1] управляет PHY: |

00 |

Idle — нет активности (LINK может посылать запрос) |

01Status — PHY по шине данных посылает информацию о событиях или ответ на запрос чтения регистра

10Receive — PHY передает LINK уровню пакет, принимаемый с шины,

или генерируемый им (PHY пакет), или пакет ответа на запрос к регистрам PHY

11Grant — PHY передает LINK’у право использования шины данных

Линиями Ctl[0:1] управляет LINK:

00Idle — нет активности: LINK завершил передачу и отдает управление интерфейсом уровню PHY

01Hold — LINK удерживает шину, готовясь к передаче пакета (или после передачи пакета, собираясь послать следующий без повторного арбитража)

10Transmit — LINK передает данные PHY (для передачи в шину или обращения к регистрам PHY)

11Не используется

В состоянии Status PHY по линиям данных D[0:1] за два такта передает 4 бита со$ стояния (Stat[0:1] в первом такте и Stat[2:3] во втором (табл. 23.3).

Таблица 23.3. Состояние, сообщаемое PHY

Бит Значение

0ARB_RESET_GAP — обнаружение зазора сброса арбитража (указание на начало нового интервала справедливости)

продолжение

Таблица 23.3 (продолжение)

Бит Значение

1SUBACTION_GAP — обнаружение нормального зазора арбитража (можно запрашивать право посылки очередного асинхронного пакета)

2BUS_RESET_START — обнаружение сброса на шине

3PHY_INTERRUPT — прерывание от PHY, причина уточняется чтением PHY регистра 0101b. Возможные события: обнаружение петли во время идентификации дерева; обнаружение снижения питающего напряжения (ниже 7,5 В); обнаружение тайм аута арбитража; обнаружение изменения напряжения смещения

Запросы LINK к PHY

Запрос от LINK к PHY посылается в последовательном виде по линии LReq. За$ прос начинается с единичного старт$бита (LReq0 = 1) и завершается нулевым стоп$ битом (LReq6 в 1394 и LReq7 в 1394a). За старт$битом следует код типа запроса (биты LReq[1:3]), за которым следуют биты тела запроса. Типы запросов, их коды и состояния интерфейса, во время которых LINK их имеет право посылать, приве$ дены в табл. 23.4.

Таблица 23.4. Запросы LINK к PHY

Код запроса |

Назначение |

Состояния, в которых |

LReq[1:3] |

|

допустима подача запроса |

|

|

|

000 |

ImmReq, немедленный запрос (без задержки |

Idle, Receive |

|

арбитража) для передачи пакета квитирования |

|

001 |

IsoReq, запрос изохронной передачи |

Все (и Idle, когда интерфейсом |

|

|

владеет LINK) |

010 |

PriReq, запрос передачи пакетов начала |

Idle, Status |

|

цикла и приоритетных асинхронных пакетов |

|

011 |

FairReq, запрос передачи обычных |

Idle, Status |

|

асинхронных пакетов |

|

100 |

RdReg, запрос чтения регистра PHY |

Все |

101 |

WrReg, запрос записи регистра PHY |

Все |

110 |

Acceleration Control, управление |

Все |

|

ускорением арбитража: LReq[4]= |

|

|

1 — разрешить, 0 — запретить |

|

111 |

Резерв |

|

|

|

|

Запросы на передачу

Тело запросов передачи пакетов содержит код скорости, за который отвечают биты LReq[4:5]; в 1394a он занимает биты LReq[4:6]. Дополнительный бит в запросе 1394a появился ради введения дополнительных скоростей; назначение кодов ско$

рости обеспечивает совместимость запросов 1394 и 1394a (на скоростях S100–S400 бит LReq6=0, он может восприниматься как стоп$бит). Коды скоростей в запросе 1394a приведены далее:

S100 — 000 (00 в 1394); S800 — 110;

S200 — 010 (01 в 1394); S1600 — 001;

S400 — 100 (10 в 1394); S3200 — 011.

Послав запрос на передачу пакета, LINK должен следить за состоянием интерфей$ са (по состоянию сигналов Ctl[1:0]), дожидаясь разрешения передачи пакета — со$ стояния Grant. Это состояние появляется, когда PHY выигрывает арбитраж для данного запроса. Обнаружив состояние Grant, LINK берет на себя управление ин$ терфейсом и шиной, установив на линиях Ctl[1:0] признак состояния Hold. Во время передачи по шине данных пакета LINK устанавливает признак состояния Transmit. Завершив передачу пакета, LINK устанавливает признак состояния Idle, чем отда$ ет управление интерфейсом PHY$уровню. Если LINK посылает подряд несколько пакетов (в соединенных транзакциях или при ускоренном арбитраже), то между пакетами он удерживает интерфейс (и шину), сигнализируя состояние Hold.

Состояния Idle и Status, наблюдаемые LINK’ом после подачи запроса передачи, означают, что запрос обслуживается (LINK должен ждать дальше). Состояние Receive для обычных и приоритетных запросов означает, что запрос отвергнут PHY (LINK его должен повторить позже). Запрос передачи пакета квитирования не отвергается (для него Receive означает ожидание). Запросы изохронных передач отвергаются только в случае получения в состоянии Status уведомления об обна$ ружении нормального зазора арбитража (истекло время, отведенное на изохрон$ ные передачи в данном цикле).

Прием пакетов

Пакеты, принимаемые по шине и предназначаемые данному узлу, PHY передает по шине данных D[0:7] в состоянии Receive. При приеме PHY передает по D[0:7] некоторое количество байтов FFh (признак Data On), байт$индикатор скорости и собственно пакет данных. Признаком конца пакета будет переход интерфейса в состояние Idle. При подсчете CRC$кода LINK учитывает только байты пакета (без индикатора скорости). Байт$индикатор скорости указывает LINK’у, сколько линий D[0:7] будет использоваться при передаче данного пакета. Если LINK не поддерживает данную скорость, он должен игнорировать весь трафик до обнару$ жения состояния Idle. Значение индикатора скорости приведено в табл. 23.5.

Таблица 23.5. Индикация скорости от PHY к LINK

Скорость |

D[0:7] |

Скорость |

D[0:7] |

S100 |

00xxxxxx |

S800 |

01010001 |

S200 |

0100xxxx |

S1600 |

01010010 |

S400 |

01010000 |

S3200 |

01010011 |

|

|

|

|