LR2

.docx

Лабораторна робота №2

Тема: Методи адресації МП i8086 та команди пересилання даних

Цілі: Вивчення методів адресації МП i8086 та використання команди пересилання даних.

Хід роботи:

1 Короткі теоретичні відомості

1.1 Формування фізичної адреси

Фізичний об'єм пам'яті процесора i8086 містить 1 Мбайт. Але 16-тирозрядна архітектура процесора дозволяє звертатися тільки до 64 Кбайт пам'яті. Для забезпечення доступу до даних об'єм в 1 Мбайт використовується метод сегментації пам'яті.

Сегментація пам'яті – це виділення окремих областей пам'яті з єдиного адресного простору й надання їх у користування. Сегмент може розміщатися в любій точці пам'яті об'ємом в 1 Мбайт, а його адреса повинна містити 20 розрядів та змінюватися від 00000h до FFFF0h. Об'єм сегмента визначається розрядністю регістрів і становить 64 Кбайта (216 = 65565 байт). Сегменти можуть мати наступне розташування відносно один одного: накладатися, стикатися, мати загальні області, бути вкладеними або ізольованими.

Фізична адреса елементів у пам'яті має дві складові: адреса сегменту та адреса зміщення в середині сегменту.

Процесор i8086 одночасно може працювати з чотирма сегментами пам'яті, початкові адреси яких визначають чотири сегментних регістри: CS, DS, SS, ES.

Сегментні регістри містять різні види інформації виконуваної програми:

-

CS – сегмент команд, містить коди виконуваної програми;

-

DS – сегмент даних, містить необхідні дані, проміжні та кінцеві

-

результати обчислень;

-

SS – сегмент стека, призначений для зберігання адреси тимчасових зупинок програм та необхідних даних для продовження виконання перерваної програми;

-

ES – додатковий сегмент даних, обов'язків при виконанні дій з командами обробки строк.

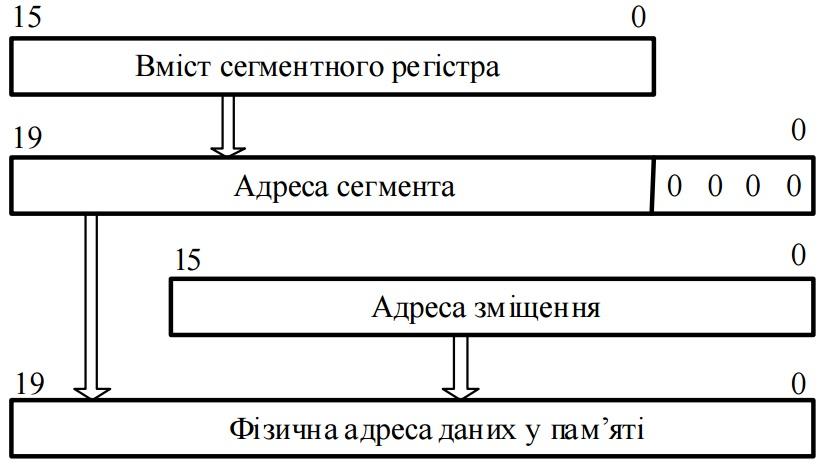

У сегментних регістрах містяться старші 16 розрядів адреси сегментів пам'яті. 20-розрядна фізична адреса сегмента пам'яті в чотирьох молодших розрядах завжди містить нулі. Адреса зміщення в середині сегменту 16-розрядна і дозволяє звернутися до любої адреси в середині 64 Кбайтного сегменту.

Повну фізичну адресу любого елемента пам'яті можна визначити наступною формулою:

ФА = Асегм + Азміщ = [*S ] ×10h + Азміщ.

Перетворення 16-розрядних складових адреси в 20-розрядний адрес виконується за допомогою суматора в блоці сполучення з шиною.

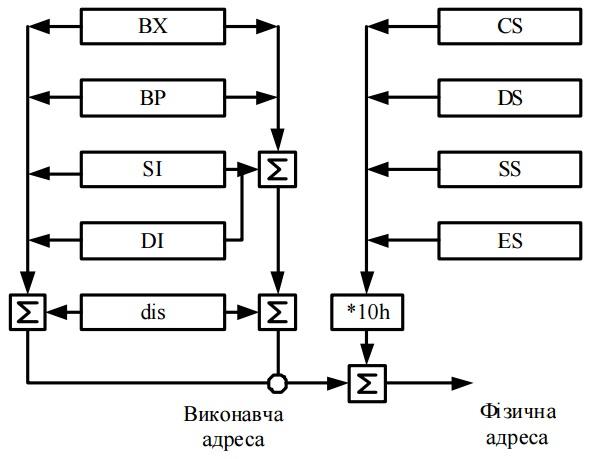

Схема формування 20-розрядної адреси наведена на рис. 1.

Рисунок 1 – Схема формування 20-розрядної адреси

У формуванні адреси команди використовуються сегментний регістр CS, який визначає фізичну адресу розміщення виконуваної програми, та значення покажчика адреси команд IP, який містить адресу наступної команди на виконання в сегменті команд.

Розглянемо обчислення фізичної адреси команди.

Складові частини адреси команди знаходяться в регістрах: CS = 0F10h та IP = 0010h.

Початок сегмента визначається: Асегм = [CS] * 10h = 0F100h.

Фізична адреса визначається: ФА = Асегм + [IP] = 0F100h + 0010h.

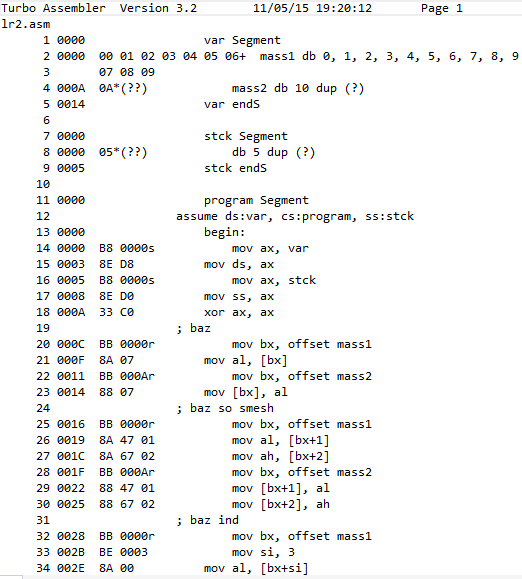

У формуванні повної фізичної адреси розміщення даних використовуються також регістри: ВХ, SI, DI, ВР.

Можливі варіанти використання регістрів у формуванні адреси наочно показані на рис. 2.

Рисунок 2 – Схема формування фізичної адреси

Кожен із регістрів, який використовується при формуванні адреси, має свої особливості, що дозволяє одержувати різні методи доступу до даних.

1.2 Організація роботи стека

Одним із різновидів сегментної організації пам'яті є стек. Стек – це ділянка пам'яті, яка спеціально виділяється для тимчасового зберігання інформації про точку зупинки роботи процесора, що дає можливість у подальшому відновити роботу програми з даної точки.

Стек забезпечує виконання програм зі складною структурою, таких, що містять звертання до окремих підпрограм, і забезпечує повернення в основну програму після виконання їх.

Для організації роботи зі стеком призначені три регістри: SS – сегментний регістр стека; SP – регістр покажчика вершини стека; BP – регістр покажчика бази області стека.

Операція запису або зчитування виконується з вершини стека, яка визначається величиною зсуву, записаною в регістрі SP, а повна адреса вершини стека визначається як SS:SP. Якщо необхідно одержати доступ до елементів, розташованих усередині стека, застосовується регістр BP – регістр покажчика бази області стека.

Робота зі стеком виконується за наступними правилами:

-

запис і читання даних у стеці здійснюється відповідно до принципу LIFO (Last In First Out – "останнім прийшов, першим пішов");

-

команди роботи зі стеком автоматично змінюють вміст регістра SP таким чином, щоб він завжди вказував на останній записаний у стек елемент;

-

при занесенні елемента в стек процесор спочатку зменшує значення регістра SP, а потім записує елемент за адресою нової вершини. При вилученні даних зі стека процесор копіює елемент, що знаходиться за адресою вершини, а потім збільшує значення регістра покажчика стека SP;

-

в стек інформація записується тільки по два байти;

-

вміст регістрів SP змінюється автоматично при роботі зі стеком (при записі автоматично зменшується на 2, при читанні – збільшується на 2). Ця особливість закладена в алгоритм команд роботи зі стеком;

-

у регістрах SP і BP утримується адреса зсуву в сегменті стека, а початок стека містить регістр SS.

Для програм з простою структурою наявність стека не є обов'язковою. Тому відсутність стека не є помилкою, але програма-компоновщик (TLINK.EXE) видасть попереджувальне повідомлення про його відсутність.

1.3 Методи адресації операндів МП8086

Методи адресації – це правила, за якими визначаються безпосередньо операнди, їхнє місцезнаходження, а також адреси розміщення результатів обчислень.

Можна виділити кілька основних методів адресації, які застосовуються для знаходження даних у сегменті пам'яті: регістрова, безпосередня, пряма, непряма.

У машинній команді з двома операндами можливі наступні взаємодії операндів: регістр – регістр; регістр – пам'ять; пам'ять – регістр; безпосередній операнд – регістр; безпосередній операнд – пам'ять.

Тільки для ланцюжкових команд та при роботі зі стеком може виконуватися передача "пам'ять – пам'ять".

При регістровій адресації операнди знаходяться безпосередньо в регістрах процесора. У командах використовуються регістри однакового типу: байт або слово. Дана адресація часто застосовується в командах пересилки даних, яка має наступну структуру: mov операнда_1, операнда_2 (або mov приймач, джерело). У процесі виконання команд дуже часто змінюється значення операнда_1, а операнд_2 залишається незмінним. В операціях з регістровою адресацією для збереження даних використовуються:

-

16-розрядні регістри АХ, ВХ, СХ, DX;

-

8-розрядні регістри AH, AL, BH, BL, CH, CL, DH, DL.

Наприклад, пересилання вмісту регістра ВХ в АХ і АН в AL буде представлено такими командами:

mov ax, bx

mov al, ah

mov cl, dh

При безпосередній адресації операнд перебуває в коді команди і для його зберігання в команді виділяється поле довжиною 8 або 16 біт. Операнд-приймач може перебувати або в пам'яті, або в регістрі, а операнд може бути тільки операндом-джерелом.

Наприклад:

mov dx, 0ba64h – команда пересилає в регістр DX шістнадцяткову константу 0BA64h.

Пряма адресація вказує безпосередньо на команду, яку необхідно виконати. Пряма адресація використовується в команді безумовного переходу jmp, в якій мітка визначає нову адресу продовження виконання програми.

Це переміщення можливе тільки в межах даного сегмента.

Непряма адресація напряму не вказує на адресу розміщення інформації, а містить її складові. Якщо операнд у команді взято у квадратні дужки, то їхній вміст визначає складову адреси розташування операнда. Такий вид адресації називається непрямим.

Непряма адресація має декілька різновидів: непряма базова (регістрова) адресація; непряма індексна адресація; непряма базова індексна адресація.

Ці моделі непрямої адресації різняться між собою вибором регістрів, в яких знаходяться складові частини адреси, наявністю або відсутністю зміщення в формуванні адреси.

Непряма базова (регістрова) адресація із зміщенням та без зміщення для доступу до окремих блоків даних використовує регістри загального призначення ВХ та ВР.

Розглянемо наступні команди:

mov al, [bx]

mov [bx+ 1], al

У регістр AL заноситься інформація, що знаходиться за адресою зміщення, яка прописана в регістрі BX.

Непряма індексна адресація із зміщенням та без зміщення Використовують для формування ефективної адреси індексні регістри SI та DI, що значно полегшує роботу з масивами даних.

Непряма базово-індексна адресація має більш складну схему формування адреси. Ефективна адреса формується як сума вмісту базового й індексного регістрів. Для визначення адреси в командах може використовуватися також зміщення. Використання двох регістрів розширює можливості доступу до даних.

У першому випадку ефективна адреса другого операнда формується з двох компонентів, адреси яких знаходяться в регістрах [SI + BX]. У другому – команда пересилає в регістр АХ слово, яке знаходиться за адресою: [si + 5]+[bx].

2 Виконання завдання

2.1 Завдання

-

Сформувати масив даних об'ємом в 10 байт;

-

Сформувати пустий масив об'ємом в 10 байт;

-

Виконати перенесення даних з першого масиву в другий, використовуючи методи непрямої адресації;

-

За допомогою команди XLAT визначити 6-й елемент другого масиву.

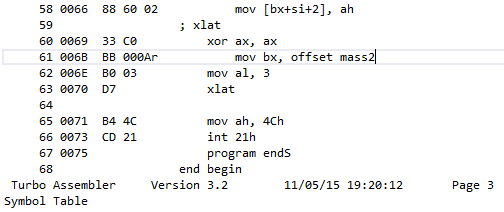

2.2 Лістинг програми

Марченко

А. Г.

6.50103.1151.09.ЛР.2

НУК

Гр.

1151

Дата

Підпис

№ докум.

Дмитрієв

Д.

Викладач

Студент

Зм.

Аркуш

Аркушів

1

Методи

адресації МП 8086 та команди пересилання

даних

Арк