Arifm_ustr

.pdf

лены в табл. 3, позволяющей определить знак vS по величине старшего пере-

носа с7. По этой таблице можно составить следующую булеву функцию:

vS vA vA c7 . |

|

(10) |

||

Таблица 3 Область определения 8-разрядных двоичных чисел |

||||

|

|

|

|

|

|

vA |

vB |

vS |

|

|

|

|

|

|

|

0 |

0 |

c7 |

|

|

0 |

1 |

c7 |

|

|

1 |

0 |

c7 |

|

|

1 |

1 |

c7 |

|

|

|

|

|

|

Схемная реализация сумматора с функцией (10) представлена на рис. 4.

Рис 4. Суммирование двух двоичных чисел с любыми знаками при представле-

нии отрицательных чисел в двоичном дополнительном коде

Как показывает сравнение с рис. 2.6, выражение (10) идентично сложе-

нию в полном сумматоре. Поэтому 8-разрядное число S8, включая знак, можно

11

вычислить с помощью 8-разрядного сумматора (рис. 5), не подвергая знаковый разряд какой-либо особенной обработке, если не возникает переполнения.

Рис 5. Включение логики определения знака суммы в арифметический блок

Определение переполнения

При суммировании двух чисел с одинаковыми знаками можно получать

неверный результат из-за выхода числа из допустимой области (переполнения разрядной сетки). Однако такая ошибка обнаруживается весьма просто. Если А и В положительны, то их сумма также положительна. Появление отрицатель-

ного знака |

v |

S |

означает положительное переполнение (OV ). Отсюда следует |

|

|

|

|

|

|

OV v |

v v . |

|||

|

A |

B |

S |

|

Если оба слагаемых отрицательны, результат также должен быть меньше

нуля. В этом случае появление положительного знака является критерием для

обнаружения отрицательного переполнения. Отсюда следует |

OV v |

v v . |

|

|

A B S |

Для любого переполнения на основании полученных выражений можно запи-

сать

OV OV OV v v v |

v v v . |

(11) |

A B S |

A B S |

|

12

Чтобы обнаружить возникновение неверного результата из-за переполне-

ния сумматора, можно дополнить его схему специальными цепями для вычис-

ления функции (11). Это предусмотрено во многих арифметических устрой-

ствах. Для обнаружения переполнения можно использовать сигнал переноса c8

и формировать сигнал переполнения в соответствии с формулой

OV c8 vS vA vB . |

(12) |

Эта формула может быть получена из соотношений |

ci 1 gi pici , где |

gi aibi , pi ai bi , а также (10) и (11).

Она реализуется на трех логических элементах ―Исключающее ИЛИ‖.

13

МЕТОДЫ ПОСТРОЕНИЯ СХЕМ УМНОЖЕНИЯ АРИФМЕТИЧЕСКИХ

УСТРОЙСТВ

Умножение двоичных чисел последовательным методом.

При выполнении многих арифметических действий возникает необходи-

мость сдвига двоичной информации на один несколько разрядов. Например,

умножению на 2 положительного числа, представленного в прямом двоичном коде, соответствует сдвиг на 1 позицию влево, делению на 2 – вправо. Обыч-

но такая операция проводится с помощью сдвиговых регистров (последова-

тельно включенных D-триггеров, входы синхронизации которых объединены).

В этом случае за каждый такт производится сдвиг на один разряд. Следова-

тельно, недостатком этой схемы является необходимость введения специально-

го программного управления, которое обеспечивало бы первоначальную за-

грузку информации в регистр, а затем ее сдвиг на требуемое число разрядов.

Время выполнения сдвига в регистре возрастает вместе с увеличением с коли-

чества позиций, на которое выполняется сдвиг.

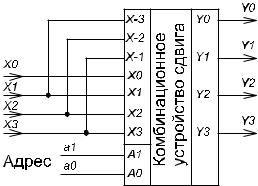

Эту же операцию можно провести и без такого управляющего устройства с помощью показанной на рис. 1 комбинационной схемы, собранной на муль-

типлексорах. Работа комбинационного устройства сдвига описывается табл. 1. Если адрес А = 002, то у3 = х3, у2 = х2, и т.д. Если адрес А= 012, то произойдет изменение в подключении выходов к выходам:

у3 = х2, у2 = х1, у1 = х0, у0 = х-1 .

14

Рис. 1 Комбинационное устройство сдвига на мультиплексорах

Таблица 1 Таблица изменения выходных сигналов комбинационного устройства сдвига

|

a1 |

a0 |

Y3 |

Y2 |

Y1 |

Y0 |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

X3 |

X2 |

X1 |

X0 |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

X2 |

X1 |

X0 |

X-1 |

|

|

|

|

|

|

|

|

|

|

1 |

0 |

X1 |

X0 |

X-1 |

X-2 |

|

|

|

|

|

|

|

|

|

|

1 |

1 |

X0 |

X-1 |

X-2 |

X-3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15

Следовательно, на выходе окажется двоичное число X, сдвинутое влево один разряд. Однако при этом, как и в обычном регистре сдвига, старший раз-

ряд этого числа пропадает. Если имеются мультиплексоры с N входами, то можно осуществить сдвиг числа на 0, 1, 2 ... (N – 1) разрядов. В примере,

представленном на рис. 1, N = 4. Чтобы не допустить потеря старшего бита,

можно нарастить устройство сдвига, подключив к нему последовательно еще одну такую же схему, как показано на рис. 2. В данном примере. N = 4; таким образом, здесь можно произвести сдвиг 5-разряднога числа X без потери ин-

формации максимум на три разряда. При этом число X установится на выходах от y3 до y7.

Схему на рис. 1 можно использовать также и в качестве кольцевого устройства сдвига; при этом входы расширения x–1 ÷ x–3 соединяются со вхо-

дами x1 ÷ x3, как показано на рис. 3.

Рис. 2 Расширенное комбинационное устройство сдвига

16

Рис. 3 Кольцевое комбинационное устройство сдвига

Рассмотрим приведенную в табл.3 схему перемножения двух двоичных чисел ―в столбик‖. В ней все вычисления выполняются достаточно просто, по-

скольку умножение производится только на единицу и нуль. Поэтому для вы-

числения произведения необходимо каждый раз сдвигать множимое на один разряд влево. Полученное в результате сдвига частное произведение прибавля-

ется к результату, если соответствующий данному шагу сдвига разряд множи-

теля равен единице. Если он равен нулю, то сложение не выполняется. Таким образом, в процессе умножения отдельные разряды множителя анализируются последовательно друг за другом, поэтому этот метод умножения называется последовательным.

Таблица 2 Схема умножения двоичных чисел ―в столбик‖

|

|

|

a3 |

a2 |

a1 |

|

|

|

b3 |

b2 |

b1 |

|

|

0 |

a3b1 |

a2b1 |

a1b1 |

|

c4 |

a3b1 |

a2b1 |

a1b1 |

|

|

a3b1 |

a2b1 |

a1b1 |

|

|

(m6) |

m5 |

m4 |

m3 |

m2 |

m1 |

Такую процедуру можно реализовать с помощью регистра сдвига и одно-

го сумматора. Однако в случае подобной схемы с памятью необходимо исполь-

зовать программное управление. Процесс сдвига можно также реализовать с помощью комбинационной схемы, аналогичной той, что показана на рис. 2, со-

17

единяя соответствующим образом N сумматоров. Хотя при этом требуется много сумматоров, нет необходимости в регистре сдвига и устройстве управле-

ния. Но основным преимуществом является сокращение времени операции, по-

скольку оно определяется уже не тактами управления, а лишь временем за-

держки логических элементов.

Матричные структуры для умножения двоичных чисел.

В современной цифровой технике для умножения двоичных чисел часто используются комбинационные схемы с матричной структурой, которая цели-

ком копирует схему математической записи процесса умножения ―в столбик‖.

Принципиальная схема перемножителя трехразрядных двоичных чисел показа-

на на рис. 4. В ней использовано девять одноразрядных перемножителей (логи-

ческая схема ―2И‖) и два трехразрядных сумматора. Сдвиг частных произведе-

ний осуществляется аппаратно, путем электрических соединений при монтаже электрической схемы. Максимальная разрядность произведения для этой схемы равна 6. В реальных схемах применяется необходимое количество соответ-

ствующим способом соединенных одноразрядных сумматоров, что позволяет реализовать устройство с применением несложных повторяемых элементов,

объединяемых в матричные структуры. Рассматриваемая схема легко поддается расширению при необходимости увеличения разрядности перемножаемых чи-

сел.

При перемножении чисел со знаком наиболее простым алгоритмом явля-

ется вычисление произведения модулей сомножителей, определение знака ре-

зультата и присваивание произведению установленного знака. Известны алго-

ритмы, позволяющие непосредственно перемножать числа в двоичном допол-

нительном коде, однако их применение существенных преимуществ (по време-

ни выполнения, или по простоте аппаратной реализации) не дает.

18

Рис. 4 Принципиальная схема перемножителя трехразрядных двоичных чисел

19

СПИСОК ЛИТЕРАТУРЫ

1.Титце, У. Полупроводниковая схемотехника: Справочное руководство. Пер. с

нем. – [текст] /У.Титце, К.Шенк/ – М.: Мир. - 1982. - 512 с.

2.Ашихмин А.С. Цифровая схемотехника. Современный подход. – [текст]

/А.С.Ашихмин/ – М.: ―ТехБук‖, 2007. – 288 с.

3. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства. Учеб. пособие для втузов. – [текст] / Г.И. Пухальский, Т.Я.Новосельцева / – СПб.: Политехни-

ка. 1996. 885 с.

4. Угрюмов Е.П. Цифровая схемотехника: Учеб. пособие для вузов. – 2-е изд.,

перераб. и доп. – [текст] /Е.П. Угрюмов / – СПб.: БХВ-Петербург, 2004. – 800 с.

5.Шило В.Л. Популярные цифровые микросхемы: Справочник. – – [текст] /В.Л. Шило/ – М.: Металлургия, 1988. 352 с. (МРБ, вып. 1111).

6.Хоровиц У., Хилл М. Искусство схемотехники. ч 1,2,3. – [текст] /У. Хоровиц,

М. Хилл / – М.: Мир, 1995.

20