- •Конспект лекций по курсу "аналоговая схемотехника"

- •Конспект лекций по курсу "аналоговая схемотехника"

- •1. Аналоговые ключи и коммутаторы

- •1.1. Ключ на полевом транзисторе с управляющим p-n - переходом

- •1.2. Аналоговые ключи на кмоп – транзисторах

- •1.3. Диодный коммутатор

- •1.4. Мультиплексоры аналоговых сигналов

- •1.5. Аналоговые коммутаторы на базе операционного усилителя

- •1.6. Контрольные вопросы

- •2. Компараторы сигналов

- •2.1. Простейшие компараторы

- •2.2. Компаратор с пос (триггер Шмидта)

- •2.3. Ограничение выходного напряжения

- •2.4. Компаратор с окном

- •2.5. Интегральные схемы компараторов

- •2.6. Контрольные вопросы

- •3. Схемы для измерительных систем

- •3.1. Схемы выборки - хранения

- •3.2. Точный выпрямитель

- •3.3. Увеличение выходного тока оу

- •3.4. Источники тока на оу

- •3.5. Источник тока на интегральной микросхеме lm117

- •3.6. Контрольные вопросы

- •4. Источники питания

- •4.1. Структурная схема источника питания

- •4.2. Стабилизаторы напряжения

- •4.3. Параметрические стабилизаторы

- •Контрольные вопросы

- •5. Компенсационные стабилизаторы с непрерывным регулированием

- •5.1. Общие положения

- •5.2. Работа компенсационного стабилизатора непрерывного действия

- •5.3. Составной транзистор

- •5.4. Расчет компенсационного стабилизатора напряжений непрерывного действия

- •5.5. Ограничение выходного тока стабилизатора

- •5.6. Контрольные вопросы

- •6. Схемы стабилизаторов компенсационного типа на интегральных схемах

- •6.1. Трехвыводные схемы стабилизаторов

- •6.2. Увеличение выходного тока стабилизатора.

- •6.3. Некоторые схемы стабилизаторов на интегральных схемах

- •Контрольные вопросы

- •Модуль № 2

- •7. Импульсные стабилизаторы

- •7.1. Общие положения

- •7.2. Вторичные импульсные стабилизаторы

- •7.3. Понижающий импульсный стабилизатор

- •7.4. Повышающий импульсный стабилизатор

- •7.5. Первичные импульсные стабилизаторы

- •7.6. Контрольные вопросы

- •8. Цифро-аналоговые преобразователи

- •8.1. Классификация цап

- •8.2. Последовательный цап с широтно-импульсной модуляцией

- •8.3. Последовательный цап на переключаемых конденсаторах

- •8.5. Цап на основе матрицы типа r – 2r

- •8.6. Построение цап с электронными ключами

- •8.7. Интерфейсы цап

- •8.8. Цап с последовательным интерфейсом входных данных

- •8.9. Цап с параллельным интерфейсом входных данных

- •Контрольные вопросы

- •9. Аналого-цифровые преобразователи

- •9.1. Общие сведения

- •9.2. Параллельные ацп

- •9.3. Последовательно – параллельный ацп

- •9.4. Ацп последовательного приближения

- •Интегрирующий ацп

- •9.6. Преобразователь напряжения - частота

- •9.7. Контрольные вопросы

- •10. Интерфейсы ацп

- •10.1. Способы организации ввода данных ацп в вычислительных системах

- •10.2. Ацп с параллельным интерфейсом выходных данных

- •10.3. Ацп с последовательным интерфейсом выходных данных

- •10.4. Системы ввода аналоговых сигналов и микроконверторы

- •10.5. Контрольные вопросы

- •11. Генераторы сигналов на оу

- •11.2. Генераторы колебаний прямоугольной формы

- •11.2. Генератор сигналов треугольной формы

- •11.3. Генератор синусоидальных сигналов с мостом Вина

- •11.4. Контрольные вопросы

- •Список использованной литературы

8.7. Интерфейсы цап

Важную часть цифро-аналогового преобразователя составляет цифровой интерфейс, т.е. схемы, обеспечивающие связь управляющих входов ключей с источниками цифровых сигналов. Структура цифрового интерфейса определяет способ подключения ЦАП к источнику входного кода, например, микропроцессору или микроконтроллеру. Свойства цифрового интерфейса непосредственно влияют и на форму кривой сигнала на выходе ЦАП. Так, неодновременность поступления битов входного слова на управляющие входы ключей преобразователя приводит к появлению узких выбросов, "иголок", в выходном сигнале при смене кода.

При управлении ЦАП от цифровых устройств с жесткой логикой управляющие входы ключей ЦАП могут быть непосредственно подключены к выходам цифровых устройств, поэтому во многих моделях ИМС ЦАП, особенно ранних (572ПА1, 594ПА1, 1108ПА1, AD565А и др.), сколь-нибудь существенная цифровая часть отсутствует. Если же ЦАП входит в состав микропроцессорной системы и получает входной код от шины данных, то он должен быть снабжен устройствами, позволяющими принимать входное слово от шины данных, коммутировать в соответствии с этим словом ключи ЦАП и хранить его до получения другого слова. Для управления процессом загрузки входного слова ЦАП должен иметь соответствующие управляющие входы и схему управления. В зависимости от способа загрузки входного слова в ЦАП различают преобразователи с последовательным и параллельным интерфейсами входных данных.

8.8. Цап с последовательным интерфейсом входных данных

Такой преобразователь содержит на кристалле помимо собственно ЦАП дополнительно также последовательный регистр загрузки, параллельный регистр хранения и управляющую логику (рис.8.8). Чаще всего используется трехпроводный интерфейс, который обеспечивает управление ЦА-преобразователем от SPI, QSPI, MICROWIRE интерфейсов процессоров. При активном уровне сигнала CS (в данном случае - нулевом) входное слово длины N (равной разрядности ЦАП) загружается по линии DI в регистр сдвига под управлением тактовой последовательности CLK. После окончания загрузки, выставив активный уровень на линию LD, входное слово записывают в регистр хранения, выходы которого непосредственно управляют ключами ЦАП. Для того, чтобы иметь возможность передавать по одной линии данных входные коды в несколько ЦАП, последний разряд регистра сдвига у многих моделей ЦАП с последовательным интерфейсом соединяется с выводом ИМС DO. Этот вывод подключается ко входу DI следующего ЦАП и т.д. Коды входных слов передаются, начиная с кода самого последнего преобразователя в этой цепочке.

В качестве примера на рис.8.8 представлена временная диаграмма, отражающая процесс загрузки входного слова в ЦАП AD7233.

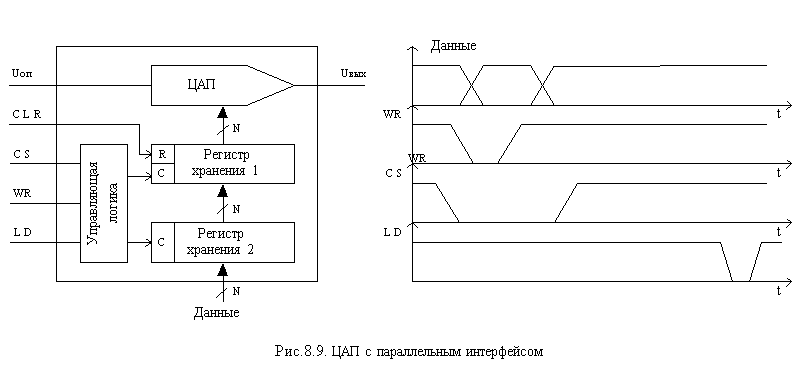

8.9. Цап с параллельным интерфейсом входных данных

Для более быстрой передачи данных в ЦАП используется параллельный интерфейс. В этом случае на N входов данных N-разрядного ЦАП подается все входное слово целиком. Интерфейс такого ЦАП включает два регистра хранения и схему управления (рис.8.9). Два регистра хранения нужны, если пересылка входного кода в ЦАП и установка выходного аналогового сигнала, соответствующего этому коду, должны быть разделены во времени. Подача на вход асинхронного сброса CLR сигнал низкого уровня приводит к обнулению первого регистра и, соответственно выходного напряжения ЦАП.