- •Конспект лекций по курсу "аналоговая схемотехника"

- •Конспект лекций по курсу "аналоговая схемотехника"

- •1. Аналоговые ключи и коммутаторы

- •1.1. Ключ на полевом транзисторе с управляющим p-n - переходом

- •1.2. Аналоговые ключи на кмоп – транзисторах

- •1.3. Диодный коммутатор

- •1.4. Мультиплексоры аналоговых сигналов

- •1.5. Аналоговые коммутаторы на базе операционного усилителя

- •1.6. Контрольные вопросы

- •2. Компараторы сигналов

- •2.1. Простейшие компараторы

- •2.2. Компаратор с пос (триггер Шмидта)

- •2.3. Ограничение выходного напряжения

- •2.4. Компаратор с окном

- •2.5. Интегральные схемы компараторов

- •2.6. Контрольные вопросы

- •3. Схемы для измерительных систем

- •3.1. Схемы выборки - хранения

- •3.2. Точный выпрямитель

- •3.3. Увеличение выходного тока оу

- •3.4. Источники тока на оу

- •3.5. Источник тока на интегральной микросхеме lm117

- •3.6. Контрольные вопросы

- •4. Источники питания

- •4.1. Структурная схема источника питания

- •4.2. Стабилизаторы напряжения

- •4.3. Параметрические стабилизаторы

- •Контрольные вопросы

- •5. Компенсационные стабилизаторы с непрерывным регулированием

- •5.1. Общие положения

- •5.2. Работа компенсационного стабилизатора непрерывного действия

- •5.3. Составной транзистор

- •5.4. Расчет компенсационного стабилизатора напряжений непрерывного действия

- •5.5. Ограничение выходного тока стабилизатора

- •5.6. Контрольные вопросы

- •6. Схемы стабилизаторов компенсационного типа на интегральных схемах

- •6.1. Трехвыводные схемы стабилизаторов

- •6.2. Увеличение выходного тока стабилизатора.

- •6.3. Некоторые схемы стабилизаторов на интегральных схемах

- •Контрольные вопросы

- •Модуль № 2

- •7. Импульсные стабилизаторы

- •7.1. Общие положения

- •7.2. Вторичные импульсные стабилизаторы

- •7.3. Понижающий импульсный стабилизатор

- •7.4. Повышающий импульсный стабилизатор

- •7.5. Первичные импульсные стабилизаторы

- •7.6. Контрольные вопросы

- •8. Цифро-аналоговые преобразователи

- •8.1. Классификация цап

- •8.2. Последовательный цап с широтно-импульсной модуляцией

- •8.3. Последовательный цап на переключаемых конденсаторах

- •8.5. Цап на основе матрицы типа r – 2r

- •8.6. Построение цап с электронными ключами

- •8.7. Интерфейсы цап

- •8.8. Цап с последовательным интерфейсом входных данных

- •8.9. Цап с параллельным интерфейсом входных данных

- •Контрольные вопросы

- •9. Аналого-цифровые преобразователи

- •9.1. Общие сведения

- •9.2. Параллельные ацп

- •9.3. Последовательно – параллельный ацп

- •9.4. Ацп последовательного приближения

- •Интегрирующий ацп

- •9.6. Преобразователь напряжения - частота

- •9.7. Контрольные вопросы

- •10. Интерфейсы ацп

- •10.1. Способы организации ввода данных ацп в вычислительных системах

- •10.2. Ацп с параллельным интерфейсом выходных данных

- •10.3. Ацп с последовательным интерфейсом выходных данных

- •10.4. Системы ввода аналоговых сигналов и микроконверторы

- •10.5. Контрольные вопросы

- •11. Генераторы сигналов на оу

- •11.2. Генераторы колебаний прямоугольной формы

- •11.2. Генератор сигналов треугольной формы

- •11.3. Генератор синусоидальных сигналов с мостом Вина

- •11.4. Контрольные вопросы

- •Список использованной литературы

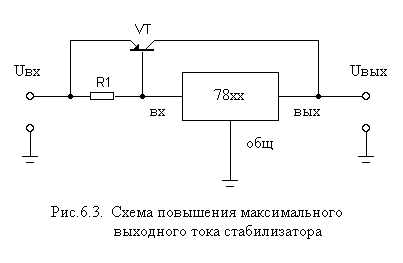

6.2. Увеличение выходного тока стабилизатора.

Д

ля

увеличения выходного тока стабилизатора

могут использоваться мощные внешние

проходные транзисторы [4], как показано

на рис.6.3. Внутренний выходной транзистор

стабилизатора с внешним проходным

транзистором образуют комплементарный

составной транзистор (внешний транзисторp-n-pтипа). На рис.6.3. показан пример схемы, в

которой выходной ток микросхемы

стабилизатора ограничивается максимальной

величиной в 100 мА. При токе нагрузки

меньше 100 мА внешний транзисторVTзакрыт (Uэб< 0,6 В)

и не оказывает влияния на работу схемы.

При больших токах нагрузки напряжение

на резистореR1 (R1=

6 Ом) повышается до 0,6 В, транзисторVTоткрывается и обеспечивает необходимый

ток нагрузки. При этом входной ток

микросхемы стабилизатора ограничивается

величиной 100 мА. Микросхема стабилизатора

поддерживает напряжение на выходе на

неизменном уровне, повышая или понижая

входной ток, т.е. ток через резисторR1

и тем самым, управляя током транзистораVT. Минимальная разность

между входным и выходным напряжением

должна быть равна допустимой разности

входного и выходного напряжения

микросхемы стабилизатора плюс напряжение

эмиттер-база транзистораVT.

ля

увеличения выходного тока стабилизатора

могут использоваться мощные внешние

проходные транзисторы [4], как показано

на рис.6.3. Внутренний выходной транзистор

стабилизатора с внешним проходным

транзистором образуют комплементарный

составной транзистор (внешний транзисторp-n-pтипа). На рис.6.3. показан пример схемы, в

которой выходной ток микросхемы

стабилизатора ограничивается максимальной

величиной в 100 мА. При токе нагрузки

меньше 100 мА внешний транзисторVTзакрыт (Uэб< 0,6 В)

и не оказывает влияния на работу схемы.

При больших токах нагрузки напряжение

на резистореR1 (R1=

6 Ом) повышается до 0,6 В, транзисторVTоткрывается и обеспечивает необходимый

ток нагрузки. При этом входной ток

микросхемы стабилизатора ограничивается

величиной 100 мА. Микросхема стабилизатора

поддерживает напряжение на выходе на

неизменном уровне, повышая или понижая

входной ток, т.е. ток через резисторR1

и тем самым, управляя током транзистораVT. Минимальная разность

между входным и выходным напряжением

должна быть равна допустимой разности

входного и выходного напряжения

микросхемы стабилизатора плюс напряжение

эмиттер-база транзистораVT.

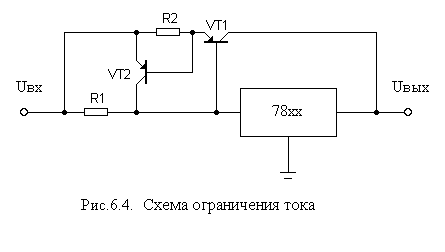

При коротком замыкании выхода стабилизатора сильно возрастает ток через внешний транзистор, что приводит к выходу его из строя. Поэтому необходимо ограничивать выходной ток. На рис.6.4 показана схема ограничения выходного тока на неизменном уровне. В этой схеме, когда ток транзистора VT1 превысит заданный уровень, напряжение на резистореR2 повышается до уровня отпирания транзистораVT2. Открывающийся транзисторVT2 понижает уровень управляющего напряженияUэб VТ1, тем самым, ограничивая его ток. Эта схема ограничения тока имеет те же недостатки, что и раннее рассмотренные схемы для стабилизаторов с ОУ. Это большая рассеиваемая мощность внешним транзистором и транзистор должен выдерживать большой ток, равный максимальному току стабилизатора, при большом перепаде напряженияUкэ.

Д ля

ограничения тока целесообразно применять

схему ограничения с изменяющимся уровнем

тока ограничения. В этой схеме происходит

уменьшение выходного тока при увеличении

перепада напряжений на проходном

транзисторе.

ля

ограничения тока целесообразно применять

схему ограничения с изменяющимся уровнем

тока ограничения. В этой схеме происходит

уменьшение выходного тока при увеличении

перепада напряжений на проходном

транзисторе.

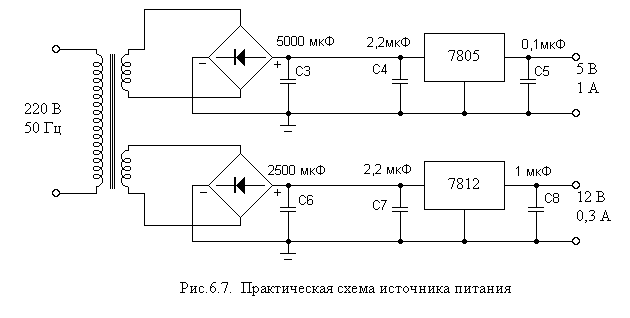

6.3. Некоторые схемы стабилизаторов на интегральных схемах

Д ля

получения отрицательных напряжений

могут использоваться стабилизаторы

на положительное напряжение, если

входное напряжение гальванически

изолировано от земли. Такая схема

показана на рис.6.5. Для получения

отрицательных напряжений могут

использоваться стабилизаторы

отрицательных напряжений. Одна из

возможных схем получения двух симметричных

напряжений показана на рис.6.6 [6]. В этой

схеме средняя точка трансформатора

подключена к земле и поэтому отрицательное

напряжение не может быть стабилизировано

схемой, приведенной на рис.6.5. В схеме

включены диоды, для предотвращения

выхода из строя стабилизаторов при

возможном изменении полярности напряжения

на выходе стабилизатора через сопротивление

нагрузки. Такая ситуация может возникнуть

при выходе из строя одного из стабилизаторов

или при появлении одного из питающих

напряжений раньше другого вследствие

различного сглаживания. На рис.6.7 показана

практическая схема источника питания.

ля

получения отрицательных напряжений

могут использоваться стабилизаторы

на положительное напряжение, если

входное напряжение гальванически

изолировано от земли. Такая схема

показана на рис.6.5. Для получения

отрицательных напряжений могут

использоваться стабилизаторы

отрицательных напряжений. Одна из

возможных схем получения двух симметричных

напряжений показана на рис.6.6 [6]. В этой

схеме средняя точка трансформатора

подключена к земле и поэтому отрицательное

напряжение не может быть стабилизировано

схемой, приведенной на рис.6.5. В схеме

включены диоды, для предотвращения

выхода из строя стабилизаторов при

возможном изменении полярности напряжения

на выходе стабилизатора через сопротивление

нагрузки. Такая ситуация может возникнуть

при выходе из строя одного из стабилизаторов

или при появлении одного из питающих

напряжений раньше другого вследствие

различного сглаживания. На рис.6.7 показана

практическая схема источника питания.

Рассмотренные схемы стабилизаторов напряжения далеко не исчерпывают всего многообразия микросхем стабилизаторов и их включений. Более подробную информацию можно получить в литературе и на сайтах производителей микросхем: NationalSemiconductors,Fairchild,Motorolaи др.