- •Презентация

- •КонспекТа лекций

- •По курсу «Элементы систем автоматики

- •Электроэнергетических систем»

- •Введение

- •2. Автоматическое повторное включение

- •Модуль 2

- •Метод точной синхронизации

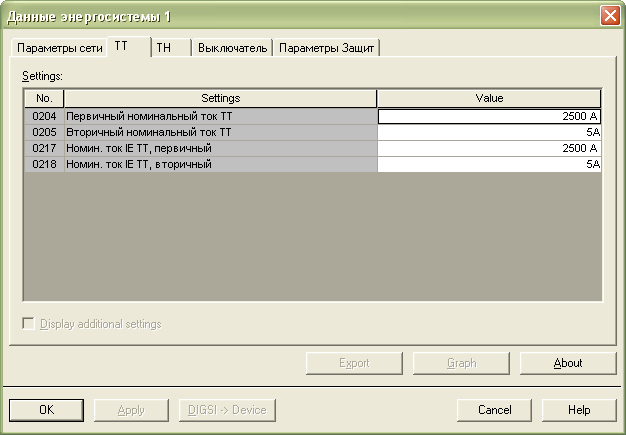

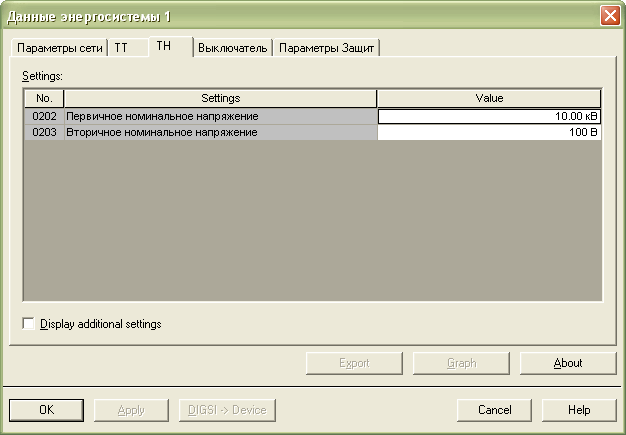

- •Задание параметров тт и тн:

- •Разработка Программного обеспечения (по)

- •Реализация терминалов на основе платформы х86

- •Принципиальная схема блоков выходных коммутаторов ком1 и ком2

- •3. Работа контроллера согласования пэвм с исполнительными реле

- •Разработка по при реализации терминалов на основе микроконтроллеров

- •Принципиальная схема микроконтроллера

- •Работа микроконтроллера с исполнительными реле

- •Програмирование на с

- •Разработка программного обеспечения на мк

- •Организация задержки по времени

- •Организация работы таймеров-счетчиков

- •Управление ацп

- •Программа мтз

- •Методы обработки смысловой информации

- •Дерево распознавания для алгоритма сп пззм-1м

- •Фаззи-логика

- •Нейронные сети

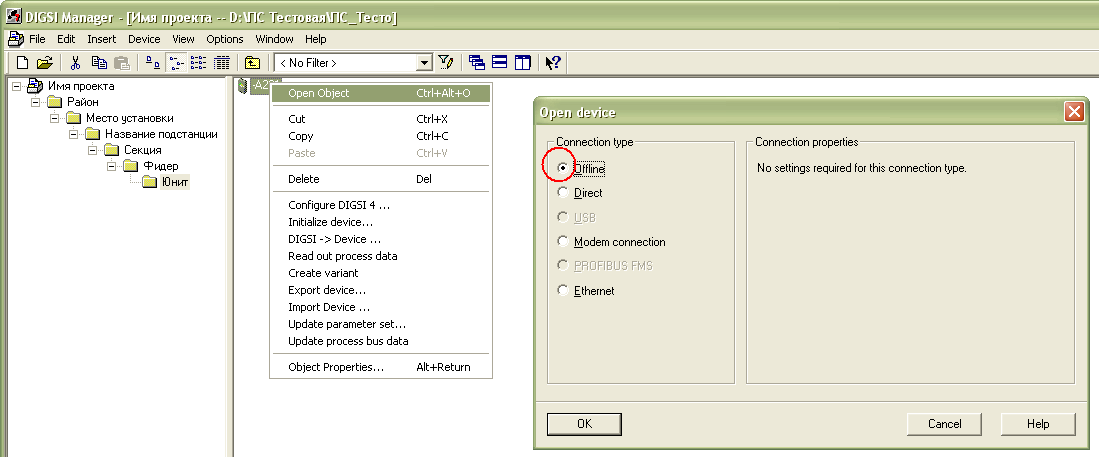

Задание параметров тт и тн:

Экспортировать (сохранить) конфигурацию устройства:

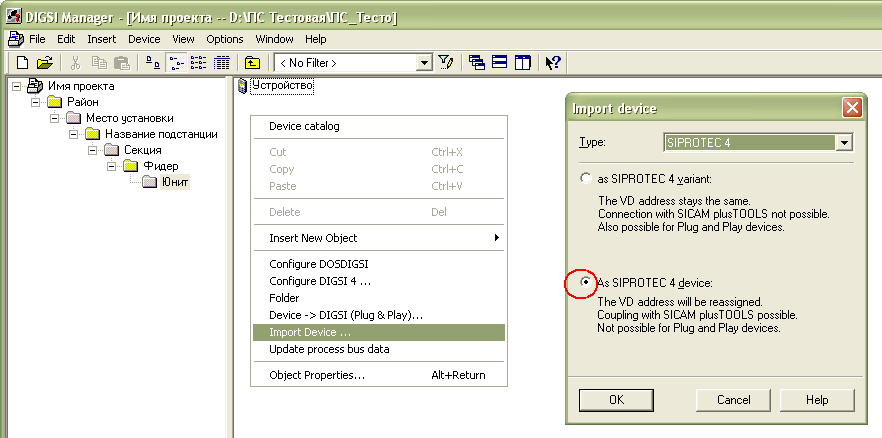

Импортировать (считать) конфигурацию устройства:

Загрузка конфигурации в устройство SIPROTEC:

Подключите устройство SIPROTEC 7SJ64 через COM-порт

Загрузите конфигурацию:

При

первой загрузке в устройство

При

последующих загрузках

ЛЕКЦИЯ. ШАГ РГР

Видео терминалы

Часть 2. Разработка программного обеспечения терминалов РЗиА

Терминал РЗиА представляет из себя три отдельных модуля в корпусе:

1) аналоговая плата; 2) цифровая плата; 3) плата индикации.

Входные цепи подготовки аналогового сигнала (измерительные усилители, источники опорного смещения для задания средней точки диапазона входного сигнала – референсное напряжение (высокой точности); задатчик диапазонов входных сигналов АЦП); выходные цепи (буферные элементе – усилители выходных сигналов для микропроцессоров). Большинство перечисленных цепей элементов включаются в состав микросхемы контроллера. Габариты входных цепей приводят к появлению отдельной аналоговой платы.

Цифровая плата – ее габариты обусловлены большим количеством выводов (локальные сети, порты ОЗУ, порты индикаторов).

Плата индикации имеет заводское изготовление, специальные модули (дисплей и т. д.)

В состав цифровой платы входят порты программирования (ITAG), порты локальных сетей.

Универсальные порты:

1) SPI; 2) MMC/SD;

3) USB; 4) ETHERNET;

5) USART (COM);

6)![]() c.Все порты работают при больших количествах

режимов.

c.Все порты работают при больших количествах

режимов.

Разработка Программного обеспечения (по)

Для индикации контрольных точек при отладке рабочей программы встраивается отдельный порт. DSB– аналог компорта.

Фирмами–изготовителями ПО выпускаются

САПР-ы (KEIL, IAR, PROTIUS, mC++).

Для каждого семейства МП контроллера необходим САПР.

Файл .hexзаписывается в память МП контроллера.

Реализация терминалов на основе платформы х86

Общие сведения

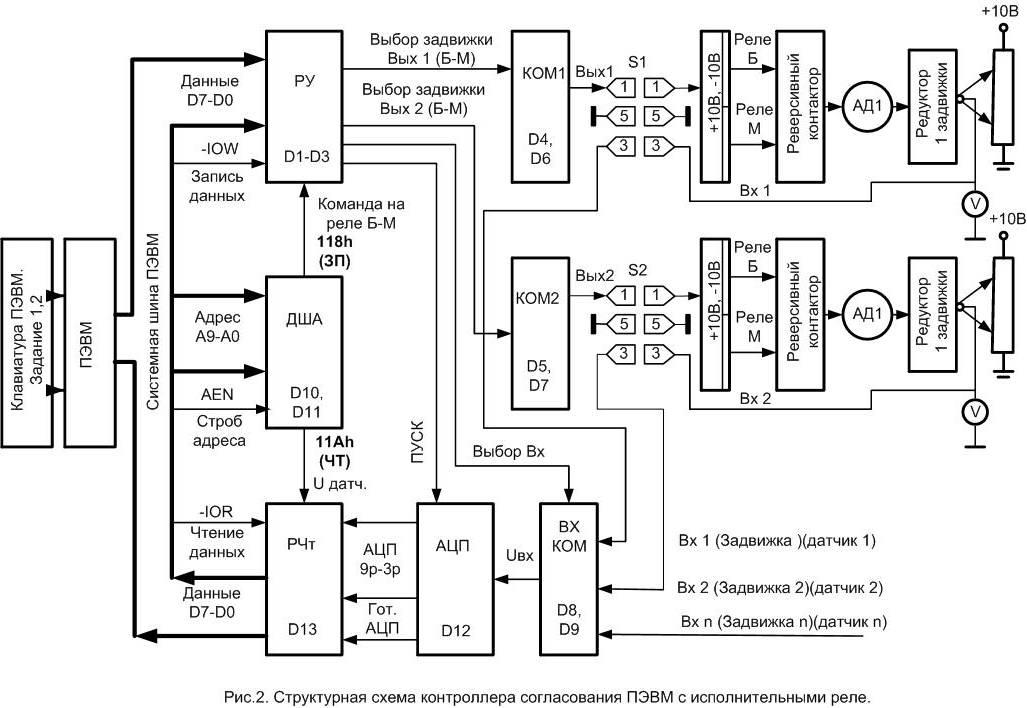

Контроллер согласования ПЭВМ с исполнительными реле представляет собой плату, которая вставляется в свободный разъем (слот) ПК, представляющий собой системную шину ПЭВМ. На плате контроллера крепится планка, на которую выведены два разъема типа DB15, обозначаемые на принципиальной схеме S1 и S2. К разъемам S1 и S2 осуществляется внешнее подключение входных сигналов и сигналов управления. Управление и работа контроллера согласования осуществляется под управлением программы, которая записана в ПЭВМ.

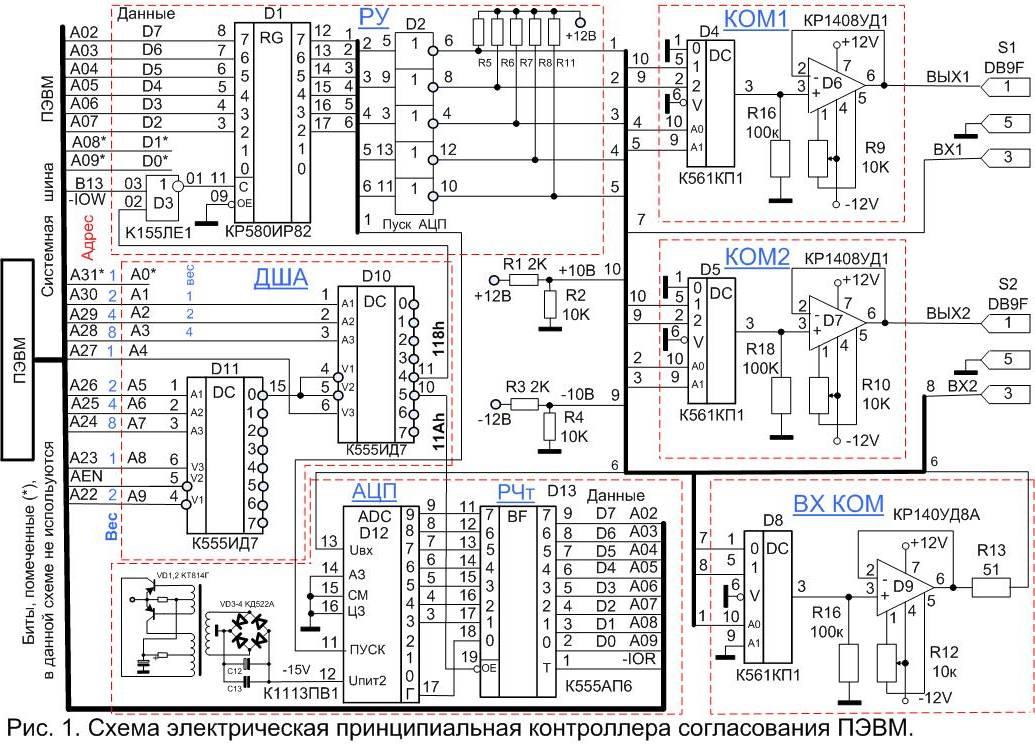

Принципиальная схема контроллера разделена на следующие блоки:

- блок дешифрации адреса ДША;

- блок регистра управления РУ;

- блок регистра чтения РЧт;

- блок аналого-цифрового преобразователя АЦП;

- блоки выходных коммутаторов КОМ1 и КОМ2;

-блок входного коммутатора ВХ КОМ.

Блок дешифрации адреса ДША представляет собой блок дешифрации адреса ПЭВМ. На вход ДША (рис. 5.1) подается 10-разрядный адрес А9-А0 из ПЭВМ, который стробируется сигналом AEN. ДША вырабатывает два сигнала:

118hв шестнадцатеричной системе счисления для записи данных;

11Аhв шестнадцатеричной системе счисления для чтения данных.

Блок регистра управления РУ представляет собой 8-ми разрядный регистр управления контроллером согласования ПЭВМ.

Информация из ПЭВМ в виде 8-ми разрядного кода записывается в блок РУ по адресу 118h, который выдается блоком дешифрации адреса ДША, и стробируется сигналом записи - IOW.

Блок РУ управляет:

коммутатором КОМ1;

коммутатором КОМ2;

коммутатором ВХ КОМ;

пуском АЦП.

Блок регистра чтения РЧт представляет собой 8-ми разрядный регистр чтения данных и готовности АЦП.

Информация из РЧт считывается в ПЭВМ по адресу 11Аh, который выдается блоком ДША, и стробируется сигналом чтения -IOR.

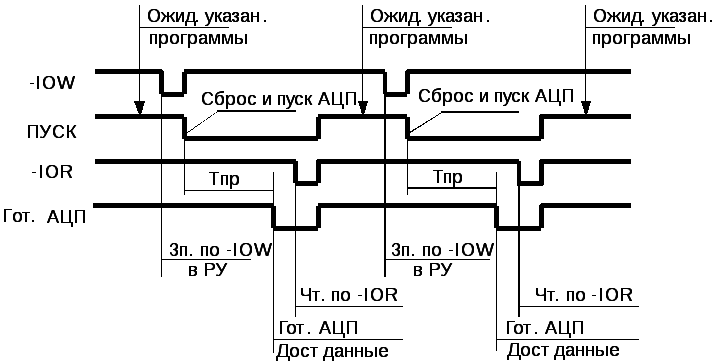

Блок аналого-цифрового преобразователя АЦП представляет собой собственно аналого-цифровой преобразователь, который преобразовывает аналоговый сигнала +0 - +10В (или -5В +5В) в цифровой код. Управление уровнем входного напряжения определяется входом СМ АЦП. Управление АЦП происходит по сигналу ПУСК, который поступает из РУ. После окончания преобразования АЦП выдает сигнал готовности Гот. АЦП. При этом на выходах АЦП D9-D0 устанавливаются достоверные данные.

Блок коммутатора КОМ1 представляет собой выходной коммутатор, который управляется сигналами “Выбор задвижки 1” Вых 1 блока РУ, и выдает на выход КОМ1 напряжение 0В, -10В, +10В.

Блок коммутатора КОМ2 представляет собой выходной коммутатор, который управляется сигналами “Выбор задвижки 1” Вых 2 блока РУ, и выдает на выход КОМ2 напряжение 0В, -10В, +10В.

Блок коммутатора ВХ КОМ представляет собой входной коммутатор, который управляется сигналом Выбор Вх блока РУ, и подает на вход АЦП напряжение 0V - +10V, поступающее на входы ВХ 1, ВХ2.

Принципиальная схема контроллера согласования ПЭВМ с исполнительными реле.

Принципиальная схема блока дешифрации адреса ДША.

Блок ДША выполнен на микросхемах (МС) D10, D11 (К555ИД7). Микросхемы D10, D11 анализируют адрес системной шины ISA и строб AEN. Дешифратор, в соответствии с таблицей истинности, при поступлении адреса 118h на МС D10, D11 формирует на выходе D10/11 логический «0». При адресе 11Аh соответственно на выходе D10/10 формирует логический «0».

Программа ПЭВМ готовит команду записи по адресу 28010 или 118h. По этой команде на системную шину ПЭВМ выставляется 10-ти разрядный адрес (А31-А22), который затем стробируется AEN из ПЭВМ. После дешифрации адреса на выходе D10/11 появится сигнал низкого уровня (логический «0»), который затем стробируется сигналом –IOW из ПЭВМ. В результате на выходе элемента D3/1 появится сигнал высокого уровня (логическая «1») по которому данные (D7-D0) из ПЭВМ (конт. системной шины А2-А9) записываются в регистр РУ (D1).

Программа ПЭВМ готовит адрес 11Ah для чтения данных с системной шины А02-А09. По этой команде на системную шину ПЭВМ выставляется 10-ти разрядный адрес А31-А22, который затем стробируется сигналом AEN из ПЭВМ. После дешифрации адреса и стробирования его сигналом AEN на выходе D10/10 появится сигнал низкого уровня (логический «0»), который разрешает совместно с сигналом (–IOR) чтение данных буфера в ПЭВМ.

Для получения достоверных данных АЦП на выходе буфера D13 необходимо проанализировать программно в ПЭВМ состояние нулевого разряда D13.

Таблица 5.1 – Адрес в 16сс читаем справа налево.

|

Конт шины адре-сов |

А31 |

А30 |

А29 |

А28 |

А27 |

А26 |

А25 |

А24 |

А23 |

А22 |

А11 |

|

|

А0 |

А1 |

А2 |

А3 |

А4 |

А5 |

А6 |

А7 |

А8 |

А9 |

AEN |

|

|

Не исп |

|

|

|

|

|

|

|

|

|

|

|

Вес разря-дов |

1 |

2 |

4 |

8 |

1 |

2 |

4 |

8 |

1 |

2 |

строб |

|

Двоич-ный код |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

--\_/-- |

|

Адрес шины в 16сс |

|

|

|

8 |

1 |

|

|

|

1 |

|

|

|

Двоич-ный код |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

--\_/-- |

|

Адрес шины в 16сс |

|

|

|

А |

1 |

|

|

|

1 |

|

|

|

Ножки микро- схемы |

|

D10/1 |

D10/2 |

D10/3 |

D10/6 |

D11/1 |

D11/2 |

D11/3 |

D11/6 |

D11/4 |

D11/5 |

После этого необходимо сделать цикл задержки считывания результатов АЦП, заведомо больший наименьшего времени работы АЦП (для АЦП К1113ПВ1 >> 30мкс). После чего, заведомо достоверное значение результатов работы АЦП, считать в ПЭВМ.

Принципиальная схема блока РУ

Блок РУ выполнен на микросхемах D1(КР580ИР82), D2(К155ЛН5) и D3 (К155ЛЕ1). Микросхема D1 представляет непосредственно сам регистр управления. Микросхема D3 организует строб записи данных в регистр D1(КР580ИР82). МС D2 служит для согласования уровней, так как управление адресными входами микросхем коммутаторов К561КП1 выполняется напряжением +12V. Резисторы R5-R8, R11 необходимы для установления уровней амплитудой +12V.

Таблица 5.2 – Назначение разрядов регистра РУ

-

Пуск АЦП

Разряды системной шины

А02

Разряды РУ

D7

Код

0

1

Назначение

Пуск АЦП

Сброс АЦП

Выбор канала АЦП ВХ КОМ

Разряды системной шины

А03

Разряды РУ

D6

Код

0

1

Назначение

Вх 2 канала

Вх 1 канала

Выбор напряжения на выходе КОМ 2

Разряды системной шины

А05-А04

Разряды РУ

D4-D5

Код

00

01

10

11

Назначение

не исп.

-10В

+10В

0В

Выбор напряжения на выходе КОМ 1

Разряды системной шины

А07-А06

Разряды РУ

D2-D3

Код

00

01

10

11

Назначение

не исп.

-10В

+10В

0В

Примечание:

А08 (D1) – не используется;

А09 (D0) – не используется.

2.3. Принципиальная схема блока РЧт

Блок РЧт выполнен на микросхеме D13(К555АП6). Микросхема D13 представляет непосредственно буфер для выходного регистра АЦП. При чтении по адресу 11Ah на входе микросхемы D13/19 появляется логический «0», который совместно со стробом чтения данных –IOR позволяет выдачу значения непосредственно АЦП и сигнала готовности Г (D12/17) на системную шину ПЭВМ.

Таблица 5.3 – Назначение разрядов регистра РЧт

-

Разряд АЦП

Разряд РЧт

Системная шина

9р.

D7

A02

8р.

D6

A03

7р.

D5

A04

6р.

D4

A05

5р.

D3

A06

4р.

D2

A07

3р.

D1

A08

Сигнал Гот. АЦП.

D0

A09

Принципиальная схема блока АЦП

Блок АЦП выполнен на микросхеме D12(К1113ПВ1 – функциональный аналог микросхемы AD571 фирмы ANALOG DEVICES (США)). Микросхема К1113ПВ1 представляет собой полупроводниковую БИС функционально завершенного аналого-цифрового преобразователя (АЦП) и предназначена для применения в электронной аппаратуре в составе блоков аналогового ввода. Микросхема выполняет функцию 10-разрядного аналого-цифрового преобразования однополярного (0 – +10,24В) или биполярного (-5,12В - +5,12В) входного сигнала с представлением результатов преобразования в параллельном двоичном коде.

Таблица 5.4 – Представление результатов преобразования в параллельном двоичном коде.

|

Однополярного входного напряжения 0 - +10,24В | ||||||||||

|

Uвх., В |

Двоичные разряды | |||||||||

|

|

Ст. р. 9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

Мл. р 0 |

|

Вес разряда |

512 |

256 |

128 |

64 |

32 |

16 |

8 |

4 |

2 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1,45 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

3,59 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

|

10,24 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Расчетная точность преобразования - 10,24В/1024(макс. двоичный код АЦП)=1/100В на разряд.

Для конкретных целей такая точность не требуется, поэтому на выходе АЦП используется только 7 старших разрядов. Отсюда точность преобразования станет меньше в 8 раз и будет равна 0,08В на разряд.

Питание микросхемы осуществляется от двух источников питания (+5В – вывод 10 МС и -15В – вывод 12 МС). Время преобразования Тпр. сигнала из аналогового в цифровой код равно 30мкс. Сброс АЦП происходит по значению логической «1» на входе D12/11, а запуск АЦП происходит по значению логического «0» на этом же входе. На вход D12/13 приходит входное напряжение от 0В до +10В. После запуска АЦП происходит аналого-цифровое преобразование в цифровой код, который выдается на выход АЦП через время Тпр. и поступает непосредственно на вход буфера D13.

Рисунок 5.3. Временная диаграмма чтения из буфера АЦП в ПЭВМ