2.ЦИФРОВІ ПРИСТРОЇ З ПАМ'ЯТТЮ

2.1.Теоретичні відомості і розрахункові співвідношення

Цифрові пристрої з пам'яттю відносяться до класу послідовнісних пристроїв в яких значення вихідних сигналів визначаються як значеннями вхідних сигналів в даний момент часу, так і передісторією зміни вхідних сигналів. Для цих пристроїв характерним є те, що при одних і тиx же значеннях вхідних сигналів вихідні сигнали можуть мати різні значення. До основних типів таких пристроїв відносяться трігери і більш складні пристрої, що реалізовуються на їх основі: ретистры, лічильники, розподільники, запам'ятовуючі пристрої та ін.

Тригери. До трігерів відноситься великий клас пристроїів загальною властивістю яких є здатність тривало залишатися в одному з двох можливих стійких станів і стрибком змінювати їх під впливом зовнішніх сигналів.

Тригери відрізняються великою різноманітністю типів і схемних рішень, визначуваних їх функціональним призначенням і способом запису в них інформації.

Функціональне призначення тригерів визначається залежністю значень їх виходів від значень вхідних сигналів. Як правило, тригер має два взаємоінверсних

виходи Q і P =Q і один або два інформаційні входи, що позначаються буквами Т або D

для одновходовых та R і S чи, J і K — для двохвходових тригерів Для тригера з одним входом, який може приймати два значення (0 і 1), і двома виходами, кожен з яких може

приймати п'ять значень (0, 1, Q, Q , ), принципово можливо отримати 52 різних типи

трігерів, з яких практичне застосування знайшли Т- і D трігери. Їх принцип роботи ілюструється таблицею переходів (табл. 2.1).

Табл. 2.1

Інфрмаційні |

Тип тригера і значення його |

||||

входи |

|

виходів Qt |

|||

D(T) |

D |

|

|

Т |

|

0 |

0 |

|

Qt−1 |

||

1 |

1 |

|

|

|

|

|

Q |

t−1 |

|||

Для тригера з двома входами і двома виходами можна отримати 54 різновидів трігерів, з яких практичне застосування знайшли RS, R, S-, Е-, JK трbгери, принцип роботи яких ілюструється таблицею переходів (табл 8 2)

Табл. 2.2

Інфрмаційні входи |

Тип тригера і значення його виходів Qt |

|||||

R(K) |

S(J) |

RS |

R |

S |

Е |

JK |

0 |

0 |

Qt−1 |

Qt−1 |

Qt−1 |

Qt−1 |

Qt−1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

Qt−1 |

Qt−1 |

Окрім перелічених інформаційних входів, трігери можуть мати входи керування, що визначають порядок перемикання тригера.

Bхід С називають синхронізуючім (тактувальним) або виконавчім входом дозволу приймання інформації, а вхід V — подготовчім входом дозволу приймання

інформації. Функціональна класифікація є найбільш загальною і характеризує стан входів і виходів тригера у момент часу до його спрацьовування і (t - 1) і після його спрацьовування (t).

Класифікація трігерів за способом запису інформації характеризує хід процесу перемикання тригера. За цією класифікацією трігери розділяють на асинхронні і синхронні. Запис інформації в асинхронні трігери здійснюється безпосередньо з надходженням інформаційних сигналів (такі трігери не мають тактуючих входів С) Синхронні трігери мають тактуючі входи, і перемикання трігера відбувається тільки за наявності відповідних сигналів на них. Якщо число цих входів m то формування нового стану тригера завершується після надходження m-го тактуючого сигналу. Найчастіше використовуються однотактні синхронні тригери, оскільки вони мають вищу швидкодію і не вимагають m-фазних генераторів тактуючих імпульсів. Такі тригери діляться на схеми, керовані рівнем тактового сигналу, і схеми з внутрішньою затримкою.

Трігери першого типу при появі тактуючого сигналу на вході С (С = 1) перемикаються відповідно до таблиці переходів стільки разів, скільки разів змінюються

інформаційні сигнали, тобто сигнали на виходах Q і Q трігерів можуть неодноразово

змінюватися, поки рівень тактуючого сигналу на вході С = 1. Їх також називають тригерами із статичним керуванням.

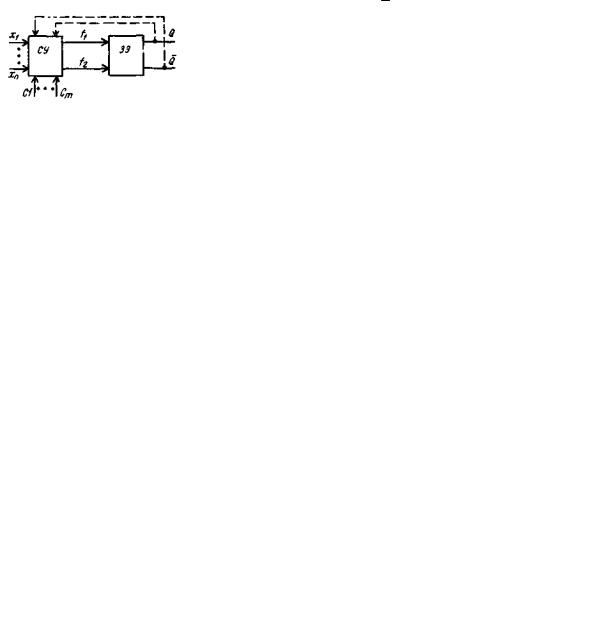

Узагальнена функціональна схема тригера із статичним керуванням приведена на рис. 2.1. Вона складається з запам'ятовуючого елементу ЗЕ (комірки пам’яті) і схеми керування СУ, х1, хn — інформаційні входи, С1, … Сn — тактуючі входи, f1 і f2 — функції збудження ЗЕ.

Рис. 2.1. Узагальнена функціональна схема тригера із статичним керуванням

У трігерах другого типу вихідні сигнали, відповідні новому стану трігера, з'являються тільки у момент переходу тактуючого сигналу з 0 в 1 (по передньому фронту) або, навпаки, з 1 в 0 (по задньому фронту). Такі тригери називаються також тригерами з динамічним керуванням. Їх відмінність полягає в тому, що від кожного тактуючого імпульсу незалежно від його тривалості і числа перемикань інформаційних сигналів протягом тактуючого імпульсу, вони перемикаються тільки один раз. Найширше на практиці застосовуються тригери з динамічним керуванням по задньому фронту тактуючого імпульсу, звані також трігерами з внутрішньою затримкою. Можливість затримки моменту перекидання тригера на якийсь час, рівне тривалості тактового імпульсу, ефективно використовується при обробці інформації, дозволяючи проводити по передньому фронту тактових імпульсів читання інформації, а по задньому фронту — запис.

На практиці використовують два основні способи побудови трігерів з внутрішньою затримкою по М - S-схемі і по схемі трьох трігерів.

Перший спосіб полягає у використанні для побудови тригера двох ЗЕ основного (М-тригера) і допоміжного (S-триггера), де М і S — абревіатури англійських слів master і slave (господар і раб, або ведучій і ведений). Узагальнена функціональна схема М - S- тригера приведена на рис. 2.2. Перший ступінь — «ведучий» — служить для проміжного запису інформації, а друга — «ведений» — для подальшого запам'ятовування і зберігання. Запис інформації в М-тригер тактується сигналом С, а в

S-триггер — сигналом F. Передача інформації з М-тригера в S-тригер здійснюється через вентилі В.

Рис. 2.2. Узагальнена функціональна схема М - S-тригера

Найбільше розповсюдження отримали М - S-тригери з інвертором в ланцюзі С і М - S-тригери із заборонними зв'язками. Їх схеми приведені на рис. 2.3, а і б відповідно Вони можуть бути реалізовані як на елементах І-НЕ, так і на елементах АБО-НЕ.

Рис. 2.3. Схеми М - S-тригера з інвертором в ланцюзі С (а) і М - S-тригери із заборонними зв'язками (б)

Другий спосіб ілюструється схемою (рис. 2.4), в якій перехід трігера в новий стан відбувається по передньому фронту тактуючого імпульсу. При С = 0 на виходах вентилів 4 і 5 присутній сигнал логічної 1 і тригер на елементах 1 і 2 не змінює свого стану, а вентилі 3 і 6 виконують функцію інвертора.

Хай, наприклад, f1 = 0, f2 = 1. Тоді при С = 1 на виході вентиля 4 з'являється сигнал 0, який встановлює основний тригер (вентилі 1 і 2) в одиничний стан і підтверджує одиничний сигнал на виході вентиля С. Після цього сигнали f1 і f2можуть змінювати своє значення, що не вплине на стан основного тригера до тих пір, поки не здійсниться черговий перехід сигналу С з 0 в 1.

Рис. 2.4. Узагальнена схема трьох тригерів

Властивості динамічних входів трігерів на електричних схемах позначають покажчиками (рис. 2.5), де на рис. 2.5, а показано прямий, а на рис. 2.5, б — інверсний динамічні входи.

Рис. 2.5. Покажчики пряммого (а) та інверсного (б) динаічних входів тригера

Синтез трігерів, виконаних на логічних елементах, може здійснюватися або в цілому по таблиці переходів конкретного трігера у поєднанні з його схемою керування, або роздільно для ЗЕ і СК. Другий шлях набув більшого поширення, оскільки як ЗЕ використовується, як правило, обмежений набір типових схем.

Синтез ЗЕ виконується по таблиці переходів конкретного тригера і полягає в отриманні логічного рівняння тригера і його функціональної схеми на заданій елементній базі, найчастіше І-НЕ чи АБО-НЕ. Повна таблиця переходів ЗЕ, який синтезується, включає як аргументи не тільки вхідні змінні, але і стан виходів у момент

часу (t −1). Так, повна таблиця переходів ЗЕ на асинхронному RS-тригерs приведена в табл. 2.3,

Табл. 2.3

S |

R |

Qt−1 |

Qt |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

I |

1 |

0 |

|

1 |

1 |

1 |

|

а рівняння його виходів, отримані по цій таблиці

Qt = S + RQt−1 , Qt = R + SQt−1 .

У системах АБО-НЕ та І-НЕ ці рівняння мають вигляд |

|||||||||||||||

Qt = R ↓ (S ↓Qt−1 ), |

Qt |

= |

|

|

| ( |

|

| Qt−1 ), |

||||||||

S |

R |

||||||||||||||

|

|

t = S ↓ (R ↓Q |

t−1 ); |

|

|

|

|

|

|

|

|

|

|

||

Q |

Q |

t |

= |

R |

| ( |

S |

| Q |

t−1 ); |

|||||||

Цим рівнянням відповідають функціональні схеми рис 2.6, а і б.

(2.1)

(2.2)

Рис. 2.6

Якщо в стовпці Qt таблиці переходів проектованого трігера є значення Qt−1

(наприклад, для T- або JK-трігерів), то як ЗЕ необхідно використовувати трігери з динамічними входами (внутрішньою затримкою). Це виключає багатократне перемикання трігера протягом тактового імпульсу.

При синтезі СК необхідно визначити, при яких значеннях f1 і f2 ЗЕ, виходи якого є виходами Q і Q триггера, здійснює певні переходи з одного стану в інший у момент спрацьовування трігера. Далі на підставі таблиці переходів трігера будується повна таблиця переходів, в якій відбиваються також значення Qt−1 у момент часу t - 1 і при

необхідності значення C. З повної таблиці переходів отримують вирази для f1 і f2, виконують мінімізацію отриманих функцій і реалізують їх на заданих елементах.

Як приклад розглянемо синтез JK-тригера на елементах І-НЕ. Оскільки в таблиці переходів JK-тригера має місце інверсія попереднього стану Qt−1 , то ЗЕ повинен мати

внутрішню затримку, тому вибираємо структуру тригера, представлену на рис. 1.3, а. У цій структурі ЗЕ на вентилях 1 і 2 є RS-тригером, порядок переходів якого залежно від значень f1 і f2 під час переходу тактуючого сигналу на вході С з 1 в 0 можна представити таким чином

з0 в0 при f1 |

=1, f |

2 |

=, |

|

|

з0 в1 при f1 |

= 0, f |

2 |

=1, |

(2.3) |

|

з1 в0 при f1 |

=1, f2 |

= 0, |

|||

|

|||||

з1 в1 при f1 |

= 0, f2 |

=1. |

|

||

Для даного тригера отримуємо повну таблицю переходів (табл. 2.4), побудовану відповідно до табл. 2.2.

Табл. 2.4

С |

|

t - 1 |

|

t |

f1 |

f2 |

|

J |

K |

Qt−1 |

Qt |

||||

|

|

|

|||||

0 |

0 |

0 |

0 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

1 |

|

1 |

|

0 |

0 |

1 |

0 |

0 |

I |

|

|

0 |

0 |

1 |

1 |

1 |

|

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

|

|

0 |

1 |

0 |

1 |

1 |

|

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

|

0 |

1 |

1 |

1 |

1 |

|

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

|

|

1 |

0 |

0 |

1 |

1 |

|

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

|

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

1 |

|

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

0 |

На підставі порядку переходів RS-триггера (2.3) заповнюємо в табл. 2.4 графи для f1 і f2, аналізуючі переходи Qt−1 в Qt в кожному рядку таблиці.

З табл. 2.4 отримуємо рівняння

f1 = C +Q + J , f2 =C +Q + K.

Далі перетворюємо їх в систему І-НЕ

f1 = C +Q + J = CQJ ,

f2 = C +Q + K = CQK.

Отримана схема тригера приведена на рис. 2.7

Рис. 2.7. Схема синтезованого тригера

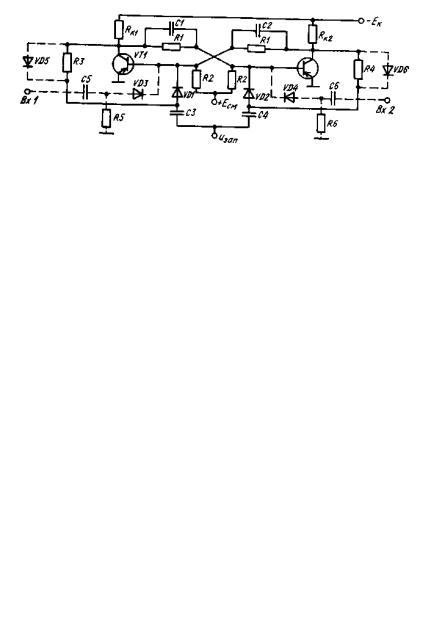

Тригери на дискретних елементах використовуються значно рідше і переважно в нестандартній апаратурі систем автоматичного керування і контролю виробничих процесів, в ядерній фізиці та інших областях, де потрібні підвищені значення напруг і струмів. Основною схемою є симетричний насичений тригер з колекторно-базовими зв'язками (рис. 2.8). Його основу складають два логічні інвертори (ключа), навантажених один на одного. Керування тригером здійснюється або роздільно (несиметрично) по двох базах або коллекторах (як і в RS-трігері) або симетрично (по лічильному входу) по базах або колекторах (як в Т-трігері). В цьому випадку для запобігання багатократному перемикання тригера протягом вхідного імпульсу вводиться затримка за допомогою прискорювальних конденсаторів С1, С2 в схемі з некерованим лічильним запуском або розділових конденсаторів С3, С4 в схемі з керованим лічильним запуском.

Рис. 2.8. Симетричний насичений тригер з колекторно-базовими зв'язками

Розрахунок тригера на транзисторах здійснюється з умов забезпечення закритого стану одного транзистора і відкритого стану іншого.

Умова закритого стану

Умова відкритого стану |

Eзс ≥ IK 0R2 |

|

(2.4) |

|||||

|

|

|

|

|

|

|

||

|

EK |

|

− |

EЗС |

≥ |

EK |

(2.5) |

|

|

|

|

βR |

|||||

|

R |

+ R1 |

|

R2 |

|

|||

|

K 2 |

|

|

|

|

|

K1 |

|

У схемах на кремнієвих транзисторах джерело зсуву може бути відсутнім, оскільки IK 0 ≈ 0 , а порогова напруга Uпор відмикання кремнієвих транзисторів істотно

більша, ніж у германієвих, тому умову закритого стану тригера на кремнієвих транзисторах можна записати

U 0 + IK 0 <Uпор ,

де U0 — напруга на насиченому транзисторі, яка відповідає напрузі логічного нуля. Умова лавиноподібного перемикання тригера має вигляд

K = |

β RK |

>1 |

(2.6) |

|

R1 + R |

||||

|

|

|

||

|

K |

|

|

Процес перемикання тригера складається з чотирьох етапів: розсмоктування (tроз)' підготовки (tп), регенерації (tрег) і встановлення (tвс)

|

|

|

|

|

tроз ≈τα (γ −1), |

|

|

(2.7) |

|||||

t |

п |

=τ |

|

|

|

UБЗ |

|

≈ (0,1...0,2)τ |

α |

, |

(2.8) |

||

|

|

|

|

||||||||||

α I |

m.зап |

|

R |

||||||||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

K |

|

|

|

|

|||

де UБЗ — напруга на базі закритого транзистора, Im.зап |

— амплітуда струму імпульсу |

запуску |

(2.9) |

tрег ≈τα |

Процес встановлення напруг відбувається одночасно і включає встановлення напруг на колекторах транзисторів, що закрилися і відкрилися, та на базі транзистора, що закрився. Тривалість встановлення напруги на колекторах транзисторів що закрився

tвс.з ≈ 3τзар ≈ 3С |

R1RK |

, |

(2.10) |

|

|||

що відкрився |

R1+ RK |

|

|

|

|

|

|

|

|

|

|

tвс.в ≈ 3 τC ln |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

, |

(2.11) |

|

|

|

|

|

|

|

|

|

τα |

|

|

|

|

1 |

|

|

|||||

|

|

|

|

1− |

|

|

|

|

|

|

|

|

||||||||

|

|

τ |

|

|

|

− |

U |

БЗ |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

C |

1 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

R1RK |

|

|

|

|

|

|

EK |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

де τ |

C |

= C |

≈C R ; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

R1 + RK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

на базі транзистора, що закрився |

|

|

R1R2 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

tвс.б ≈ 3C |

|

|

|

|

|

|

|

|

|

(2.12) |

||||||

|

|

|

|

|

R1 + R2 |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

Тривалість встановлення визначається більшою з тривалостей. Мінімально |

||||||||||||||||||

допустимий інтервал між імпульсами запуску визначає роздільну здатність тригера |

||||||||||||||||||||

|

|

|

|

tрозд = tроз +tп |

+tрег |

+tвс . |

|

|

(2.13) |

|||||||||||

|

|

Максимальна частота перемикагь тригера |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

F = |

|

|

1 |

. |

|

|

|

|

|

|

|

(2.14) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

max |

|

tрег |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Регістри. Регістри призначені для зберігання і перетворення багаторозрядних двійкових чисел. Вони є впорядкованою послідовністю тригерів і використовуються як пристрої, що керують і запам'ятовують, генератори і перетворювачі кодів, лічильники, дільники частоти, вузли тимчасової затримки і тому подібне.

Елементами структури регістрів є асинхронні і синхронні D-, RS- або JK-тригери з динамічним або статичним керуванням та допоміжні логічні елементи. Число розрядів в регістрі називається його довжиною. У n-розрядний регістр можна записати 2n розрядних слів, тобто регістр може знаходитися в 2n різних станах.

Занесення інформації в регістр називають операцією введення або запису. Видача інформації до зовнішніх пристроїв характеризує операцію виведення або читання.

Всі регістри залежно від функціональних властивостей підрозділяється на дві категорії: накопичувальні (регістри пам'яті, зберігання) і зсувні. У свою чергу зсувні регістри діляться:

за способом введення і виведення інформації на паралельні, послідовні і комбіновані (паралельно-послідовні і послідовно-паралельні).

по напрямком переди (зсуву) інформації на односпрямовані і реверсивні. Узагальнена функціональна схема регістра представлена на рис. 2.9. Вона

складається з тригерів ТТ і комбінаційної схеми КС. Входи y1…ym — сигнали мікрооперацій; xn і zn — інформаційні входи і виходи регістра; А і В — інформаційні входи тригерів; C — тактувальні входи.

Рис. 2.9. Узагальнена функціональна схема регістра

Найбільш поширеними мікроопераціями регістрів є:

1.Установка початкового стану (наприклад, нульового) — y1.

2.Прийом (запис) слова — y2.

3.Порозрядне логічне множення двох слів — y3.

4.Порозрядне логічне складання двох слів — y4.

5.Порозрядне додавання двох слів по модулю 2 — y5.

6.Зсув слова на j розрядів — y6.

7.Інвертування розрядів слова — y7.

8.Видача слова в прямому — y8, зворотному — y9, парафазному, — y10 кодах.

Мікрооперація y1 полягає у встановленні кожного розряду або в 0, або в 1. Для її виконання доцільно використовувати асинхронні R і S входи тригерів.

При виконанні операції y2 в і-й розряд регістра записується цифра хі, тобто

Qit = xi(t−1)

Для мікрооперацій y3, y4 і y5 можна записати відповідно

Qit =Qi(t−1) xi(t−1) ,

Qit =Qi(t−1) + xi(t−1),

Qit =Qi(t−1) xi(t−1)

Мікрооперація y6 може бути записана

Qit =Q(i− j)(t−1) ,

Qit =Q(i+ j)(t−1)

При виконанні мікрооперації y7, осуществтяется перетворення інформації в 1-му трігері відповідно до рівняння

Qit =Qi(t−1)

В процесі виконання мікрооперацій y8, y9 і y10 стан регістра не змінюється. Для видачі слова в прямому коді до виходів регістра підключаються прямі виходи тригерів

Qi, в зворотному — інверсні Qi , а при видачі в парафазному коді — і прямі, і інверсні

Синтез регістрів зводиться до вибору типу тригерів і синтезу КС, що формує функції збудження тригерів при виконанні заданих мікро операцій.

Лічильники Лічильником називається пристрій, сигнали на виході якого в певному коді відображають число імпульсів, що надійшли на його вхід. Число дозволених станів лічильника називають його модулем або коефіцієнтом лічби Kлч.

Основними часовими характеристиками лічильників є максимальна частота надходження рахункових імпульсів fлч і час переходу з одного стану в інший.

По характеру операцій лічби лічильники діляться на додавальні, віднімальні і реверсивні.

Залежно від основи системи числення, в якій здійснюється лічба, вони можуть бути двійковими, двійково-десятковими, двійково-п’ятірковими та ін.

За схемними ознаками лічильники можуть бути асинхронними і синхронними.

Уасинхронних лічильниках на тактові входи синхронних тригерів або на інформаційні входи асинхронних тригерів інформація надходить з виходів сусідніх тригерів, тому тригери в таких схемах спрацьовують не одночасно, а послідовно, один за одним. В синхронних лічильниках всі тригери перемикаються одночасно під дією загального синхронізуючого сигналу, що надходить на тактові входи всіх тригерів одночасно.

За способом організації ланцюгів перенесення вони діляться на схеми з послідовним, паралельним і груповим переносом.

Улічильниках з послідовним переносом перенесення в сусідній старший розряд формується тільки після перемикання тригера в попередньому розряді Їх швидкодія визначається сумою часів встановлення (затримки) тригерів всіх розрядів.

В лічильниках з паралельним переносом аргументами функції перенесень для кожного розряду є тільки сигнали на виходах тригерів відповідних розрядів, причому переноси для всіх розрядів лічильника формуються одночасно. Їх швидкодія визначається часом встановлення одного тригера і однієї комбінаційної схеми незалежно від числа розрядів лічильника.

Ланцюги наскрізного перенесення організовуються так, щоб функція перенесення і-го розряду лічильника була аргументом функції перенесення (і + 1)-го розряду. В цьому випадку сигнали переносів для кожного розряду формуються по черзі, починаючи з молодших розрядів лічильника. Лічильники з крізним перенесенням потребують меншого числа логічних елементів для організації ланцюгів переносу, але поступаються лічильникам з паралельним перенесенням в швидкодії. Їх швидкодія визначається у гіршому разі перемиканням n логічних схем в ланцюгах крізного переносу і одного тригера (n — число розрядів лічильника).

Улічильниках з груповим перенесенням розряди лічильника розбиваються на групи. В межах однієї групи зазвичай організовується паралельний перенос, а між групами — послідовний або наскрізний.

Якщо лічба виконується в канонічній двійковій системі числення (у однорідній позиційній двійковій системі числення з природним порядком ваг), то такий лічильник називається з природним порядком лічби. Коефіцієнт рахунку при цьому може бути

Kлч ≤ 2n , але незалежно від його значення лічба виконується від 0 до Kлч.

Якщо рахунок виконується в неканонічних системах (наприклад, символічних, з штучним порядком ваг та ін.), то порядок лічби вважається штучним (довільним).

У лічильниках Kлч ≠ 2n і довільним порядком лічби найчастіше застосовуються

схеми з примусовим нарахуванням і з початковим встановленням.

Найбільш простими є схеми лічильників з природним порядком лічби, побудовані на основі тригерів з лічильним входом (Т- і JК-тригерів).

Узагальнена функціональна схема синхронного лічильника на Т-тригерах приведена на рис. 2.10, де КС — комбінаційна схема, що формує сигнали переносів fi, які надходять на лічильні входи i-x тригерів. В JК-григгерах лічильні входи організовуються з'єднанням входів J і K. Для отримання T-тригера з синхронного D- тригера слід його інверсний вихід з'єднати з входом D, а як Т-вхід використовувати вхід з D-триггера.

Рис. 2.10. Узагальнена функціональна схема синхронного лічильника на Т-тригерах

Лічильники, виконані у вигляді окремих функціональних вузлів, є у складі багатьох серії мікросхем. Номенклатуру лічильників відрізняє велике різноманіття. Багато які з них мають універсальні властивості і дозволяють керувати коефіцієнтом і напрямом лічби, вводити до початку циклу початкове число, припиняти по команді лічбу, нарощувати число розрядів і тому подібне.

Проте, у ряді випадків, може виникнути необхідність в лічильнику з нетиповими характеристиками. Такі лічильники синтезуються з окремих тригерів і логічних елементів.