-

Анализ приоритетов обслуживания при введении аппаратной избыточности

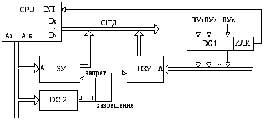

Рис. 19

Используется метод схемного последовательного опроса (см. рис. 19.). По данному методу предполагается, что имеется ряд внешних устройств, инициирующих запрос на прерывание. По каждому запросу предполагается своя подпрограмма обслуживания прерываний. Используемый микропроцессор имеет всего один вход INT (например, КР580ВМ80А). Схема работает следующим образом:

В исходном состоянии триггер Т сброшен, запросов от внешних устройств нет; счетчик СТ через дешифратор DС последовательно опрашивает запросные линии внешних устройств.

Поочередно формируется сигнал на логических элементах & сборки «И»-«ИЛИ». Сборка логических элементов И* закрыта, т.к. разрешающий сигнал «1» с системной шины данных отсутствует.

При появлении одного или нескольких запросов на прерывание от внешних устройств по первому из них срабатывает соответствующий элемент &, на выходе сборки «И»-«ИЛИ» появляется сигнал, поступающий на синхровход триггера. Триггер устанавливается в «1» и формирует запрос на прерывание микропроцессору. Этим же сигналом запрещается работа счетчика. На выходе счетчика фиксируется m-разрядный двоичный код, который соответствует номеру внешнего устройства, выставившего запрос на прерывание. Микропроцессор переходит на подпрограмму обработки прерываний. В этой подпрограмме обработки прерываний формируется сигнал разрешения («1») для сборки И*. Логические элементы & этой сборки открываются, код со счетчика поступает на системную шину данных, считывается микропроцессором, и является адресом перехода на подпрограмму обслуживания прерываний для данного внешнего устройства.

Режим последовательного программного опроса. В данном режиме микропроцессор с помощью контроллера прерываний последовательно опрашивает источники запросов многократной загрузкой операционного управляющего слова в контроллер прерываний (OCW3, код ОСН) командой OUT. Далее по команде IN микропроцессор читает системную шину данных. Переход в этот режим осуществляется, таким образом, программным путем. Контроллер прерываний, получив OCW3 от МП, выставляет на шину данных следующий шифр: это байт D7D6D5D4D3D2D1D0, в котором если D7=1, то запрос (INT) есть, биты D6D5D4D3 не анализируются, биты D2D1D0 указывают номер внешнего устройства с высшим приоритетом, которое нуждается в обслуживании. Во время опроса микропроцессором внешних устройств должны быть запрещены прерывания.

9)Передача вектора прерываний в МП (Intel 8080), который не обладает реакцией на векторные прерывания.

Простые микропроцессоры (INTEL 8080) не обладают способностью реагировать на векторное прерывание. Они имеют один вход INT и фиксированный адрес перехода на обслуживающую программу. Появление сигнала на входе INT вызывает передачу управления в фиксированную ячейку памяти с последующим сохранением служебной информации в стеке для возврата к прерванной программе. Предлагаемая схема (см. рис. 20.) позволяет повысить функциональные возможности микропроцессора до уровня, когда он способен различать запросы от внешних устройств и соответствующим образом реагировать на них.

Рис. 20

|

Х |

Код операции |

|

Х+1 |

А' |

А' – адрес перехода.

Таким образом, при получении хотя бы одного запроса от внешнего устройства, который поступает на вход приоритетного дешифратора DC1, на его выходе формируется сигнал запроса на прерывание для микропроцессора, который вызывает переход микропроцессора к фиксированной прерывающей подпрограмме.

В начале этой подпрограммы в ячейках Х и Х+1 записана двухбайтная команда передачи управления по адресу А'. При попытке выбора микропроцессором адреса А' из ячейки Х+1 происходит следующее: дешифратор DC2, обнаружив, что адрес на шине = Х+1, формирует на выходе сигнал, запрещающий работу основной памяти, и отключает ее от системной шины данных. Одновременно по этому же сигналу разрешается работа дополнительной памяти ПЗУ*, и происходит ее подключение к системной шине данных.

Поскольку дешифратор DC1 выбрал один из запросов от внешнего устройства, с его выхода на вход дополнительной памяти поступит соответствующий этому запросу код, который используется для формирования дополнительным ПЗУ адреса передачи управления.

Таким образом, микропроцессор, не подозревая о подлоге, отрабатывает процедуру перехода к программе, считав начальный адрес по шине данных, и ведет себя, по существу, также, как и при отработке векторных прерываний.