Регистры управления памятью (Регистры системных адресов)

В защищённом режиме процессор берёт информацию о сегментах памяти из дескрипторных таблиц глобальной (GDT) и локальной (LDT), но если положение LDT описано в одном из дескрипторовGDT, то положение самойGDTнеобходимо указывать иначе. Помимо этого в процессореi80286 появилась возможность размещать таблицу векторов прерываний в произвольном месте оперативной памяти, а не обязательно в самом начале, как в процессоре 8086. Это привело к необходимости добавить четыре регистра, указывающих положения структур данных, ответственных за сегментацию в защищенном режиме:

GDTR: 48‑битный (6‑байтный) регистр, в котором содержатся 32‑битный линейный адрес начала таблицы глобальных дескрипторов (GDT) и ее 16‑битный размер (минус 1).

Чтение – команда SGDT.

Запись – команда LGDT.

IDTR: 48‑битный (6‑байтный) регистр, в котором содержатся 32‑битный линейный адрес начала таблицы глобальных дескрипторов обработчиков прерываний (IDT) и ее 16‑битный размер (минус 1). Каждый раз, когда происходит прерывание или исключение, процессор передает управление на обработчик, описываемый дескриптором из IDT с соответствующим номером.

Чтение – команда SIDT.

Запись – команда LIDT.

LDTR: 80‑битный (10‑байтный) регистр, в видимой части которого содержится 16‑битный селектор для GDT (TIселектора равен 0), а в теневой весь 8‑байтный дескриптор из GDT, описывающий текущую таблицу локальных дескрипторов (LDT).

Чтение – команда SLDT.

Запись – команда LLDT.

TR: 80‑битный (10‑байтный) регистр, в видимой части которого содержится 16‑битный селектор для GDT (TIселектора равен 0), а в теневой весь 8‑байтный дескриптор из GDT, описывающий сегмент состояния текущей задачи – TSS (TaskStateSegment). Служит для организации многозадачной работы процессора в защищенном режиме.

Чтение – команда STR.

Запись – команда LTR.

Регистры управления процессором

Пять 32-битных регистров CR0 - CR4 – управляют функционированием процессора и работой отдельных его внутренних блоков.

Доступ к этим регистрам возможен с помощью обычной команды MOV.

Отладочные регистры

Восемь 32‑битных регистров DR0 - DR7 – предназначены для аппаратной отладки. Позволяют программам, выполняющимся на уровне привилегий 0, определять точки останова, не модифицируя код программ (например - для отладки программ, применяющих сложные схемы защиты от трассировки).

Доступ к этим регистрам возможен с помощью обычной команды MOV.

Система прерываний

Логическая организация системы прерываний

В архитектуре процессоров 80x86 предусмотрены особые ситуации, когда процессор прекращает (прерывает) выполнение текущей программы и немедленно передает управление программе‑обработчику, специально написанной для обработки этой конкретной ситуации. Такие особые ситуации делятся на три типа:

Исключения (внутренние прерывания процессора) – вызываются самим процессором и, в зависимости от того, когда по отношению к вызвавшей их команде они происходят, делятся на:

Ошибки – происходят перед выполнением команды, так что обработчик такого исключения получит в качестве адреса возврата адрес ошибочной команды

Ловушки – происходят сразу после выполнения команды, так что обработчик получает в качестве адреса возврата адрес следующей команды

Остановы – могут происходить в любой момент и вообще не предусматривать средств возврата управления в программу

Аппаратные прерывания – вызываются внешними по отношению к процессору устройствами и, в зависимости от того можно ли запретить прерывание программно через сброс флага IFделятся на:

Маскируемые – блокируются сбросом флага IF. Сигнал о них поступает процессору по входуINTR(или по шинеAPIC).

Немаскируемые – флаг IFна них не влияет.Делятся на:

Прерывания NMI(Non‑Maskable Interrupt) – собственно просто - “Немаскируемые прерывания”. Блокируются через порты ввода‑вывода 70h,A0hи 61h; источник прерывания можно узнать через порты 61hи 62h. Сигнал о них поступает процессору по входуNMI.

Прерывания SMI(System ManagementmodeInterrupt) – Прерывания режима системного управления. Имеют наивысший приоритет и не могут быть заблокированы операционной системой, сигнал о них поступает процессору по входуSMI. ОбработчикиSMI‑прерываний устанавливаютсяBIOS’ом при загрузке компьютера.

Программные прерывания – вызываются выполняющейся программой и по сути являются одним из способов вызова подпрограмм фактически вовсе не являясь прерываниями, делятся на:

Прерывания BIOS– обработчики и вектора этих прерываний устанавливаютсяBIOS’ом при загрузке компьютера.

Прерывания DOS– обработчики и вектора этих прерываний устанавливаются операционными системамиDOSиWindowsпри их загрузке. Для совместимости могут присутствовать и в других ОС.

Пользовательские прерывания – обработчики и вектора этих прерываний устанавливаются программистом по мере необходимости и им же удаляются.

Таблица векторов прерываний

Для того чтобы процессор, прервав текущую программу, мог выполнить программу‑обработчик прерывания ему необходимо знать адрес в оперативной памяти, на который нужно передать управление, и по которому, как правило, и располагается код обработчика – точку входа в обработчик.

В реальном режиме эти точки входа хранятся в виде четырёхбайтных дальних адресов (<селектор сегмента>:<смещение>) называемых векторами прерываний и хранящихся в виде таблицы векторов прерываний в первом килобайте оперативной памяти.

В защищённом режиме точки входа хранятся в виде восьмибайтных дескрипторов прерываний расположенных в глобальной дескрипторной таблице векторов прерываний, расположение которой определяется специальным регистром IDTR.

Аппаратные прерывания

Одна из важнейших концепций в вычислительной технике - это идея аппаратных прерываний. Аппаратные прерывания оптимизируют системную производительность, поскольку внешние устройства запрашивают ресурсы процессора только по мере необходимости их обслуживания. Если бы в системе не было аппаратных прерываний, процессору пришлось бы периодически опрашивать все устройства в системе, чтобы проверить, не нуждается ли в обслуживании какое-либо из этих устройств.

Аппаратные прерывания разбиты на два подкласса маскируемые и немаскируемые. Маскируемые прерывания можно заблокировать (замаскировать) путём сброса флага IFв регистре флагов процессора, но на немаскируемые прерывания этот флаг не влияет. Однако немаскируемыеNMI‑прерывания также могут быть заблокированы при помощи системных портов 70h,A0hи 61h, при этом источник вызвавшийNMI‑прерывание можно узнать через порты 61hи 62h.

Изначально вIBM PCдля подключения источников маскируемых прерываний предусматривалось восемь линий, обслуживаемых одним контроллером прерыванийPIC(ProgrammableInterruptionController), выполненном на микросхемеi8259A, но позднее к нему был каскадно подключён ещё один. Линии запроса прерываний обозначаются IRQ0‑IRQ15 (Interrupt ReQuest), причёмIRQ2 служит для каскадирования контроллеров и никаких других системных функций выполнять не может. Выход подсистемы контроллеров прерываний, через который ведущий контроллер сообщает процессору что произошло маскируемое прерывание, соединен со входом INTR микропроцессора.

В отличии от них запросы немаскируемых NMIиSMI‑прерываний поступают на специальные входы микропроцессора – NMI иSMIсоответственно.

Приоритет прерываний

Строго говоря, поскольку контроллеры прерываний являются программируемыми, – приоритеты обрабатываемых ими прерываний можно расположить произвольно, однако их приоритет всё же останется ниже немаскируемых. Однако при загрузке компьютера BIOSинициализирует контроллер прерываний в режиме с фиксированными приоритетами зависящими от номераIRQ. Обработчик аппаратного прерывания также можно вызвать и программно с помощью командыINT.

В отличии от маскируемых прерываний приоритет немаскируемых прерываний задан более жёстко. Они имеют более высокий по отношению к маскируемым прерываниям приоритет, а SMI‑прерывания и вовсе наивысший (настолько, что даже повторноеSMIпрерывание будет запрещено), поскольку одно из их предназначений – управление энергопотреблением, а также сохранение данных и системы при аварийных ситуациях.

При обработке SMI‑прерываний процессор переходит в специальный режим – режим управления системой илиSMM‑режим (System ManagementMode), сохраняя своё состояние не в стеке, а в специальной области оперативной памяти называемойSMRAM, всегда находящейся в пределах первых 4 GiB(232байт) физической памяти; выход из этого режима выполняется командойRSM.

Таблица 3: Аппаратные прерывания, расположенные в порядке убывания приоритета обслуживания в базовой конфигурации PC/AT.

|

|

Источник прерывания |

Вектор | |||||

|

Немаскируемые: | |||||||

|

SMI |

Микросхемы чипсета материнской платы |

| |||||

|

NMI |

Ошибки сопроцессора, деление на 0, ошибки памяти, недопустимая операция, и прочие критические события |

INT 02h | |||||

|

Маскируемые: | |||||||

|

Контроллеры прерываний |

|

| |||||

|

PIC2 (Ведомый) |

PIC1 (Ведущий) |

|

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

IRQ0 |

Системный таймер |

INT 08h | ||

|

|

|

|

IRQ1 |

Клавиатура |

INT 09h | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

IRQ2 |

Выход INTRведомого контроллера (PIC2) |

(INT 0Ah) | ||

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IRQ8 |

|

|

|

Часы реального времени (RTC/CMOS) |

INT 70h | ||

|

IRQ9 |

|

|

|

Видеоадаптер |

INT 0Ah/INT 71h | ||

|

IRQ10 |

|

|

|

Резерв пользователя |

INT 72h | ||

|

IRQ11 |

|

|

|

Резерв пользователя (Мышь PS/2) |

INT 73h | ||

|

IRQ12 |

|

|

|

Резерв пользователя |

INT 74h | ||

|

IRQ13 |

|

|

|

Сопроцессор |

INT 02h/INT 75h | ||

|

IRQ14 |

|

|

|

НЖМД №1 |

INT 76h | ||

|

IRQ15 |

|

|

|

Резерв пользователя (НЖМД №2) |

INT 77h | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IRQ3 |

Последовательный порт RS232C №2(COM2) |

INT 0Bh | ||

|

|

|

|

IRQ4 |

Последовательный порт RS232C №1 (COM1) |

INT 0Ch | ||

|

|

|

|

IRQ5 |

Параллельный порт №2(LPT2) |

INT 0Dh | ||

|

|

|

|

IRQ6 |

НГМД |

INT 0Eh | ||

|

|

|

|

IRQ7 |

Параллельный порт №1(LPT1) |

INT 0Fh | ||

Программные прерывания

Программные прерывания в отличие от аппаратных прерываний не привязаны к конкретным аппаратным ресурсам и иногда рассматриваются системными программистами как вызовы подпрограмм. Программное прерывание вызывается командой INT NNh, гдеNNh – шестнадцатеричное число от 00h до FFh, указывающее на номер вектора прерывания.

Программные прерывания включают в себя три уровня: BIOS‑прерывания, DOS‑прерывания и пользовательские прерывания. Одно из главных назначений BIOS‑прерываний - обеспечение корректного (с точки зрения совместимости) доступа к аппаратуре со стороны операционной системы и пользовательской программы. Роль DOS-прерывания заключается в обеспечении доступа пользовательских программ к системным ресурсам. Пользовательские прерывания - это такие прерывания, которые нужны пользователю для создания собственных обработчиков прерываний и не используют никакие из существующих векторов прерываний DOS за исключением официально разрешенных: с INT 60h по INT 67h.

Этапы обработки прерывания

Прежде чем процессор сможет начать обработку прерывания он должен выполнить ряд действий необходимых для корректной передачи управления обработчику, собственно обработки прерывания и последующего возврата управления из обработчика в текущую программу после его завершения.

Таблица 4: Последовательность действий по обработке запроса на прерывание по сигналам INTR, NMI или по команде INT n, выполняемая микропроцессором.

|

Маскируемые (INTR) |

Немаскируемые (NMI) |

Программные (INT NNh) |

|

Получить номер вектора из контроллера прерываний |

Вектор 02h |

Вектор NNh |

|

Сохранить регистр флажков в стеке. | ||

|

Сохранить CS в стеке. | ||

|

Сохранить IP в стеке. | ||

|

Сбросить IF. | ||

|

|

Запретить NMI. |

|

|

Прочитать вектор прерывания. | ||

|

Поместить селектор в CS и смещение в IP. | ||

|

Начать выполнение команд во входной точке (CS:IP). | ||

После обработки прерывания процессору необходимо восстановить предыдущее состояние сохранённое в стеке и передать управление на команду перед которой произошло прерывание.

Аппаратная реализация системы обработки прерываний

В архитектуре PC/AT подсистема аппаратных прерываний состояла из двух контроллеров i8259А (главного - MASTER и подчиненного - SLAVE). Они были объединены таким образом, что могли обслужить 15 запросов на прерывания, часть из которых использовалась платами расширения на шинеISA. Но с появлением в компьютерах на базе процессораi80486 шиныPCI, платы расширения для которой могут содержать несколько устройств, а позднее и многопроцессорных систем, в которых разные прерывания могут обслуживать разные процессоры, систему обработки прерываний пришлось изменить.

В IBM PC‑совместимых компьютерах применяется два основных типа контроллеров прерываний:

PIC (Peripheral/ProgrammableInterrupt Controller) – периферийный программируемый контроллер прерываний

APIC (Advanced Peripheral Interrupt Controller) – усовершенствованный периферийный контроллер прерываний, введенный для поддержки мультипроцессорных систем и увеличения числа доступных линий прерываний.

PIC‑контроллер

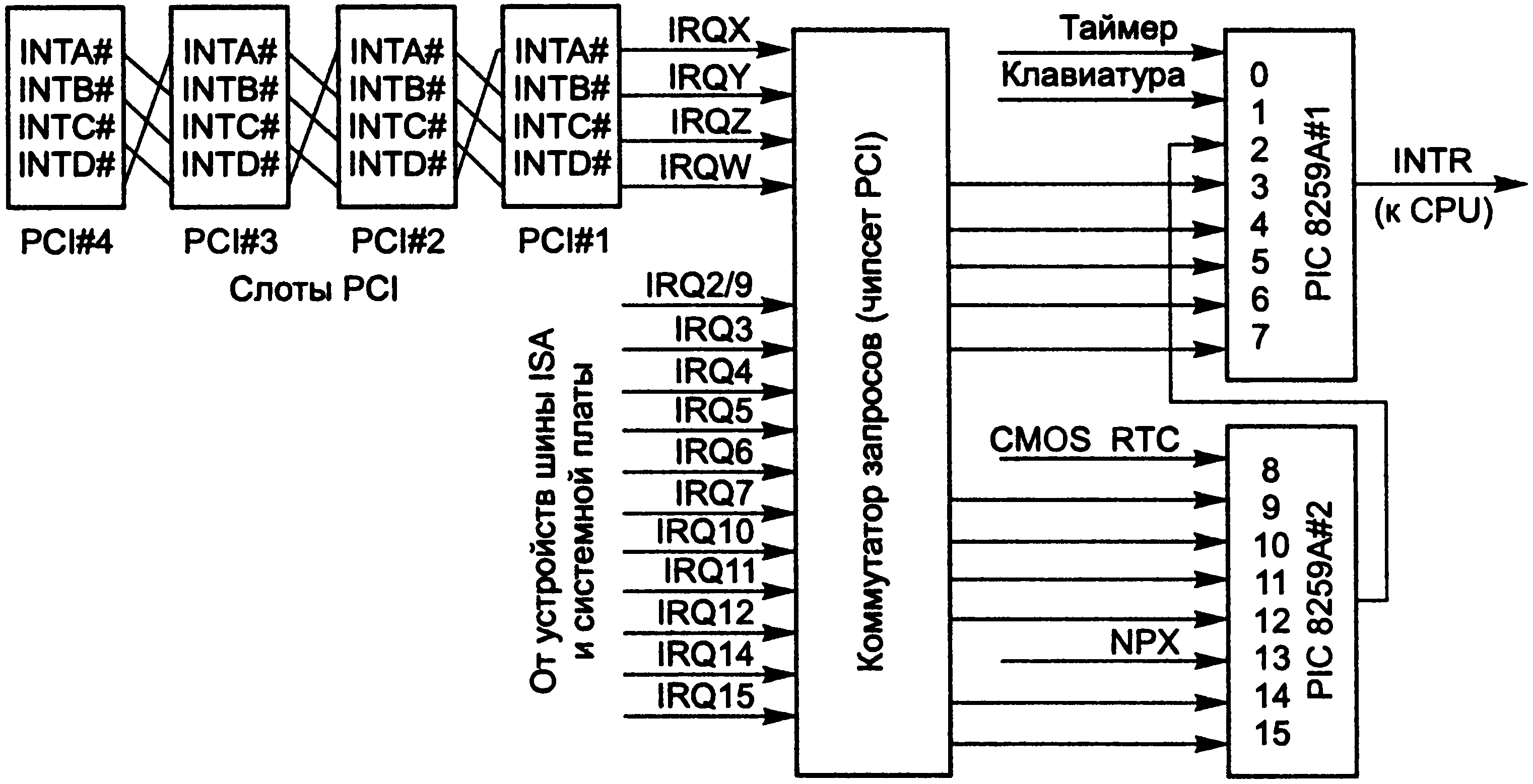

Рисунок 6: Традиционная схема коммутации запросов прерываний

Платы расширения для шины PCIмогут использовать одновременно до четырёх линий аппаратных запросов прерываний. Но если устройству требуется только одна линия запроса, то оно должно занимать линию INTA#, если две - INTA# и INTB#, и т. д. это правило позволяет установить в 4 соседних слота 4 простых устройства, и каждое из них будет занимать отдельную линию запроса прерывания. Порт AGP в плане прерываний следует рассматривать наравне со слотом PCI.

APIC‑контроллер

APICсостоит из модуля, встроенного в сам процессор (в случае многоядерной системы – в каждое ядро), называемого локальный контроллер прерываний (Local APIC), и центрального модуля, выполненного в одном экземпляре даже на многоядерном оборудовании, обычно как часть микросхем обрамления процессора (I/O APIC), которые связаны друг с другом специальным трёхпроводным интерфейсом. Проводники IRQ от устройств подсоединены к I/O APIC, но помимо маскируемыхAPICобрабатывает также и запросы на немаскируемые прерывания (в том числе иSMI‑прерывания). Он также может обрабатывать запросы прерываний от устройств PCI, посылаемые через механизм сообщений (MSI –MessageSignaledInterrupts) и имеет возможность функционировать в режиме, совместимом со стандартной связкой пары PIC‑контроллеров.