Рисунки к конспектам (11.10.10)

.docРисунки и таблицы к конспектам лекций по дисциплине «ЦиМПУ»

Содержание

«АРИФМЕТИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ» 5

Таблица 1 – Представление десятичных чисел в позиционных СС 5

Рисунок 1 – Область представляемых чисел с фиксированной точкой 5

Таблица 2 – Символьный код КОИ-7 6

«ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ» 6

Таблица 3 – Таблица истинности для элементарных логических функций одного аргумента 6

Таблица 4 – Таблица истинности для элементарных логических функций двух аргументов 7

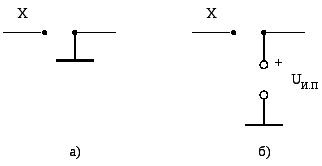

Рисунок 2 – Реализация элементарных логических функций одного аргумента (а) и (б) 7

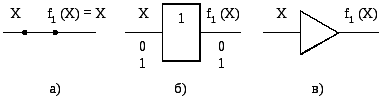

Рисунок 3 – Реализация элементарной логической функции (а) и условное графическое обозначение повторителя (б и в) 7

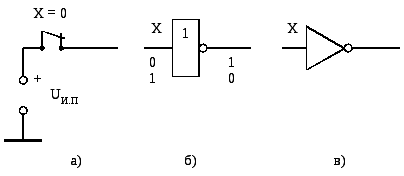

Рисунок 4 – Реализация элементарной логической функции (а) и условное графическое обозначение инвертора (б и в) 8

Таблица 5 – Полная совокупность элементарных логических функций двух аргументов 9

Продолжение таблицы 5 11

Продолжение таблицы 5 13

Продолжение таблицы 5 15

Окончание таблицы 5 16

Рисунок 5 – Логическая схема устройства 18

Рисунок 6 – Реализация на основе логических элементов И‑НЕ логических элементов НЕ (а) и И (б) 18

Рисунок 7 – Реализация на основе логических элементов ИЛИ‑НЕ логических элементов НЕ (а) и ИЛИ (б) 19

Рисунок 8 – Логическая схема устройства в базисе И-НЕ 19

Рисунок 9 – Логическая схема устройства в базисе ИЛИ-НЕ 20

«СХЕМОТЕХНИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ» 20

Рисунок 10 – Временные диаграммы физического представления кодового слова 10110 потенциальным способом (а), импульсным (б) и динамическим (в) 20

Рисунок 11 – Условное обозначение микросхемы 1533ЛА3 21

Таблица 6 – Обозначение цифровых ИС для подгруппы логических элементов 21

Рисунок 12 – Условное графическое обозначение расширителя (а), логического элемента 2И-2ИЛИ-НЕ/2И-2ИЛИ с возможностью расширения по ИЛИ (б) и логического элемента 3ИЛИ-НЕ/3ИЛИ (в) 22

Рисунок 13 – Направление выходных и входных токов при высоком уровне выходного напряжения (а) и низком уровне – (б) 22

Окончание рисунка 13 23

Рисунок 14 – Типовая передаточная характеристика инвертора 23

Рисунок 15 – Временные диаграммы входного и выходного напряжений при переключении инвертирующего логического элемента 24

Рисунок 16 – Схемы логических выходов цифровых элементов схемотехники ТТЛШ (а) и КМОП (б) 24

Рисунок 17 – Временная диаграмма тока, потребляемого цифровым элементом при переключении из одного логического состояния в другое 25

Рисунок 18 – Инвертор схемотехники КМОП с тремя состояниями выхода. Принципиальная схема (а) и условное графическое обозначение (б) 25

Рисунок 19 – Схемы выходов цифровых элементов с открытым коллектором (стоком) схемотехники ТТЛШ (а) и схемотехники КМОП (б) 26

Рисунок 20 – Схема реализации монтажной логики (а) и индикации уровня логической единицы (б) и уровня логического нуля (в) с помощью логических элементов с открытым коллектором (стоком) 26

Рисунок 21 – Схема наращивания числа входов для логических элементов И (а) и ИЛИ (б) 27

Рисунок 22 – Схема наращивания числа входов для логических элементов И-НЕ (а) и ИЛИ-НЕ (б) 27

Рисунок 23 – Схема снижения нагрузки на выходах логических элементов с помощью буферных элементов (а) и путем разделения нагрузки (б) 28

Рисунок 24 – Схема входной цепи элемента схемотехники КМОП с подтягивающим (а) и заземляющим (б) резисторами 28

Окончание рисунка 24 29

«АНАЛИЗ И СИНТЕЗ КЦУ» 29

Таблица 7 – Таблица истинности для логической функции трех аргументов 29

Рисунок 25 – Карты Карно для логических функций трех (а) и четырех (б) аргументов 30

Таблица 8 – Таблица истинности для логической функции трех аргументов 30

Рисунок 26 – Карта Карно для логической функции трех аргументов, функционирование которой задано таблицей 8 31

Рисунок 27 – Карта Карно и результат минимизации к примеру 1 31

Рисунок 28 – Карта Карно и результат минимизации к примеру 2 31

Рисунок 29 – Карта Карно и результат минимизации к примеру 3 32

Рисунок 30 – Карта Карно и результат минимизации к примеру 4 32

Рисунок 31 – Карта Карно и результат минимизации к примеру 5 32

Рисунок 32 – Карта Карно и результат минимизации к примеру 6 33

Рисунок 33 – Карта Карно для не полностью заданной логической функции 33

Рисунок 34 – Варианты минимизации не полностью заданной логической функции 33

Окончание рисунка 34 34

«ОБЩИЕ СВЕДЕНИЯ О МИКРОПРОЦЕССОРАХ» 35

Рисунок 1 – Классификация МП БИС 35

Рисунок 2 – Общая структурная схема микропроцессора 36

Рисунок 3 – Структурная схема МП со схемной логикой управления 36

Рисунок 4 – Структурная схема МП с программируемой логикой управления 37

Рисунок 5 – Структурная схема УУ МП с программируемой логикой управления 37

Рисунок 6 – Временная диаграмма работы МП 38

Рисунок 7 – Структура микропроцессорной системы 38

«ПРИНЦИПЫ ОРГАНИЗАЦИИ МПС НА ОСНОВЕ ОДНОКРИСТАЛЬНОГО МИКРОПРОЦЕССОРА» 39

Рисунок 1 – Структура микропроцессора К1821ВМ85А 39

Таблица 1 – Значения сигналов состояния и управления для различных машинных циклов 40

Рисунок 2 – Внешние элементы тактового генератора (а) и формирование синхросигналов (б) в микропроцессоре К1821ВМ85А 40

Рисунок 3 – Циклы и такты микропроцессора К1821ВМ85А (а) и пример размещения команды в памяти микропроцессорной системы (б) 41

Таблица 2 – Адреса регистров и регистровых пар МП К1821ВМ85А 41

Рисунок 4 – Временные диаграммы цикла чтения микропроцессора К1821ВМ85А 41

Рисунок 5 – Аппаратная реализация пересылки байта при выполнении операции рестарта 42

Таблица 3 – Описание разрядов регистра-аккумулятора при последовательном выводе 42

Таблица 4 – Описание разрядов регистра-аккумулятора при последовательном вводе 43

Таблица 5 – Система команд МП К1821ВМ85А 43

Продолжение таблицы 5 44

Продолжение таблицы 5 45

Продолжение таблицы 5 46

Продолжение таблицы 5 47

Окончание таблицы 5 48

Таблица 6 – Коды условий для команд управления 49

Рисунок 6 – Формат регистра флажков RF 49

Рисунок 7 – Схемы, поясняющие выполнение сдвигов микропроцессором 49

«ПРОГРАММИРОВАНИЕ МП» 50

Рисунок 15 – Схема алгоритма инвертирования содержимого ЯП 50

Таблица 7 – Программа инвертирования содержимого ЯП на языке Ассемблера при использовании прямой адресации 50

Таблица 8 – Программа инвертирования содержимого ЯП на языке Ассемблера при использовании косвенной регистровой адресации 50

Рисунок 16 – Схема алгоритма циклической программы суммирования однобайтных чисел 52

Таблица 9 – Циклическая программа суммирования однобайтных чисел на языке Ассемблера 53

Таблица 10 – Программа суммирования массива однобайтных чисел на языке Ассемблера, содержащая подпрограмму 53

54

Рисунок 1 – Структурная схема микроконтроллера PIC16F84 54

Рисунок 2 – Условное графическое обозначение микроконтроллера PIC16F84 55

Таблица 1 – Назначение выводов ОМК PIC16F84 55

Окончание таблицы 1 55

Рисунок 3 – Временные диаграммы тактирования и выполнения команд 57

Рисунок 4 – Организация памяти программ и стека 57

Рисунок 5 – Организация памяти данных PIC16F84 58

Таблица 2 – Описание разрядов регистра STATUS 59

Таблица 3 – Описание разрядов регистра OPTION 60

Таблица 4 – Описание разрядов регистра INTCON 61

Рисунок 6 – Загрузка счётчика команд командой, модифицирующей PCL (а) и командами GOTO, CALL (б) 62

Рисунок 7 – Структурная схема таймера 63

Таблица 5 – Описание разрядов регистра CONFIG 63

Рисунок 8 – Схема подключения кварцевого или керамического резонатора 64

Рисунок 9 – Схема внешнего тактирования 64

Рисунок 10 – Схема включения RC-генератора 64

Рисунок 11 – Структурная схема узла сброса 65

Таблица 6 – Общее время запуска микроконтроллера PIC16F84 65

Рисунок 12 – Схема внешнего сброса 66

Рисунок 13 – Логика прерываний 66

Рисунок 14 – Структурная схема сторожевого таймера 67

Рисунок 15 – Форматы команд микроконтроллера PIC16F84 67

Таблица 7 – Система команд микроконтроллера PIC16F84 68

Окончание таблицы 7 69

«ОРГАНИЗАЦИЯ ПАМЯТИ МИКРОПРОЦЕССОРНЫХ СИСТЕМ» 70

Рисунок 1 – Типичные сигналы ЗУ 70

Рисунок 2 – Классификация полупроводниковых ЗУ 70

Рисунок 3 – Структура постоянного ЗУ типа 3D с одноразрядной (а) и многоразрядной организацией (б) 71

Окончание рисунка 3 72

Рисунок 4 – Структура ЗУ типа 2DM для ROM 73

Рисунок 5 – Структура ЗУ типа 2DM для RAM 74

Рисунок 6 – Структура кэш-памяти 74

Рисунок 7 – Структура полностью ассоциативной кэш-памяти 75

Рисунок 8 – Принципиальная электрическая схема ЗЭ на КМОП-транзисторах 76

Рисунок 9 – Схема подключения резервного источника питания к накопителю ЗУ 76

Рисунок 10 – Принципиальная схема ЗЭ динамического ОЗУ 77

Рисунок 11 – Схема включения усилителя-регенератора в разрыв лини записи-считывания динамического ЗУ (а) и вариант схемной реализации усилителя-регенератора (б) 77

Рисунок 12 – Матрица диодных запоминающих элементов масочного ПЗУ 78

Рисунок 13 – Запоминающие элементы с плавкими перемычками (а) и диодными парами (б) 78

Рисунок 14 – Структуры транзисторов типов МНОП (а) и ЛИЗМОП с двойным затвором (б) 79

Рисунок 15 – Схема подключения ЛИЗМОП-транзисторов с двойным затвором к линиям выборки и считывания в РПЗУ 79

Рисунок 16 – Структура матрицы накопителя Флэш-памяти на основе ячеек ИЛИ-НЕ 80

«ИНТЕРФЕЙСНЫЕ БИС/СБИС» 81

Рисунок 17 – Шинный формирователь КР580ВА86. Схема логическая (а) и временные диаграммы работы (б) 81

Окончание рисунка 17 82

Рисунок 18 – Буферный регистр КР580ИР82. Схема логическая (а) и временные диаграммы работы (б) 83

Окончание рисунка 18 84

Таблица 11 – Адресация внутренних регистров ППА и направление передач 85

информации 85

Рисунок 19 – Параллельный периферийный адаптер. Схема электрическая структурная 86

Рисунок 20 – Формат управляющего слова УС1 ППА 87

Рисунок 21 – Формат управляющего слова УС2 ППА 88

Рисунки и таблицы к теме:

«АРИФМЕТИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ»

Таблица 1 – Представление десятичных чисел в позиционных СС

|

D (Decimal notation) |

B (Binary notation) |

H (Hexadecimal notation) |

BCD (Binary-Coded Decimal) |

|

P = 10 |

P = 2 |

P = 16 |

Код 8421 |

|

0 |

0000 |

0 |

0000 |

|

1 |

0001 |

1 |

0001 |

|

2 |

0010 |

2 |

0010 |

|

3 |

0011 |

3 |

0011 |

|

4 |

0100 |

4 |

0100 |

|

5 |

0101 |

5 |

0101 |

|

6 |

0110 |

6 |

0110 |

|

7 |

0111 |

7 |

0111 |

|

8 |

1000 |

8 |

1000 |

|

9 |

1001 |

9 |

1001 |

|

10 |

1010 |

A |

0001 0000 |

|

11 |

1011 |

B |

0001 0001 |

|

12 |

1100 |

C |

0001 0010 |

|

13 |

1101 |

D |

0001 0011 |

|

14 |

1110 |

E |

0001 0100 |

|

15 |

1111 |

F |

0001 0101 |

|

16 |

10000 |

10 |

0001 0110 |

|

17 |

10001 |

11 |

0001 0111 |

Рисунок 1 – Область представляемых чисел с фиксированной точкой

Таблица 2 – Символьный код КОИ-7

|

Код символа в 16-ричной системе счисления |

||||||

|

Младшая цифра |

Старшая цифра |

|||||

|

2 |

3 |

4 |

5 |

6 |

7 |

|

|

0 |

Пробел |

0 |

@ |

P |

Ю |

П |

|

1 |

! |

1 |

A |

Q |

А |

Я |

|

2 |

« |

2 |

B |

R |

Б |

Р |

|

3 |

# |

3 |

C |

S |

Ц |

С |

|

4 |

¤ |

4 |

D |

T |

Д |

Т |

|

5 |

% |

5 |

E |

U |

Е |

У |

|

6 |

|

6 |

F |

V |

Ф |

Ж |

|

7 |

|

7 |

G |

W |

Г |

В |

|

8 |

( |

8 |

H |

X |

Х |

Ь |

|

9 |

) |

9 |

I |

Y |

И |

Ы |

|

A |

|

: |

J |

Z |

Й |

З |

|

B |

+ |

; |

K |

[ |

К |

Ш |

|

C |

, |

< |

L |

\ |

Л |

Э |

|

D |

– |

= |

M |

] |

М |

Щ |

|

E |

. |

> |

N |

|

Н |

Ч |

|

F |

/ |

? |

O |

_ |

О |

Забой |

Рисунки и таблицы к теме:

«ЛОГИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ»

Таблица 3 – Таблица истинности для элементарных логических функций одного аргумента

|

Аргумент X |

Логические функции |

|||

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

Таблица 4 – Таблица истинности для элементарных логических функций двух аргументов

|

Аргументы |

Функции |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

Рисунок 2 –

Реализация элементарных логических

функций одного аргумента

![]() (а) и

(а) и

![]() (б)

(б)

Рисунок 3 –

Реализация элементарной логической

функции

![]() (а) и условное графическое обозначение

повторителя (б и в)

(а) и условное графическое обозначение

повторителя (б и в)

Рисунок 4 –

Реализация элементарной логической

функции

![]() (а) и условное графическое обозначение

инвертора (б и в)

(а) и условное графическое обозначение

инвертора (б и в)

|

Таблица 5 – Полная совокупность элементарных логических функций двух аргументов

|

Условное графическое обозначение |

международное |

10 |

|

Генератор нуля |

|

Конъюнктор (ЛЭ И) |

|

|

по ГОСТ 2.743‑91 ЕСКД |

9 |

|

|

|||||

|

Наименование функции |

8 |

Константа нуль (функция 0) |

Конъюнкция (логическая операция И) |

|||||

|

Запись функции |

с помощью самостоятельной нотации |

7 |

|

|

||||

|

в основном базисе (И, ИЛИ, НЕ) |

6 |

|

|

|||||

|

Значения истинности аргументов и функций |

1 |

1 |

5 |

0 |

1 |

|||

|

1 |

0 |

4 |

0 |

0 |

||||

|

0 |

1 |

3 |

0 |

0 |

||||

|

0 |

0 |

2 |

0 |

0 |

||||

|

Логические аргументы и функции |

аргумент

|

аргумент

|

1 |

Функция

|

Функция

|

|||

|

Продолжение таблицы 5

|

10 |

|

Элемент запрета (ЛЭ НЕТ) |

|

Повторитель |

|

Элемент запрета (ЛЭ НЕТ) |

|

Повторитель |

|

9 |

|

|

|

|

|||||

|

8 |

Запрет первого аргумента (логическая операция НЕТ) |

Повторение первого аргумента (логическая операция ДА) |

Запрет второго аргумента (логическая операция НЕТ) |

Повторение второго аргумента (логическая операция ДА) |

|||||

|

7 |

|

|

|

|

|||||

|

6 |

|

|

|

|

|||||

|

5 |

0 |

1 |

0 |

1 |

|||||

|

4 |

1 |

1 |

0 |

0 |

|||||

|

3 |

0 |

0 |

1 |

1 |

|||||

|

2 |

0 |

0 |

0 |

0 |

|||||

|

1 |

Функция

|

Функция

|

Функция

|

Функция

|

|||||