Рисунки к конспектам (11.10.10)

.doc

|

Продолжение таблицы 5

|

10 |

|

Сумматор по модулю 2 (ЛЭ Исключающее ИЛИ) |

|

Дизъюнктор (ЛЭ ИЛИ) |

|

Элемент Пирса (ЛЭ ИЛИ-НЕ) |

|

Эквивалентор (ЛЭ Исключающее ИЛИ-НЕ) |

|

9 |

|

|

|

|

|||||

|

8 |

Неравнозначность, сложение по модулю 2 (логическая операция Исключающее ИЛИ) |

Дизъюнкция (логическая операция ИЛИ) |

Отрицание дизъюнкции (стрелка Пирса), логическая операция ИЛИ-НЕ |

Равнозначность, сложение по модулю 2 с отрицанием (логическая операция Исключающее ИЛИ-НЕ) |

|||||

|

7 |

|

|

|

|

|||||

|

6 |

|

|

|

|

|||||

|

5 |

0 |

1 |

0 |

1 |

|||||

|

4 |

1 |

1 |

0 |

0 |

|||||

|

3 |

1 |

1 |

0 |

0 |

|||||

|

2 |

0 |

0 |

1 |

1 |

|||||

|

1 |

Функция

|

Функция

|

Функция

|

Функция

|

|||||

|

Продолжение таблицы 5

|

10 |

|

Инвертор (ЛЭ НЕ) |

|

Импликатор |

|

Инвертор (ЛЭ НЕ) |

|

Импликатор |

|

9 |

|

|

|

|

|||||

|

8 |

Отрицание второго аргумента (логическая операция НЕ) |

Импликация

от

|

Отрицание первого аргумента (логическая операция НЕ) |

Импликация

от

|

|||||

|

7 |

|

|

|

|

|||||

|

6 |

|

|

|

|

|||||

|

5 |

0 |

1 |

0 |

1 |

|||||

|

4 |

1 |

1 |

0 |

0 |

|||||

|

3 |

0 |

0 |

1 |

1 |

|||||

|

2 |

1 |

1 |

1 |

1 |

|||||

|

1 |

Функция

|

Функция

|

Функция

|

Функция

|

|||||

|

Окончание таблицы 5

|

10 |

|

Элемент Шеффера (ЛЭ И-НЕ) |

|

Генератор единицы |

|

9 |

|

|

|||

|

8 |

Отрицание конъюнкции (штрих Шеффера, логическая операция И-НЕ) |

Константа единица (логическая операция 1) |

|||

|

7 |

|

|

|||

|

6 |

|

|

|||

|

5 |

0 |

1 |

|||

|

4 |

1 |

1 |

|||

|

3 |

1 |

1 |

|||

|

2 |

1 |

1 |

|||

|

1 |

Функция

|

Функция

|

|||

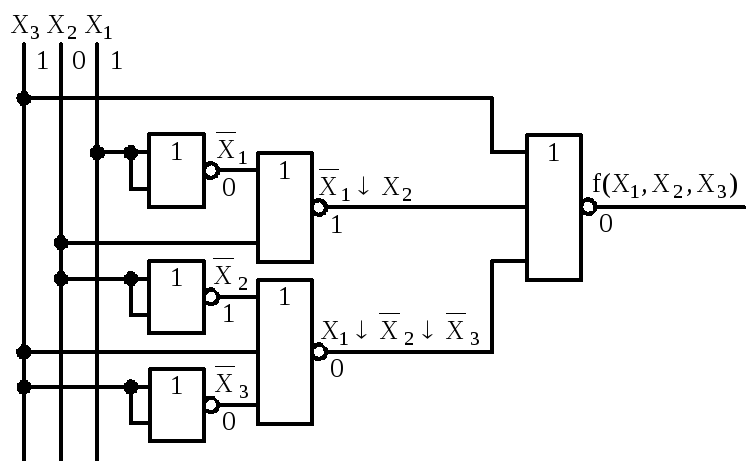

Рисунок 5 – Логическая схема устройства

Рисунок 6 – Реализация на основе логических элементов И‑НЕ логических элементов НЕ (а) и И (б)

Рисунок 7 – Реализация на основе логических элементов ИЛИ‑НЕ логических элементов НЕ (а) и ИЛИ (б)

Рисунок 8 – Логическая схема устройства в базисе И-НЕ

Рисунок 9 – Логическая схема устройства в базисе ИЛИ-НЕ

Рисунки и таблицы к теме:

«СХЕМОТЕХНИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ»

Рисунок 10 – Временные диаграммы физического представления кодового слова 10110 потенциальным способом (а), импульсным (б) и динамическим (в)

Рисунок 11 – Условное обозначение микросхемы 1533ЛА3

Таблица 6 – Обозначение цифровых ИС для подгруппы логических элементов

|

Подгруппа и вид ИС |

Обозначение |

|

Логические элементы: |

|

|

И-НЕ |

ЛА |

|

И-НЕ/ИЛИ-НЕ |

ЛБ |

|

расширители |

ЛД |

|

ИЛИ-НЕ |

ЛЕ |

|

И |

ЛИ |

|

И-ИЛИ-НЕ/И-ИЛИ |

ЛК |

|

ИЛИ |

ЛЛ |

|

ИЛИ-НЕ/ИЛИ |

ЛМ |

|

НЕ |

ЛН |

|

прочие |

ЛП |

|

И-ИЛИ-НЕ |

ЛР |

|

И-ИЛИ |

ЛС |

Примечание – символ «E» означает расширительный выход (вход).

Рисунок 12 – Условное графическое обозначение расширителя (а), логического элемента 2И-2ИЛИ-НЕ/2И-2ИЛИ с возможностью расширения по ИЛИ (б) и логического элемента 3ИЛИ-НЕ/3ИЛИ (в)

Рисунок 13 – Направление выходных и входных токов при высоком уровне выходного напряжения (а) и низком уровне – (б)

Окончание рисунка 13

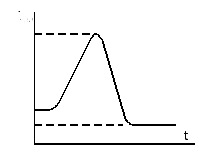

Рисунок 14 – Типовая передаточная характеристика инвертора

Рисунок 15 – Временные диаграммы входного и выходного напряжений при переключении инвертирующего логического элемента

Рисунок 16 – Схемы логических выходов цифровых элементов схемотехники ТТЛШ (а) и КМОП (б)

Рисунок 17 – Временная диаграмма тока, потребляемого цифровым элементом при переключении из одного логического состояния в другое

Рисунок 18 – Инвертор схемотехники КМОП с тремя состояниями выхода. Принципиальная схема (а) и условное графическое обозначение (б)

Рисунок 19 – Схемы выходов цифровых элементов с открытым коллектором (стоком) схемотехники ТТЛШ (а) и схемотехники КМОП (б)

Рисунок 20 – Схема реализации монтажной логики (а) и индикации уровня логической единицы (б) и уровня логического нуля (в) с помощью логических элементов с открытым коллектором (стоком)

Рисунок 21 – Схема наращивания числа входов для логических элементов И (а) и ИЛИ (б)

Рисунок 22 – Схема наращивания числа входов для логических элементов И-НЕ (а) и ИЛИ-НЕ (б)

Рисунок 23 – Схема снижения нагрузки на выходах логических элементов с помощью буферных элементов (а) и путем разделения нагрузки (б)

Примечание – «![]() »

– выходное сопротивление источника

сигнала

»

– выходное сопротивление источника

сигнала

Рисунок 24 – Схема входной цепи элемента схемотехники КМОП с подтягивающим (а) и заземляющим (б) резисторами

Окончание рисунка 24

Рисунки и таблицы к теме:

«АНАЛИЗ И СИНТЕЗ КЦУ»

Таблица 7 – Таблица истинности для логической функции трех аргументов

|

Номер набора |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

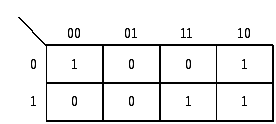

Рисунок 25 – Карты Карно для логических функций трех (а) и четырех (б) аргументов

Таблица 8 – Таблица истинности для логической функции трех аргументов

|

Номер набора |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

Рисунок 26 – Карта Карно для логической функции трех аргументов, функционирование которой задано таблицей 8

Рисунок 27 – Карта Карно и результат минимизации к примеру 1

Рисунок 28 – Карта Карно и результат минимизации к примеру 2

Рисунок 29 – Карта Карно и результат минимизации к примеру 3

Рисунок 30 – Карта Карно и результат минимизации к примеру 4

Рисунок 31 – Карта Карно и результат минимизации к примеру 5

Рисунок 32 – Карта Карно и результат минимизации к примеру 6

Рисунок 33 – Карта Карно для не полностью заданной логической функции

Рисунок 34 – Варианты минимизации не полностью заданной логической функции

Окончание рисунка 34

Рисунки к теме:

«ОБЩИЕ СВЕДЕНИЯ О МИКРОПРОЦЕССОРАХ»

Рисунок 1 – Классификация МП БИС

Рисунок 2 – Общая структурная схема микропроцессора

Рисунок 3 – Структурная схема МП со схемной логикой управления

Рисунок 4 – Структурная схема МП с программируемой логикой управления

Рисунок 5 – Структурная схема УУ МП с программируемой логикой управления

Рисунок 6 – Временная диаграмма работы МП

Рисунок 7 – Структура микропроцессорной системы

Рисунки и таблицы к теме:

«ПРИНЦИПЫ ОРГАНИЗАЦИИ МПС НА ОСНОВЕ ОДНОКРИСТАЛЬНОГО МИКРОПРОЦЕССОРА»

Рисунок 1 – Структура микропроцессора К1821ВМ85А

Таблица 1 – Значения сигналов состояния и управления для различных машинных циклов

|

Тип МЦ |

Сигналы состояния |

Сигналы управления |

|||||

|

|

S1 |

S0 |

|

|

|

||

|

OF |

0 |

1 |

1 |

0 |

1 |

1 |

|

|

MR |

0 |

1 |

0 |

0 |

1 |

1 |

|

|

MW |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

IOR |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

IOW |

1 |

0 |

1 |

1 |

0 |

1 |

|

|

INA |

1 |

1 |

1 |

1 |

1 |

0 |

|

|

BI |

TC |

|

|

1 |

1 |

1 |

|

|

HALT |

TC |

0 |

0 |

TC |

TC |

1 |

|

|

Примечание – TC – третье состояние |

|||||||

Рисунок 2 – Внешние элементы тактового генератора (а) и формирование синхросигналов (б) в микропроцессоре К1821ВМ85А

|

КЦ |

|

b1 |

N – 2 |

|||||||||

|

М1 |

М2 |

М3 |

|

b2 |

N – 1 |

|||||||

|

Т1 |

Т2 |

Т3 |

Т4 |

Т1 |

Т2 |

Т3 |

Т1 |

Т2 |

Т3 |

|

b3 |

N |

|

а) |

|

б) |

|

|||||||||