Рисунки к конспектам (11.10.10)

.doc

Рисунок 8 – Принципиальная электрическая схема ЗЭ на КМОП-транзисторах

Рисунок 9 – Схема подключения резервного источника питания к накопителю ЗУ

Рисунок 10 – Принципиальная схема ЗЭ динамического ОЗУ

Рисунок 11 – Схема включения усилителя-регенератора в разрыв лини записи-считывания динамического ЗУ (а) и вариант схемной реализации усилителя-регенератора (б)

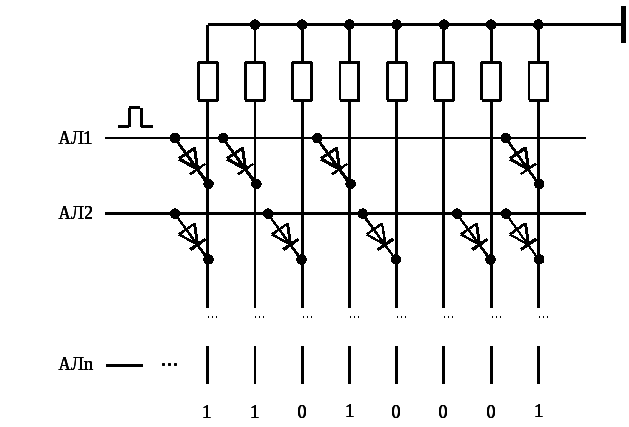

Рисунок 12 – Матрица диодных запоминающих элементов масочного ПЗУ

Рисунок 13 – Запоминающие элементы с плавкими перемычками (а) и диодными парами (б)

Рисунок 14 – Структуры транзисторов типов МНОП (а) и ЛИЗМОП с двойным затвором (б)

Рисунок 15 – Схема подключения ЛИЗМОП-транзисторов с двойным затвором к линиям выборки и считывания в РПЗУ

Рисунок 16 – Структура матрицы накопителя Флэш-памяти на основе ячеек ИЛИ-НЕ

Рисунки и таблицы к теме:

«ИНТЕРФЕЙСНЫЕ БИС/СБИС»

Рисунок 17 – Шинный формирователь КР580ВА86. Схема логическая (а) и временные диаграммы работы (б)

t1 – задержка распространения сигналов от входов к выходам;

t2 – задержка перехода выходов в Z-состояние;

t3 – задержка перехода выходов в активное состояние;

t4

и t5

– время выдержки и предустановки сигнала

T

относительно сигнала

![]() .

.

б)

Окончание рисунка 17

Рисунок 18 – Буферный регистр КР580ИР82. Схема логическая (а) и временные диаграммы работы (б)

t1 – задержка распространения сигналов от входов к выходам;

t2 – задержка перехода выходов в Z-состояние;

t3 – задержка перехода в активное состояние;

t4 – интервал от изменения строба до изменения выхода схемы;

t5

и t6

– времена предустановки и выдержки

входного сигнала относительно

спада строба

![]()

б)

Окончание рисунка 18

Таблица 11 – Адресация внутренних регистров ППА и направление передач

информации

|

A1 |

A0 |

|

|

|

Операция |

|

0 |

0 |

0 |

1 |

0 |

Порт A → Системная ШД |

|

0 |

1 |

0 |

1 |

0 |

Порт B → Системная ШД |

|

1 |

0 |

0 |

1 |

0 |

Порт C → Системная ШД |

|

1 |

1 |

0 |

1 |

0 |

Запрещенная комбинация |

|

0 |

0 |

1 |

0 |

0 |

Системная ШД → Порт A |

|

0 |

1 |

1 |

0 |

0 |

Системная ШД → Порт B |

|

1 |

0 |

1 |

0 |

0 |

Системная ШД → Порт C |

|

1 |

1 |

1 |

0 |

0 |

Системная ШД → РУС при D7 = 1 |

|

|

|

|

|

|

Системная ШД → BSR при D7 = 0 |

|

X |

X |

1 |

1 |

0 |

Шины отключены (Z-состояние) |

|

X |

X |

X |

X |

1 |

Шины отключены (Z-состояние) |

|

Примечание – Знак «X» означает произвольный уровень сигнала (0 или 1) |

|||||

Рисунок 19 – Параллельный периферийный адаптер. Схема электрическая структурная

Рисунок 20 – Формат управляющего слова УС1 ППА

Пример – Составим программу ввода данных из порта A и вывода в порты B и C.

|

Программирование ППА |

MVI A, 90 H |

; загрузка УС1 в регистр А МП (90 H – код УС1) |

|

OUT 83 H |

; загрузка УС1 в РУС ППА (83 H – адрес РУС) |

|

|

Ввод-вывод данных |

IN 80 H |

; ввод данных из порта A (80 H – адрес порта A) |

|

OUT 81 H |

; вывод данных из порта B (81 H – адрес порта B) |

|

|

OUT 82 H |

; вывод данных из порта C (82 H – адрес порта C) |

Рисунок 21 – Формат управляющего слова УС2 ППА

Например, для установки разрядов D0 и D2 порта C в единичное состояние необходимо выполнить следующую последовательность команд:

|

MVI A, 01 H |

; загрузка УС 2 в регистр A МП (01 H – код УС2) |

|

OUT 83 H |

; загрузка команды BSR (83 H – адрес команды) |

|

MVI A, 05 H |

; загрузка УС 2 в регистр A МП (05 H – код УС2) |

|

OUT 83 H |

; загрузка команды BSR (83 H – адрес команды) |